Goddard

# NATIONAL AERONAUTICS AND SPACE ADMINISTRATION WASHINGTON, D.C. 20546

USI/Scientific & Technical Information Division

REPLY TO ATTN OF: GP

| - At                                                          | tention: Miss                                                                                | Winnie M. Morgan                                                                                                                                                       |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                               | /Office of Assistent Matters                                                                 | stant General Counsel for                                                                                                                                              |

| SUBJECT: An                                                   | nouncement of N                                                                              | ASA-Owned U. S. Patents in STAR                                                                                                                                        |

| and Code USI                                                  | , the attached                                                                               | edures agreed upon by Code GP<br>NASA-owned U. S. Patent is being<br>and announcement in NASA STAR.                                                                    |

| The following                                                 | ng information i                                                                             | s provided:                                                                                                                                                            |

| U. S. I                                                       | Patent No.                                                                                   | : 3,588,483                                                                                                                                                            |

|                                                               | ment or<br>ate Employee                                                                      | : U.S. Government                                                                                                                                                      |

|                                                               | mentary Corporat<br>(if applicable)                                                          | · NA                                                                                                                                                                   |

| NASA Pa                                                       | atent Case No.                                                                               | : GSC-10186                                                                                                                                                            |

|                                                               |                                                                                              | tor, the following is applicable:                                                                                                                                      |

| Space Act, the first painventor (at the Specific an invention | Section 305(a)<br>the name of the<br>age of the paten<br>author) appears<br>cation, followin | of the National Aeronautics and Administrator of NASA appears on it; however, the name of the actual at the heading of Column No. 1 of ing the words " with respect to |

| Elizabeth A<br>Enclosure                                      | . Carter                                                                                     | N71-33110  (ACCESSION NUMBER)  (PAGES)  (NASA CR OR TMX OR AD NUMBER)  (CATEGORY)                                                                                      |

|                                                               |                                                                                              |                                                                                                                                                                        |

| [72]  | Inventor            | Robert J. L.<br>Greenbelt, I |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                     |

|-------|---------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|

| 1211  | Appl. No.           | 713,188                      | V & V.S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                     |

|       | Filed               | Mar. 14, 19                  | 830                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                     |

| [1    | Patented            | June 28, 19                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                     |

|       | Assignee            | The United<br>by the Adm     | States of Amer<br>inistrator of the<br>s and Space Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e Nation | al                  |

|       |                     | -                            | THE RESIDENCE OF THE PARTY OF T |          |                     |

| [54]  | REGISTE<br>IN EITHE |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                     |

| [52]  | U.S. Cl             |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 235/175,<br>235/164 |

| [51]  | Int Cl              |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | G06f 7/50           |

| 1501  |                     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 235/175,            |

| [50]  |                     |                              | 307/221, 216,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                     |

| [56]  |                     | Referen                      | nces Cited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                     |

|       | J                   | UNITED STA                   | TES PATENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rs       |                     |

| 3,239 | ,764 3/1            | 966 Verma                    | et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 235/156X            |

| 3.375,358 | 3/1968  | Franck        | 235/175  |

|-----------|---------|---------------|----------|

| 3,454,310 | 7/1969  | Wilhelm, Jr.  | 235/152X |

| 3,374,468 | 3/1968  | Muir          | 235/164X |

| 3,320,410 | 5/1967  | Barrett et al | 235/175  |

| 3,348,069 | 10/1967 | Petschaver    | 307/221  |

| 3,462,589 | 8/1969  | Robertson     | 235/175X |

| 3,480,259 | 9/1968  | Maczko et al  | 235/175X |

Primary Examiner—Malcolm A. Morrison Assistant Examiner—David H. Malzahn Attorneys—R. F. Kempf, E. Levy and G. T. McCoy

ABSTRACT: Disclosed is a data processor including a plurality of cascaded registers connected together to selectively perform left and right shifts, as well as right rotation. The register stages are selectively connected to feed and be responsive to a single data line at either end thereof. The register stages are selectively connected with parallel data lines to be responsive to signals on the data lines. Words stored in the register can be combined with words on the parallel data lines in accordance with logical functions such as AND, OR, EXCLUSIVE OR, ADDITION, and SUBTRACTION. The register stages can also combine signals from one of the serial data lines with signals stored therein and from the parallel data lines.

SHEET 1 OF 3

BY

SHEET 3 OF 3

# VARIABLE DIGITAL PROCESSOR INCLUDING A REGISTER FOR SHIFTING AND ROTATING BITS IN EITHER DIRECTION

The invention described herein was made by an employee of the United States Government and may be manufactured and used by or for the Government for governmental purposes without the payment of any royalties thereon or therefor.

The present invention relates to data processors, and more particularly to a data processor including a plurality of register stages which are selectively interconnected with each other to 10 effect a multiplicity of operations.

With the advent of large scale integrated circuits, it has become feasible to perform multiple operations which heretofore have been considered impractical because of power and

space requirements. With discrete and individual integrated 15

circuits, it has generally been the practice to interconnect

computer elements in a relatively rigid manner wherein the

number of possible functions that could be achieved was

limited.

In accordance with the present invention, a plurality of re- 20 gister stages are interconnected with each other and serial data sources connected to the least and most significant stages to effect transfer of data in either direction and rotation thereof at will. Data are transferred to and from the register to lines connected to the least and most significant bit stages to 25 reduce the number of external leads to the system.

According to another embodiment of the invention, words expressed as parallel bits are combined with words stored in the register stages in accordance with a plurality of different operating instructions, viz., logical AND, logical OR, EXCLU-SIVE OR, add, subtract the register word from the word on the lines, subtract the word on the lines from the register word, and load the external word into the register. In addition, the register stages can be cleared to zero or set to one at will, and the lowest order stage is selectively responsive to serial 35 data bits, as well as the parallel data bits. The most significant bit stage is selectively coupled to a serial data line or to an overflow indicator.

Preferably, the entire data processor comprises a large scale integrated circuit that may be mounted on a single chip to 40 conserve space and power.

A further feature of the invention is that the parallel data lines can at will either feed bits into the register or be responsive to words stored in the register. Also, the logic between stages is established so that negative number operations are 45 performed in the two's complement binary arithmetic.

It is, accordingly, an object of the present invention to provide a new and improved data processor having capability for multiple connections between a plurality of register stages.

An additional object of the present invention is to provide a 50 data processor capable of performing multiple operations on parallel words; such operations being, for example, addition, subtraction, logical AND, logical OR, logical EXCLUSIVE OR, and one's and two's complementing.

A further object of the present invention is to provide a data processor including a plurality of register stages, the operation of which can be altered at will to enable left and right shifts, as well as feedback.

A further object of the present invention is to provide a data processor wherein serial and parallel data words can be fed 60 into and derived from the computer on the same leads.

The above and still further objects, features and advantages of the present invention will become apparent upon consideration of the following detailed description of one specific embodiment thereof, especially when taken in conjunction 65 with the accompanying drawings, wherein:

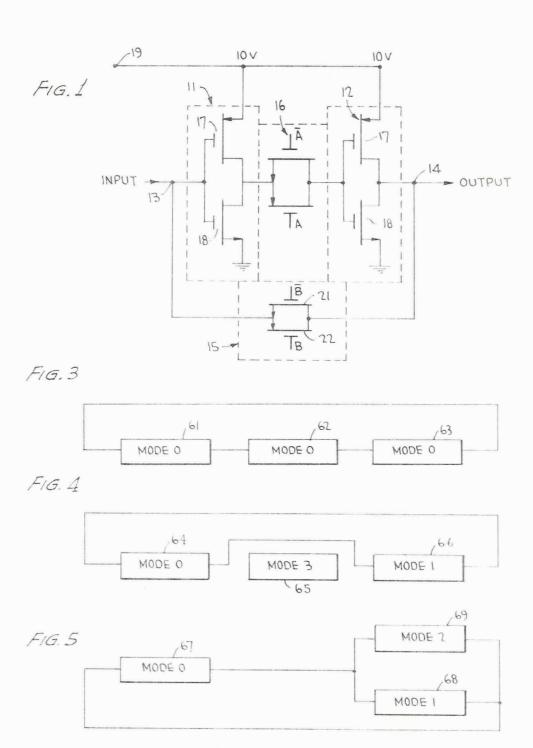

FIG. 1 is a circuit diagram of a preferred network for a single register stage;

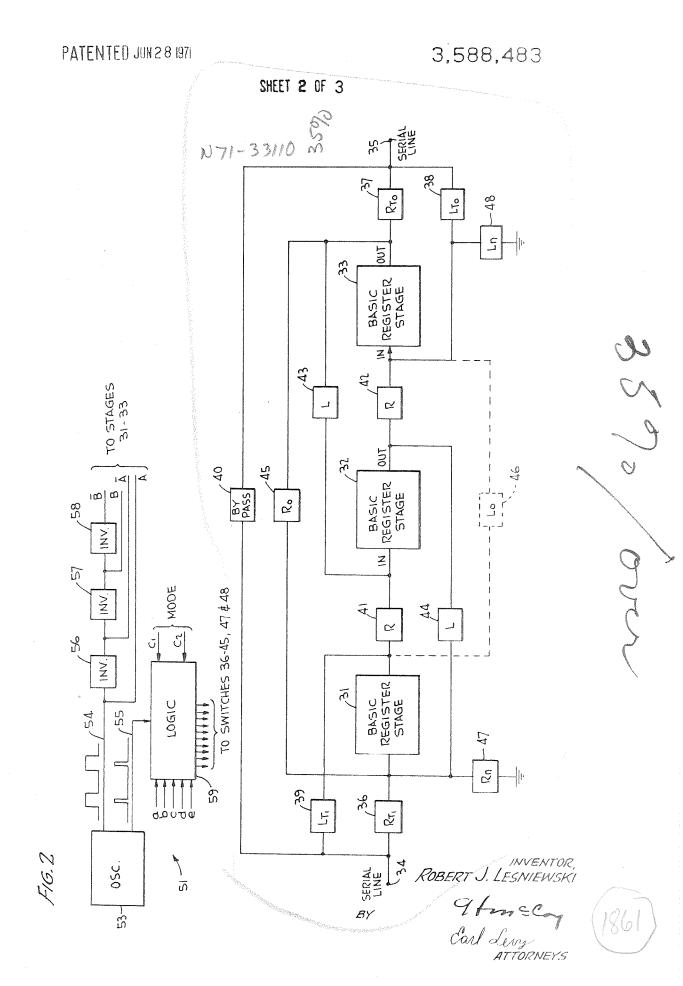

FIG. 2 is a block diagram of a serial register in accordance with one embodiment of the present invention;

FIGS. 3, 4 and 5 are block diagrams illustrating the manner by which several registers of the type illustrated by FIG. 2 may be interconnected; and

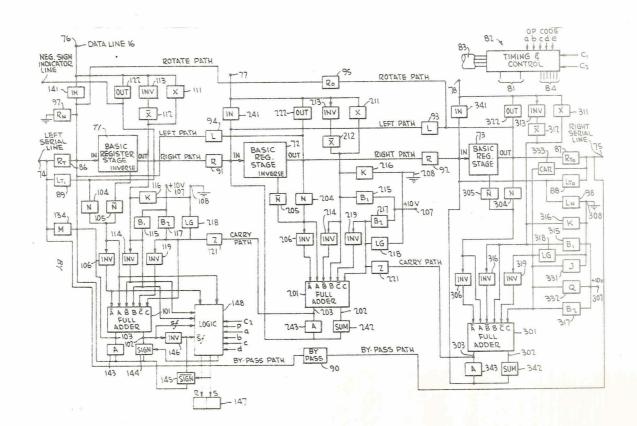

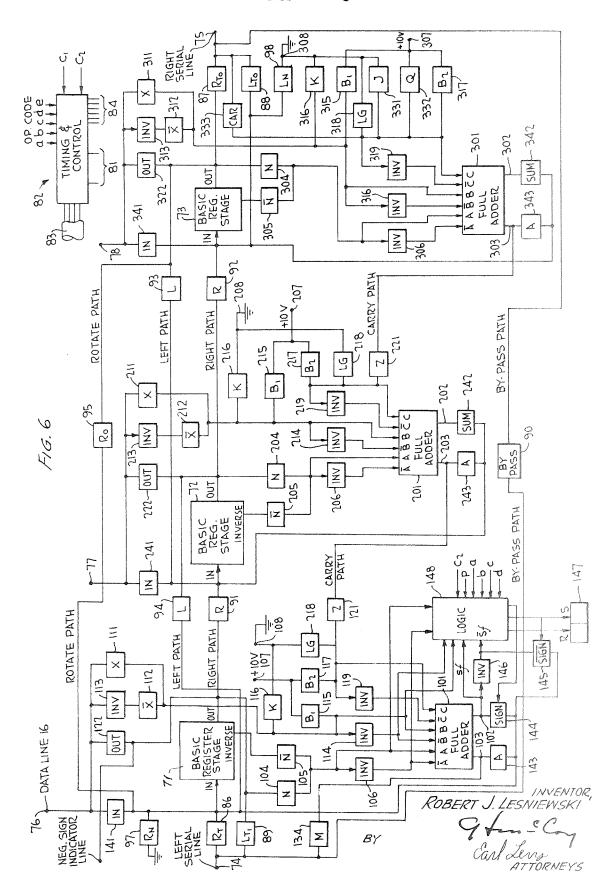

FIG. 6 is a block diagram illustrating an embodiment of a parallel processor according to the present invention.

Prior to considering the apparatus of the present invention, consideration will be given to the circuitry comprising a basic shift register stage, by referring to FIG. 1 of the drawings. The basic shift register stage of FIG. 1 comprises, in essence, a pair of inverters, each having inherent memory provision, and separated by a pair of normally closed switches. The basic shift register stage is described in conjunction with metal oxide semiconductor field effect transistors (MOSFET's) formed as large scale integrated circuit components on a chip; it is to be understood, however, that other suitable devices may be utilized in lieu of MOSFET's and integrated circuit chips.

The basic register stage comprises inverter sections 11 and 12, the former having an input responsive to binary signals at terminal 13 and the latter deriving a binary output at terminal 14. Input and output terminals 13 and 14 are selectively connected together by normally closed switch 15, while stages 11 and 12 are selectively connected to each other by normally closed switch 16.

Each of inverters 11 and 12 includes a pair of opposite conductivity type MOSFET's 17 and 18, having the source drain paths thereof connected in series between a positive, 10-volt source at terminal 19 and ground. The gate electrodes of MOSFET's 17 and 18 are connected together and to the input terminal of the inverter, whereby only one of MOSFET's 17 or 18 is forward biased at any time. Hence, only one of the MOSFET's 17 or 18 has the source drain path thereof activated to a relatively low impedance state, while the source drain path of the other MOSFET is virtually open circuited. Because of the relatively large MOSFET gate source capacitance, MOSFET's 17 and 18 include capacitive memories and store charge upon the removal of a voltage source from the gate electrodes.

Switches 15 and 16 comprise an additional pair of MOSFET's 21 and 22, having their source electrodes connected together and their drain electrodes similarly connected. The gate electrodes of MOSFET's 21 and 22 are responsive to complementary voltages, whereby both active elements comprising the switch are simultaneously open- and short-circuited.

In normal operation, with the transistors comprising switches 15 and 16 driven to the closed state, a regenerative path is established between terminals 13 and 14 since the output voltage of stage 11 is of an opposite sense from the voltage at terminal 13. The voltage at the output of stage 11 is coupled to the input of stage 12 via switch 16, whereby the voltage at terminal 14 is of the same polarity as the voltage at terminal 13. The voltage at terminal 14 is coupled back to terminal 13 through closed switch 15 to establish the regenerative feedback path.

To consider a specific example of the register stage operation, assume that terminal 13 has applied thereto a voltage equal to the voltage at terminal 19 whereby a low impedance source drain path subsists in transistor 18, while the source drain path of MOSFET 17 is virtually an open circuit. In consequence, a ground voltage is coupled to the drain electrode of MOSFET 18 and fed through closed switch 16 to the gate electrodes of stage 12. In response to the ground potential applied to the gate electrodes of stage 12, the source drain path of MOSFET 17 of stage 12 is virtually short-circuited, while the source drain path of MOSFET 18 is open-circuited. Thereby, the 10-volt source at terminal 19 is coupled through MOSFET 17 of inverter 12 to output terminal 14 to form the regenerative loop. The regenerative loop continues to provide a positive voltage at terminal 14 even though a source coupling a positive voltage to terminal 13 is decoupled from the register stage of FIG. 1. The positive voltage is derived at terminal 14 until terminal 13 is connected to a binary zero indicating ground potential, while switches 15 and 16 are opencircuited.

Because of the relatively large source gate capacity of MOSFET's 17 and 18, inverter stages 11 and 12 remain in the same state as they were previously driven even when no driving voltage is at terminal 13 and switches 15 and 16 are open-

circuited. Thereby, the basic register stage illustrated has an inherent memory capacity, sufficient to enable the voltage at terminal 14 to remain relatively constant during the occurrence of switching operations which would open circuit switches 15 and 16 and decouple terminal 13 from external 5 voltage sources.

The manner by which the basic shift register stage of FIG. 1 is employed in a complete large scale integrated circuit shift register capable of being activated to four different operating modes is indicated by the circuit diagram of FIG. 2, to which reference is now made. The shift register illustrated by FIG. 2, for purposes of simplicity, comprises three stages 31, 32 and 33, although in actual practice the number of stages is generally considerably in excess of three, usually being on the order of 16.

The shift register stages 31-33 can be selectively connected to feed or be responsive to binary bits on external serial data lines 34 and 35 in accordance with four different modes,

Mode 0. Shifting data in either direction from and into terminals 34 and 35:

Mode 1. Shifting data into and from terminal 34 at the left end of the register without feeding data into and/or from

Mode 2. Shifting data into and out of terminal 35 at the right end of the register without feeding data into and/or from terminal 34; and

Mode 3. Bypassing all of stages 31-33, whereby terminals 34 and 35 are directly connected.

The several stages 31-33 comprising the entire register can be connected together whereby data are shifted left or right. In the shifting operations, binary bits at the highest and lowest order stages, 31 and 33, respectively, are selectively fed to serial data lines 34 or 35 or decoupled from the remainder of 35 the network. In addition to the shifting instruction or operation, register stages 31-33 can be connected in a feedback loop so that data are rotated either in the right or left direction. For left rotation, shift register stages 31-33 are interconnected so that binary bits propagate from register 33 to 40 register 32 to register 31 and back to register 33. For right rotation, the opposite direction of data flow occurs between stages 31-33.

The four modes stated supra are established by selectively closing switches between lines 34 and 35 and the input and 45 output terminals of register stages 31-33 (the input and output terminals are always respectively shown on left and right sides of the stages). In addition, the mode connections are provided by selectively grounding the input and output of stages 31 and 33 by closing switches. In particular, mode 0 50 operation involving shifting or rotating in the right direction is established by closing switches 36 and 37, respectively connected between line 34 and the input of highest order stage 31 and between the output of lowest order stage 33 and line 35. Left shift and rotate connections for mode 0 operation are established by closing switches 38 and 39, respectively connected between line 35 and the input of stage 33 and between the output of stage 31 and line 34. Mode 3 operation, wherein terminals 34 and 35 are directly connected together and the 60 stages 31-33 are isolated therefrom, is established by closing switch 40 connected between terminals 34 and 35.

Selective opening and closing of switches 36-40 establishes the four different operating modes indicated relative to external lines 34 and 35. To selectively couple data 65 between the various shift register stages 31-33 for left and right shifts, as well as rotations regardless of the mode configuration, the register stages are interconnected with each other via normally open-circuited series switches 41-46. Switches 41 and 42 are respectively connected between the output and 70 input terminals of stages 31 and 32 and between the output and input terminals of stages 32 and 33 to enable the propagation of binary bits in the right-hand direction for either shifting or rotation operations. In contrast, switch 43 selectively connects the output terminal of stage 33 with the input terminal of 75 mode 1, switches 36, 39 and 48 are selectively energized; in

stage 32, while switch 44 is connected between the output and input terminals of stages 32 and 31, respectively. To perform right-hand rotation, the output terminal of stage 33 is connected with the input terminal of stage 31 via switch 45, while left-hand rotation is selectively established through switch 46, connected between the input and output terminals of stages 33 and 31, respectively.

For a left shift operation in modes 1 and 3, wherein data line 35 is isolated from register stages 31-33, a binary zero is fed to the input of least significant bit stage 33 by closing switch 48, connected between the input of stage 33 and ground. For right shift operations in modes 2 and 3, wherein data line 34 is decoupled from the internal register circuitry, a binary zero is fed to the input of stage 31 by closing switch 47, connected between the input of the left stage and ground.

Control of the various switches interconnecting stages 31--33 with each other and external lines 34 and 35 is in response to timing pulses derived from timing and control source 51. Timing and control source 51 includes oscillator 52 that derives on leads 53 and 54 a pair of relatively low duty cycle rectangular waves having the same frequency and identical center of occurrence times. The rectangular wave on lead 54 is designed to have a duty cycle slightly greater than the duty cycle of the wave derived on lead 55 because the voltage on the former lead controls switching within each of stages 31--33 while the signal on lead 55 controls the switches external to the register stages.

The wave on lead 54 is coupled through three cascaded in-30 verters 56-58, each identical to the inverters included within register stages 31-33. Thereby, each of the opposite polarity voltages derived at the inputs and outputs of inverters 56-58 has a propagation delay equal to the propagation delay of each inverter stage within register stages 31-33. The inputs to inverters 56, 57 and 58 are respectively applied as the complementary input signal pairs to switches 16 and 15, whereby inverters 11 and 12 in each register stage are decoupled in response to the positive portion of the wavetrain on lead \$4 in synchronism with decoupling of the inverter stages in the register stages.

The short duration pulses derived on lead 55 by oscillator 53 are coupled as timing signals to logic network 59. Logic network 59 responds to the timing pulses and a pair of command signals, C1 and C2, indicative of the register mode configuration. In addition, logic network 59 responds to five binary signals, a-e, indicative of operating connections for the register comprising stages 31-33. The operating code signals a-e and the mode signals  $C_1$  and  $C_2$  are combined with the short duration pulses on lead 55 for selective activation of switches 36-45, 47 and 48 only while a pulse is being derived on lead 55. A pulse is derived on lead 55 only while the inverters in register stages 31-33 are decoupled from each other. No output signal is derived from logic network 59 to control activation of switch 46 because, in an actual preferred embodiment of the register, there is usually no need to employ switch 46 as left rotate is, to a certain extent, a redundant function of right rotate.

Logic network \$9 responds to the C, and C2 inputs to control the complete register into a selected mode in accordance

| TABLE I |                |                  |

|---------|----------------|------------------|

| Mode    | C <sub>2</sub> | Ci               |

| 0       | 0<br>0<br>1    | 0<br>1<br>0<br>1 |

From Table I, it is appreciated that each mode number corresponds with the binary equivalent for the particular number. In mode 0, generally switches connected to data lines 34 and 35, namely switches 36-39, are selectively energized; in

6

mode 2, switches 37, 38 and 47 are selectively energized; and in mode 3, switches 47 and 48 are selectively energized, while switch 40 is always energized.

In addition to controlling the mode connections of the switches which selectively couple data between lines 34 and 5 35 and the register stages between them, logic circuit 59 responds to the operation code signals a-e to control opening and closing of switches 41-45 independently of the mode signals  $C_1$  and  $C_2$ .

A complete analysis of the circuit configurations established between register stages 31-33 and data lines 34 and 35 is indicated by Table II:

each other. After each of switches 15 and 16 in register stages 31—33 has been open-circuited, the second pulse on lead 55 is derived to close switches 38, 43, 44 and 39 again. The binary one signal stored in inverter 12 of register stage 33 is now coupled to inverter 11 of register 32 via switch 43. Inverter 11 changes state from the zero previously loaded therein to one in response to the signal coupled to it through switch 43 because the inverter input is isolated from any other signal source. Simultaneously, inverter 11 in stage 33 is responsive to the binary one signal on lead 35 and thereby remains in the binary one state. Upon completion of the second pulse on lead 55, each of switches 38, 43, 44 and 39 is again open-circuited

TABLE II

| M9M/W/A-Ja-ourus |   | Op code Mode Mode d |   |   |    |    |     |       |           |           | deper | ndent s | Mode<br>independent<br>switch |    |         |    |   |

|------------------|---|---------------------|---|---|----|----|-----|-------|-----------|-----------|-------|---------|-------------------------------|----|---------|----|---|

|                  | a | b                   | С | d | e  | Ć٤ | Cı  | $R_n$ | $R_{T_1}$ | $L\tau_1$ | BY    | RTo     | LTo                           | Ln | $R_{o}$ | R  | L |

| L                | 1 | 1                   | 0 | 1 | D  | 0  | 0   | 0     | 0         | 1         | 0     | 0       | 1                             | 0  | 0       | 0  | 1 |

| L                | 1 | 1                   | 0 | 1 | D  | 0  | 1   | 0     | 0         | 1         | 0     | 0       | 0                             | 1. | 0       | 0  | 1 |

| L                | 1 | 1                   | 0 | 1 | D  | 1  | 0   | 0     | 0         | 0         | 0     | 0       | 1                             | 0  | 0       | 0  | 1 |

| L                | 1 | 1                   | 0 | 1 | D  | 1  | 1   | 0     | 0         | 0         | 1     | 0       | 0                             | 1  | 0       | 0  | 1 |

| R                | 1 | 1                   | 1 | 0 | D  | 0  | 0   | 0     | 1         | 0         | 0     | 1       | 0                             | 0  | 0       | 1  | 0 |

| R                | 1 | 1                   | 1 | 0 | D  | () | . 1 | 0     | 1         | 0         | 0     | 0       | 0                             | 0  | 0       | 1  | 0 |

| R                | 1 | 1                   | 1 | 0 | D  | 1  | 0   | 1     | 0         | 0         | 0     | 1       | 0                             | 0  | 0       | 1. | 0 |

| R                | 1 | 1                   | 1 | 0 | D  | 1  | 1   | 1     | 0         | 0         | 1     | 0       | 0                             | 0  | 0       | 1  | 0 |

| Rn               | 1 | 1                   | 1 | 1 | D  | 0  | 0   | 0     | 1         | 0         | 0     | 1       | 0                             | 0  | 1       | L  | 0 |

| Ro               | 1 | ī                   | 1 | 1 | D  | Ó  | 1   | 0     | 1         | 0         | 0     | 0       | 0                             | 0  | 1       | I  | 0 |

| Ro               | 1 | ī                   | 1 | ī | D  | 1  | 0   | 0     | 0         | 0         | 0     | 1       | 0                             | 0  | 1       | ï  | 0 |

| R <sub>0</sub>   | 1 | 1                   | 1 | 1 | 1) | 1  | 1   | $i$ } | 0         | O         | 1     | 0       | 0                             | 0  | 1       | 1  | 0 |

In Table II, the instructions, indicated by the columns denominated as I, L, R and  $R_o$ , are indicative respectively of 30 instructions left shift, right shift and right rotate. Mode dependent switches 47, 36, 39, 40, 37, 38, 48 and 45, controlled by signals  $C_1$  and  $C_2$ , are respectively indicated by  $R_n$ ,  $R_{T1}$ ,  $L_{T1}$ , BY,  $R_{T0}$ ,  $L_n$ , and  $R_0$ , while the mode independent right and left shift switches 41, 42 and 43, 44 are denominated R and L. In 35 Table II, the presence of a binary one indicates a particular switch is closed for the duration of a pulse on lead 55, a zero indicates an open circuit condition of the switch, while a D can be zero or one, at the will of the designer.

To provide a more complete understanding as to the 40 manner by which the register of FIG. 2 functions selectively to perform different instructions in the different connection modes, an example will be considered wherein a binary one signal, having a positive voltage, is continuously applied to terminal 34 while the  $C_1$  and  $C_2$  signals are both equal to zero and  $^{45}$ stages 31-33 are all cleared to zero; i.e., register connections are in accordance with mode 0 and the operation code signals, abcde, are respectively 11010. As indicated by the first line of Table II, logic network 59 responds to the stated mode and operation signals to shift data in the left direction from line 35 50 to line 34, whereby switches 38, 43, 44 and 39 are closed in response to each pulse on lead 55. While and for a short time before and after each of switches 38, 43, 44 and 39 is closed, switches 15 and 16 in each of register stages 31-33 are opencircuited in response to signals derived on lead 54.

In response to the first pulse on lead 55, switch 38 is closed to gate the positive voltage at line 35 to the input of register stage 33. Simultaneously, switches 15 and 16 in register stage 33 are in an open circuit condition, whereby inverter stage 11 60 in register stage 33 is loaded with a binary one. The binary one signal on terminal 35 is decoupled from the input of inverter stage 11 as the first pulse on lead 55 terminates; however, inverter 11 remains loaded to the binary one state because of the gate source capacity of MOSFET's 17 and 18. In response 65 to the termination of the positive voltage on lead 54, switches 15 and 16 are closed and the binary one state of inverter 11 is coupled to inverter 12 within register stage 33. The binary one state of inverters 11 and 12 is maintained after the trailing edge of the first pulse on lead 54 because of the regenerative 70 circuit established between terminals 13 and 14 through switches 15 and 16.

In response to the second pulse on lead 54, switches 15 and 16 in each of stages 31—33 are again open-circuited and inverter stages 11 and 12 in each register stage are isolated from 75

to isolate the inverter stages 11 and 12 in each register stage from any external source. Shortly after inverters 11 of register stages 31—33 are decoupled from the output of the preceding register stage, both inverters 11 and 12 within each stage are connected in a regenerative feedback loop in response to termination of the second pulse on lead 54. From the preceding description, it is believed obvious as to the manner in which stages 31—33 function in response to the signals applied to switches 38, 39, 43 and 44.

The complete repertoire of right rotate, right shift and left shift instructions for the four different modes will now be considered.

In the right rotate operation, data bits are transferred in sequence from stage 31 to stage 32 etc., from the highest order stage to the lowest order stage. When a bit reaches lowest order stage 33, it is transferred back to the highest order stage through switch 45. In response to the register being activated into modes 0 or 2, bits are serially coupled from stage 33 through switch 37 to lead 35; in contrast, bits may be coupled from the register to line 34 from stage 31 via switch 39 only while the register is activated into modes 0 or 1.

For shifting right, data bits are transferred in sequence from the highest order stage to the lowest order stage, i.e., from stage 31 to stage 32 to stage 33 etc., from left to right. In mode 0 data bits are serially fed to the register from line 34 through switch 36 and coupled to line 35 via switch 37. If no signal source is connected to line 34, the signal stored in the highest order register stage 31 is not altered because the capacity of inverter stages 11 and 12 is sufficient to enable the stored signal to be maintained between closures of the switches within the stage.

For right shift in mode 1, any signal source connected to line 34 is fed to register stage 31 through switch 36. If line 34 is floating, most significant bit stage 31 remains activated to the same state it had in response to a prior signal being coupled thereto. For both conditions of line 34, switch 37 is opencircuited, whereby line 35 is isolated from the remainder of the register. For right shift mode 2, all connections of the register to terminal 34 are open-circuited, while any data bits derived from least significant register stage 33 are coupled through switch 37 to terminal 35. Switch 47 is closed in response to each pulse on lead 55, whereby most significant bit stage 31 is continuously loaded with binary zeros. For right shift, mode 3, any signals coupled to terminal 34 are fed to terminal 35 via bypass switch 40, while the remainder of the re-

gister is decoupled from lines 34 and 35. Simultaneously, binary zeros are continuously fed to the input of stage 31 through switch 47 and internal shifts within the register occur without readout to line 35.

In all four modes, left shift generally involves shifting the 5 contents of a lower order register stage to a higher order stage, i.e., shifting from the output of a stage to the right, as illustrated by FIG. 2, to the left. For example, the contents at the output of stage 33 are shifted to the input of stage 32 and the output of stage 32 is shifted to the input of stage 31.

In left shift, mode 0, data bits coupled to line 35 are fed through switch 38 to the input of register stage 33 and are ultimately coupled from register stage 31 through switch 39 to data line 34. If terminal 35 is decoupled from a signal source and is floating, register stage 33 remains in the state to which is was previously activated in response to the last signal fed thereto. For left shift, mode 1, the output of register stage 31 is coupled to line 34 through switch 39, while line 35 is decoupled from stage 33 due to both switches 37 and 38 being open-20 circuited. Binary zeros are continuously loaded into least significant bit register stage 33 in response to switch 48 being closed upon the occurrence of each pulse on lead 55. For left shift, mode 2, signal sources connected to line 35 are coupled to the input of register stage 33 via switch 38 while the output 25 of stage 31 is decoupled from lead 34. If no signal source is connected to line 35, but the line is floating, least significant bit register stage 33 remains in the same state as the one to which it was previously activated. In left shift, mode 3, data lines 34 and 35 are connected together and are decoupled 30 and 69 as an OR circuit. The signal in the most significant from all of the register circuitry.

Internally of the register, the contents of stages 31-33 are sequentially fed from the lowest order register stage to the highest order stage. As signals are read from the lowest order stage 33, binary zeros are fed thereto in response to switch 48 35 being closed in synchronism with each pulse on lead 55.

The registers of FIG. 2 can be interconnected with other registers having the same configuration to form larger registers having stages which can be selectively interconnected. The registers can be connected in series with each other, in parallel 40 with each other, or in series parallel combinations to provide variable series operations. For example, it it were desired to provide a variable register having 48 stages, three 16-stage registers could be interconnected in series. Once the 48-stage register was established, it is possible, for example, to 45 segregate the 16-stage registers into separate parts which may include 32 stages and 16 stages. Data can be independently written into and out of the 16- and 32-stage registers, or different 16-stage registers can be bypassed at will. In general, it can be stated that if N registers of the type illustrated by FIG. 2 are interconnected, 4" different circuit combinations of those registers are possible.

Exemplary of some of the different combinations possible utilizing three registers of the type illustrated by FIG. 2 are circuits shown by FIGS. 3-5. In FIG. 3, each of registers 61, 62 and 63 is energized to mode 0 and the left and right data lines of each register are connected to the data lines of the adjacent register. Data are free to circulate between the various registers 61-63 to form a complete feedback register having a 60 total of 48 stages. Data can be shifted in the right or left direction between registers 61-63 and the individual registers can be activated, one at a time, to a rotate mode.

In FIG. 4, the same three registers of FIG. 3 are interconnected, whereby registers 64 and 66 are connected with each 65 other and respectively activated to modes 0 and 1; register 65 being activated into mode 3 is isolated from registers 64 and 66. Thereby, register 65 is unresponsive to circulation of data between registers 64 and 66 but can be energized for internal rotation and shifts as indicated by Table II supra. Registers 64 70 and 66 are interconnected with each other so that, for example, in response to a right rotate operation code, the output of the least significant stage of register 64 is fed to the most significant stage of register 66. Simultaneously, the most significant stage of register 64 remains in the state to which it was 75 reference numerals in the 100's, the 200's and the 300's. All

previously activated by a signal source coupled thereto; the most significant bit stage of register 64 is unresponsive to signals from the least significant stage of register 66 because the latter register is in mode 1 operation.

If the register configuration of FIG. 4 receives the operation code indicative of a left shift, the most significant bit stage of register 66 is coupled to the least significant bit stage of register 63. Simultaneously, the contents of the most significant bit stage of register 63 are overflow, and can be indicated as such as seen infra. The most significant bit stage of register 63 is not coupled to the least significant bit stage of register 66 because the latter register is in mode 1, whereby the least significant bit stage thereof is repeatedly loaded with binary zero

A further possible circuit configuration for a plurality of registers is illustrated by FIG. 5 wherein register 67 is energized to mode 0 and is connected in series with the parallel combination of registers 68 and 69, respectively energized to modes 1 and 2. By virtue of the mode configurations, the right side data terminal of register 67 is connected to the left side data terminal of registers 68 and 69, while the right side data terminals of the latter registers are connected to the left side data terminal of register 67.

With registers 67-69 in the stated mode conditions and assuming a rotate right operation command, the least significant bit stage of register 67 feeds binary bits to the most significant bit stages of registers 67 and 68. The most significant bit stage of register 68 responds to the signals fed to it from registers 67 stage of register 68 is circulated or rotated to the right, but output signals are not derived from the right output terminal of register 68. Register 69, however, is unresponsive to the contents of the least significant stage of register 67, by virtue of the former register being in mode 2; but register 69 continuously feeds the contents of its least significant bit stage to the most significant bit stage of register 67. In addition, the bits continuously derived from the least significant bit stage of register 69 are continuously fed back to the most significant stage thereof in response to the right rotation operation.

From the foregoing examples, it is believed obvious as to how a plurality of registers of the type illustrated by FIG. 2 can be interconnected together to provide various programmable functions as may be desired. The functions are not limited on an a priori basis but are completely amorphous and may be established at will in response to operation codes and mode

Consideration will now be given to the circuitry by which the basic register configuration of FIG. 2 can be employed as a large scale integrated circuit variable parallel processor, i.e., as a computer responsive to signals derived on parallel leads. and fed to parallel arithmetic computing circuitry. The parallel processor illustrated by FIG. 6 comprises three register stages 71-73 interconnected with each other selectively in a similar manner to register stages 31-33 of FIG. 2. Each of register stages 71-73 is substantially the same as the register stage illustrated by FIG. 1. A difference, however, exists between register stages 71-73 and the stage of FIG. 1 since the variable parallel processor of FIG. 6 is required to derive indications of the inverted state of a register. To this end, an output is derived from the gate electrode connection of inverter 12 for each of the register stages 71-73.

While the variable parallel processor of FIG. 3 is illustrated as including only three stages, it is to be understood that in an actual practical system, the number of stages is considerably in excess of three and is generally on the order of 16. By illustrating the variable parallel processor as having three stages, redundant circuitry associated with the central stages is eliminated from the drawing to simplify the exposition herein.

There are however many redundant switching components associated with each of stages 71-73. To simplify the description of these redundant components, all switches associated with register stages 71, 72 and 73, are respectively assigned switches that are identically connected in each of the register stage circuitry have identical unit and tens reference numerals. In general, only the circuitry for switches associated with the central stage register 72 are described in detail. Any differences in the circuitry associated with register stages 71 and 73 relative to register stage 72 are described in detail.

Register stages 71—73 are selectively coupled to read binary bits in sequence to and from left and right serial data lines 74 and 75; in addition, each of the register stages is selectively responsive to and from a binary bit on each of parallel data lines 76—78.

Stages 71—73 are selectively interconnected by means of switches 86—95, 97 and 98 in the same manner as register stages 31—33 are interconnected with switches 36—45, 47 and 48 to perform the same operations as the circuit of FIG. 2, as indicated by Table II, supra. For purposes of convenience, the similarly connected switches of FIGS. 2 and 6 have identical unit reference numerals and tens reference numerals displaced by a factor of 5.

Control of switches 86—95, 97 and 98 is in response to timing signals derived on leads 81 at the output of timing and control network 82, which is generally similar to timing and control network 51, FIG. 2. Timing and control network 82 derives output signals for controlling switching within register stages 71—73 in the same manner as stages 31—33 are controlled in response to the signals fed into and derived from inverters 56—58.

In addition to the time controlled signals derived on leads 81 and 83, timing and control network 82 responds to the operation code bits a-e and mode control signals C1 and C2 to selectively activate other switches associated with each of register stages 71-73 independently of timing pulses. The time independent switches associated with stages 71-73 respond 35 to the operation code bits a-d and the mode control signals C<sub>1</sub> and C<sub>2</sub> to enable 16 different instructions or commands to be performed by the parallel processor. The instructions are fed to the computer switches via leads 84 in response to the operation code bits a-d to enable the contents of the stages 40 71-73 to be: (1) selectively combined with signals on parallel input leads 76-78; (2) selectively combined with signals on serial leads 74 and 75; (3) cleared to zero or set to one; (4) shifted left and right; (5) loaded in response to the parallel data bits on leads 76-78; or (6) rendered into a nonoperating condition. Exemplary of how signals stored in stages 71-73 may be combined with the parallel data bits on leads 71-78 are the logic operations of AND, OR and EXCLUSIVE OR; and binary addition and subtraction in either the one's or 50 two's complement mode. Subtraction may be effected so that the contents of registers 71-73 are either the minuend or subtrahend. The operation code bit e is derived at will for any combination of operation codes a-d. Thereby, the contents of register stages 71-73 are read out to parallel data lines 76-55 —78 whenever the operation code e occurs.

Consideration is now given to the circuitry associated with the middle register stage 72, FIG. 6. Each of the switches to be described in conjunction with register stage 72 is operated in response to a predetermined combination of signals on leads 81 and 84. The inverters in the circuitry associated with register stage 72 are not switched, however, but are always in operation.

All arithmetic operations in the middle stage are performed in full adder 201, having input terminals A, A, B, B, C, and C. Full adder 201 responds to the three input signals thereof to derive a sum signal output on lead 202 and a carry signal output on lead 203. Full adder 201 includes conventional circuitry whereby the binary sum signal derived on lead 202 is represented as the Boolean function:

# S=ABC+ABC+ABC+ABC,

while the carry signal derived on lead 203 is indicative of the Boolean function:

# A B+C (A+B).

The input signals to terminals A and A of full adder 201 are derived from the true and inverted signals stored in register stage 72. To this end, switches 204 and 205 are respectively connected to the output and input of inverter 12 within stage 72, and the outputs of the switches are fed to a common junction at the A input terminal of full adder 201. The common junction of switches 204 and 205 is also fed to the A input of full adder 201 via inverter 206.

The input signals to the B and  $\overline{B}$  terminals of full adder 201 are selectively responsive to the binary bits on lead 77 or the binary one and zero signals derived respectively from the +10 volt source at terminal 207 and the ground voltage at terminal 208. Coupling of signal from parallel input lead 77 to the B and  $\overline{B}$  input terminals of full adder 201 is via switches 211 and 212, the former of which is directly responsive to the bit fed to lead 77 and the latter being responsive to the complement of the bit, as coupled through inverter 213. The output terminals of switches 211 and 212 have a common connection to the B input of full adder 201 as well as a connection to the  $\overline{B}$  input of the full adder through inverter 214. The binary one and zero signals at terminals 207 and 208 are selectively fed to the B and  $\overline{B}$  input terminals of full adder 201 via switches 215 and 216, respectively.

The  $\overline{C}$  and  $\overline{C}$  inputs of full adder 201 are selectively responsive to the binary one and zero voltages at terminals 207 and 208 via connections selectively established through a common junction at the output of switches 217 and 218, with the  $\overline{C}$  input terminal of the full adder being fed by the output of inverter 219. The C and  $\overline{C}$  input terminals of full adder 201 are also responsive to a carry signal derived from full adder 301 associated with register stage 73, as coupled through switch

Each of the just previously described switches, i.e., switches 204, 205, 211, 212, 215—218, and 221, is actuated in response to logical combinations of the a—d operation code signals fed into timing and control network 82 as derived on output leads 84. Thereby, the selective activation of each of these switches is independent of any timing pulses derived in timing and control unit 82 and depends solely upon a desired operation to be performed by the variable parallel processor.

The exact relationship between operation code bits a-e and these switches is described by means of Table III.

TABLE III

|       |   | Op code Switches independent of time |      |    |   |   |   |   |    |        |                |    |                | Time dependent<br>switches |     |        |        |        |        |     |         |    |

|-------|---|--------------------------------------|------|----|---|---|---|---|----|--------|----------------|----|----------------|----------------------------|-----|--------|--------|--------|--------|-----|---------|----|

|       |   |                                      | J CO | ue |   |   |   |   |    |        |                |    |                |                            |     | (3, 1) | (3, 1) | (0, 2) | (0, 1) |     | Witches |    |

| I     | а | b                                    | c    | d  | e | N | N | X | X  | K      | $\mathrm{B}_1$ | LG | $\mathbb{B}_2$ | Z                          | Out | ```Q   | Ĵ      | Car    | M      | A   | SUM     | IN |

| NOP   | 0 | 0                                    | 0    | 0  | 0 | D | 0 | 0 | 0  | 0      | 0              | 0  | 0              | 0                          | 0   | 0      | 0      | 0      | 0      | 0   | 0       | 0  |

| XOR   | 0 | 0                                    | 0    | 1  | 0 | 1 | 0 | 1 | 0  | 0      | 0              | 1  | 0              | 0                          | 0   | 0      | 0      | 0      | 0      | 0   | 1       | 0  |

| CNTD  | 0 | 0                                    | 1    | 0  | 0 | 1 | 0 | 0 | 0  | 0      | 1              | 0  | 0              | 1                          | 0   | 0      | 1      | 1      | 1      | 0   | 1       | 0  |