# PLXMon 98

software development utility

# Version 2.1

## Revision 1

# **User's Manual**

Copyright © 1998, PLX Technology, Inc.. All rights reserved.

This document contains proprietary and confidential information of PLX Technology Inc. (PLX). The contents of this document may not be copied nor duplicated in any form, in whole or in part, without prior written consent from PLX.

PLX provides the information and data included in this document for your benefit, but it is not possible for us to entirely verify and test all of this information in all circumstances, particularly information relating to non-PLX manufactured products. PLX makes no warranties or representations relating to the quality, content or adequacy of this information. Every effort has been made to ensure the accuracy of this manual, however, PLX assumes no responsibility for any errors or omissions in this document. PLX shall not be liable for any errors or for incidental or consequential damages in connection with the furnishing, performance, or use of this manual or the examples herein. PLX assumes no responsibility for any damage or loss resulting from the use of this manual; for any loss or claims by third parties which may arise through the use of this SDK; for any loss or claims by third parties which may arise through document is subject to change without notice.

Product and Company names are trademarks or registered trademarks of their respective owners.

Document number: PCISDK-MON-211

# **Table of Contents**

| 1. I | INTRODUCTION                                              | 1-1 |

|------|-----------------------------------------------------------|-----|

| 1.1  | About This Manual                                         | 1-1 |

| 1.2  | Conventions And Support                                   | 1-1 |

| 1.3  | PLXMon 98 Feature List                                    | 1-2 |

| 1.4  | Customer Support Information                              | 1-2 |

| 2.   | A BRIEF TOUR OF PLXMON 98                                 | 2-1 |

| 2.1  | Starting And Configuration                                | 2-1 |

| 2.2  | Displaying Registers                                      | 2-2 |

| 2.3  | Popular Features                                          | 2-3 |

| 2    | 2.3.1 Downloading To The IOP                              | 2-3 |

| 2    | 2.3.2 DMA Transfers                                       | 2-4 |

| 3. F | PLXMon 98 - Reference                                     | 3-1 |

| 3.1  | Access Mode                                               | 3-1 |

| 3    | 3.1.1 PCI Mode                                            | 3-1 |

| 3    | 3.1.2 Serial Mode                                         | 3-1 |

| 3.2  | Application Hot Links                                     | 3-2 |

| 3.3  | Device Configuration                                      | 3-2 |

| 3.4  | Downloading IOP Applications                              | 3-3 |

| 3.5  | Font Configuration                                        | 3-4 |

| 3.6  | The Interface                                             | 3-4 |

| 3    | 3.6.1 The PLXMon 98 Toolbar                               | 3-5 |

| 3    | 3.6.2 Status Bar                                          | 3-5 |

| 3    | 3.6.3 Command Line Interface (CLI)                        | 3-5 |

|      | 3.6.3.1 Displaying Memory Via Memory Cycles, (dl, dw, db) | 3-5 |

|      | 3.6.3.2 Displaying Memory Via I/O Cycles, (il, iw, ib)    | 3-6 |

|      | 3.6.3.3 Writing Memory Via Memory Cycles, (el, ew, eb)    | 3-6 |

|      | 3.6.3.4 Writing Memory Via I/O Cycles, (ol, ow, ob)       | 3-7 |

|      | 3.6.3.5 The Pci Command                                   | 3-7 |

|      | 3.6.3.6 The Quit Command                                  | 3-7 |

|      | 3.6.3.7 The Reg Command                                   | 3-7 |

|      | 3.6.3.8 The Repeat Command (r)                            | 3-7 |

|      | 3.6.3.9 User Variables (vars)                             | 3-8 |

|      | 3.6.3.10 The Ver Command                                  | 3-8 |

| 3.7  | Print, Print Preview, and Print Setup                     | 3-8 |

| 3.8  | Register Access/Register Sets                             | 3-8 |

| 3.9  | The Reset Button                                          | 3-9 |

| 3.10 | Selecting Devices    |  |

|------|----------------------|--|

| 3.11 | Serial Configuration |  |

| 3.12 | Serial EEPROM Access |  |

### APPENDIX A. THE PCI 9080 REGISTER SET

### A-1

| A.1 The | e Register Group Dialog Boxes                 | A-1 |

|---------|-----------------------------------------------|-----|

| A.1.1   | PCI Configuration Register Group Dialog Box   | A-1 |

| A.1.2   | Local Configuration Register Group Dialog Box | A-2 |

| A.1.3   | The Runtime Register Group Dialog Box         | A-6 |

| A.1.4   | The DMA Register Group Dialog Box             | A-7 |

| A.1.5   | The Messaging FIFO Register Group Dialog Box  | A-9 |

|         |                                               |     |

### APPENDIX B. THE PCI 9054 REGISTER SET

### B-1

| B.1 The | Register Group Dialog Boxes                   | B-1  |

|---------|-----------------------------------------------|------|

| B.1.1   | PCI Configuration Register Group Dialog Box   | B-1  |

| B.1.2   | Local Configuration Register Group Dialog Box | B-3  |

| B.1.3   | The Runtime Register Group Dialog Box         | B-7  |

| B.1.4   | The DMA Register Group Dialog Box             | B-9  |

| B.1.5   | The Messaging FIFO Register Group Dialog Box  | B-11 |

| PENDIX  | C. TROUBLESHOOTING                            | C-1  |

### APPENDIX C. TROUBLESHOOTING

| APPENDIX D. | <b>GLOSSARY OF TERMS</b> |

|-------------|--------------------------|

|-------------|--------------------------|

PLX SOFTWARE LICENSE AGREEMENT THIS PLX SOFTWARE DEVELOPMENT KIT INCLUDES PLX SOFTWARE THAT IS LICENSED TO YOU UNDER SPECIFIC TERMS AND CONDITIONS. CAREFULLY READ THE TERMS AND CONDITIONS PRIOR TO USING THIS SOFTWARE DEVELOPMENT KIT. OPENING THIS PACKAGE OR INITIAL USE OF THIS SOFTWARE DEVELOPMENT KIT INDICATES YOUR ACCEPTANCE OF THE TERMS AND CONDITIONS. IF YOU DO NOT AGREE WITH THEM, YOU SHOULD RETURN THE ENTIRE SOFTWARE DEVELOPMENT KIT TO PLX.

#### <u>LICENSE</u> Copyright (c) 1998 PLX Technology, Inc.

This PLX Software License agreement is a legal agreement between you and PLX Technology, Inc. for the PLX Software Development Kit (SDK), also referred to as "PLX SDK" which is provided on the enclosed PLX CD-ROM, or may be recorded on other media included in this PLX SDK. PLX Technology owns this PLX SDK. The PLX SDK is protected by copyright laws and international copyright treaties, as well as other intellectual property laws and treaties, and is licensed, not sold. If you are a rightful possessor of the PLX SDK, PLX grants you a license to use the PLX SDK as part of or in conjunction with a PLX chip on a **per project basis**. PLX grants this permission provided that the above copyright notice appears in all copies and derivatives of the PLX SDK. Use of any supplied runtime object modules or derivatives from the included source code in any product without a PLX Technology, Inc. chip is strictly prohibited. You obtain no rights other than those granted to you under this license. You may copy

### <u>License Agreement</u>

the PLX SDK for backup or archival purposes. You are not authorized to use, merge, copy, display, adapt, modify, execute, distribute or transfer, reverse assemble, reverse compile, decode, or translate the PLX SDK except to the extent permitted by law.

### <u>GENERAL</u>

If you do not agree to the terms and conditions of this PLX Software License Agreement, do not install or use the PLX SDK and promptly return the entire unused PLX SDK to PLX Technology, Inc. You may terminate your license at any time. PLX Technology may terminate your license if you fail to comply with the terms and conditions of this License Agreement. In either event, you must destroy all your copies of this PLX SDK. Any attempt to sub-license, rent, lease, assign or to transfer the PLX SDK except as expressly provided by this license, is hereby rendered null and void.

#### <u>WARRANTY</u>

PLX Technology, Inc. provides this PLX SDK AS IS. WITHOUT ANY WARRANTY. EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTY OF MERCHANTIBILITY OR FITNESS FOR A PARTICULAR PURPOSE. PLX makes no guarantee or representations regarding the use of, or the results based on the use of the software and documentation in terms of correctness, or otherwise; and that you rely on the software, documentation, and results solely at your own risk. In no event shall PLX be liable for any loss of use, loss of business, loss of profits, incidental, special or, consequential damages of any kind. In no event shall PLX's total liability exceed the sum paid to PLX for the product licensed hereunder.

# 1. Introduction

The PLXMon 98 program is a simple and powerful tool for working with PLX devices. By making this product both easy to use and effective the user will be able to realize all the features of a given PLX RDK. This is accomplished by grouping common registers into windows with a common theme, as well as providing useful utilities to manipulate the registers.

These dialog windows contain detailed information about each register and if necessary about the individual bits within. Combining this information with the programming algorithms included for accessing the various IOP components and the ability to communicate over both PCI and Serial buses, PLXMon 98 gives the tools needed to access any PLX RDK properly.

# 1.1 About This Manual

This manual is divided into 3 sections. After this introduction, a brief software tour is conducted. This will allow first time users to set up PLXMon 98 quickly, and see how some of the more common functions are used. The section following the tour is provided as a reference guide. In this area every feature found in PLXMon 98 is defined alphabetically. The final section provides rapid data, such as a glossary of terms, and customer support information.

# 1.2 Conventions And Support

References to Windows NT assume Windows NT 4.0 or higher and will be shown as WinNT. Similarly, references to Windows98 will be shown as Win98.

All references to IOP (I/O Platform) throughout this manual refer to the embedded hardware and all references to IOP software refer to the embedded software.

All values used in the manual are hexadecimal numbers, with the exception for memory sizes (used in Local Configuration Register screen). The prefix '0x' has been omitted from all hexadecimal numbers and is not required when entering values for PLXMon 98 fields.

It is important to note that PLXMon 98 can only operate with a PLX device. This version has been designed to work with the following PLX RDKs.

- PCI 9080RDK-401B;

- PCI 9054RDK-860;

- CompactPCI 9054RDK-860;

- PCI 9080RDK-RC32364;

- PCI 9080RDK-SH3;

- PCI 9080RDK-860;

- Any device that uses the PCI 9080 or PCI 9054 chips.

PLXMon 98 has been tested to ensure compatibility with both Windows NT and Windows98.

*Note: PLXMon* 98 *is designed to run best with a high-resolution display, such as* 1024*x*768 *with* 256 *colors or better. Users choosing to run the software at lower resolutions will find it visually undesirable.*

# 1.3 PLXMon 98 Feature List

PLXMon 98 provides the following features:

- Graphical User Interface (GUI) screens that are based on PLX device registers;

- Compatible with the PCI 9080 and PCI 9054 chips;

- Split Screen Interface, allowing command line input while receiving serial data.

- Serial communications with an IOP's debug port. This feature is compatible with PLX's Back-End Monitor protocol;

- A built-in downloader providing support for the following image standards: Motorola S-Record, IBM-401B Image Files, COFF, and Binary. This feature supports downloading to RAM and FLASH devices through the PCI bus.

- PLX EEPROM Configuration screens to modify the contents of NM93CS46, NM93CS56, and NM93CS66 EEPROMs;

- Customizable Hot-Links. This feature allows users to launch Win32 compatible programs such as testing and sample programs;

Note: PLXMon 98 is only compatible with PLX chips.

# **1.4 Customer Support Information**

Prior to contacting PLX customer support, please ensure that you are situated close to the computer that has the PCI SDK installed and have the following information:

- 1. Model number of the PLX PCI RDK (if any);

- 2. PLX PCI SDK version (if any);

- 3. Host Operating System and version;

- 4. Description of your intended design:

- PLX chip used

- Microprocessor

- Local Operating System and version (if any)

- I/O

- 5. Description of your problem; and

- 6. Steps to recreate the problem.

You may contact PLX customer support at:

Address: PLX Technology, Inc. Attn. Technical Support 390 Potrero Avenue Sunnyvale, CA 94086

| Phone: | 408-774-9060           |

|--------|------------------------|

| Fax:   | 408-774-2169           |

| Web:   | http://www.plxtech.com |

You may send email to one of the following addresses:

west-apps@plxtech.com

mid-apps@plxtech.com

east-apps@plxtech.com

euro-apps@plxtech.com

asia-apps@plxtech.com

# 2. A Brief Tour of PLXMon 98

This section will give a 10-minute tour of the PLXMon 98 program. During this tour you will become familiar with how to setup the program. Some of the more common features found in PLXMon 98 will also be discussed.

# 2.1 Starting And Configuration

PLXMon 98 can be started by:

- Typing Plxmon98 at the command prompt and pressing Enter; or

- Clicking on the icon in the PCI SDK folder in the Start Menu.

| Device: Bus 00, Slot 12, Device ID 1860, Vendor ID 1085 is opened<br>File Command PLX 9054 Registers Hot Links Help                                                                                                                            | d 📃 🗅 🕨                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Elle Command PLX 3054 Registers Hot Links Help  Elle Command PLX 3054 Registers Hot Links Help |                                      |

|                                                                                                                                                                                                                                                |                                      |

| TR TR TR TR                                                                                                                                                                                                                                    |                                      |

|                                                                                                                                                                                                                                                |                                      |

| ROM_APP: Hello World!                                                                                                                                                                                                                          |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                | F                                    |

| &ver<br>PCI SDK Version 2.1 Rev 1<br>December 23, 1998                                                                                                                                                                                         | Í                                    |

| å                                                                                                                                                                                                                                              |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                | F                                    |

| Communicate with the device through the PciApi Active Pane: Lower Pane                                                                                                                                                                         | Communication Mode: PCI PlxMon98.plx |

#### Figure 2-1 The PLXMon 98 Interface

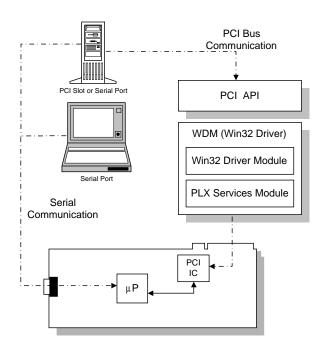

Depending on whether a supported PLX device is present, the monitor will enter PCI Mode or

Serial Mode. If a PLX device is in a PCI slot on your computer you will be in PCI mode, otherwise you will enter Serial mode. It is possible to switch back and forth between the two modes after the program has started. In Figure 2-1 the greyed-out upper pane would be enabled in Serial Mode. Also note this program can be run on a second computer and used to do remote debugging through a serial port.

If PLXMon 98 does not detect a standard PLX RDK on the system, it will notify the user that one does not exist. It is then necessary to add a device to the Properties menu or verify that the device data is correct in the Properties menu.

| 🔵 Do          | evice: Bus                                      | 00, Slot          | 13, Devi  | ce ID-0401,                |

|---------------|-------------------------------------------------|-------------------|-----------|----------------------------|

| <u>F</u> ile  | <u>C</u> ommand                                 | PLX 90 <u>8</u> 0 | Registers | Hot <u>L</u> inks <u>F</u> |

| <u>C</u> le   | ar                                              |                   |           |                            |

| Sav           | en Properties<br>ve Properties<br>ve Properties | File              | Ctrl+O    |                            |

|               | nt<br>ht Pre <u>v</u> iew<br>ht Setup           |                   | Ctrl+P    |                            |

| Pro           | per <u>t</u> ies                                |                   | Ctrl+T    |                            |

| E <u>x</u> it | :                                               |                   |           |                            |

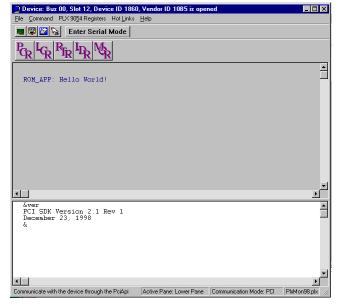

Until properties are assigned to the specific Vendor and Device ID of your RDK, the program will not know the data needed to access the board. To edit these values select the

Proper<u>t</u>ies item under the <u>File</u> pull-down menu. (You can also use the hot-key Ctrl-t).

The Properties menu first shows the Device Configuration page (see Figure 2-3). This data is used for PCI accesses only, the serial configuration data is retreived using BEM commands directly through the serial port. The Properties data will be correct if you are using a **standard PLX RDK**. These are the steps that should be followed however, to ensure proper operation of PLXMon 98.

| Properties from File: PlxMon98.plx                                                                                                       | ×                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Device Configuration Serial Communication Font                                                                                           |                                                                                 |

| ECI Device to Configure: 1085 7700<br>RDK Type:<br>PCI 9054RDK-860 T <u>FDK:Default</u><br>Local Memory Map<br>Memory Region 0. 20000000 | Eeprom Options<br>EEPROM Device: NM93CS56                                       |

| Memory Region 1:         00000000           ELASH Base Address:         FFF00000                                                         | FLASH Degice: AT 49LV040<br>FLASH Programming Method: HOST<br>Other             |

| PLX Register Base Address: 30000000                                                                                                      | Default Ram Application Format: COFF 🔽<br>Default Rom Application Format: BIN 👻 |

|                                                                                                                                          | QkCancelApply                                                                   |

Figure 2-3 Device Configuration

- 1. If the Vendor and Device ID is not listed under the "PCI Device to Configure" combo box, then click the "ADD" push button to create a new custom property entry for this device.

- 2. Now enter all the valid device information. By first clicking the RDK Default button, the default values for the RDK type selected will be entered on the screen. You should still verify that the Configuration EEPROM and FLASH EEPROM are the correct models.

- 3. Change the memory map, or set default datafile extension types, if necessary.

Now click the Serial Communications tab. If you wish to use the debug port on your

```

Device Configuration Serial Communication Font

```

RDK, then you need to select the correct COM port. Also note if you are in Serial mode when doing this change, you must switch out then back into Serial mode for your changes to take effect. The IOP software on the PLX RDKs have been designed to accept 38400 Baud only. You can also change the timeout length if desired.

To see command line data in a different font, select the font tab to select many different styles and point sizes. Select the underline option and it will turn the display screen into lined pages.

# 2.2 Displaying Registers

Whether you are in PCI mode or Serial mode, you can access the registers on a PLX RDK. It's as easy as clicking a button. The large buttons on the

lower tier display various register sets. Click on the PCI Configuration Registers (PCR) button. A formatted PCI register set appears with some bit decoding already done. Greyed-out boxes indicate read-only windows. Now close this window and open the Local Configuration Register (LCR) window.

By clicking on an edit box, you can change the hexadecimal value then either close the window or move the cursor to another edit box to enter the value. Clicking on a check box will

automatically update the register. Try it by clicking on the Details of any register box. The next dialog that appears will have check boxes to represent various bits of the register.

All the register capabilities mentioned above are applicable in Serial Mode as well as in PCI mode. PLXMon 98 uses the interface provided by the Back End Monitor (BEM) to read and write to register locations. For more information on BEM, see either the PCI SDK Programmers Manual or the glossary.

# 2.3 Popular Features

Now you can try using some tools that make PLXMon 98 very useful. This section of the tour will give you a brief overview of the IOP loader as well as interactive DMA.

### 2.3.1 Downloading To The IOP

If you want to download an application to the IOP side, this is the feature you will need to use.

Some of the features of the download utility include:

- Translation from different file formats including COFF, IBM Image file for the 401B, Motorola SRecord, and pure Binary.

- The ability to download the file to either RAM or FLASH ROM.

- Binary reads from FLASH ROM to a binary data file.

- Supports Serial downloads to RAM.

| Download to IOP                                                |                                 |                     |          | _ 🗆 🗵         |

|----------------------------------------------------------------|---------------------------------|---------------------|----------|---------------|

| Choose a file to download:<br>D:\Plx\PciSDK\IOP\Samples\Hello\ | 9080RDK-401B\Romh               | ello.bin            |          | •             |

| Device <u>Type</u>                                             | Status:<br>Successful in findin | g PLX devices       |          | Browse        |

| Data Broperties<br>Memory Offset in HEX: Entry                 | Point in HEX:                   | <u>R</u> ead Binary | Download | <u>C</u> lose |

Figure 2-4 Download To IOP

To familiarize yourself with downloading to an RDK, this tour will take you through the steps of downloading a RAM Hello Sample, and the Direct Master ROM sample, both of which are found in the PCI SDK. The examples below demonstrate downloading using the PCI 9054RDK-860 but the methods also apply to other PLX RDKs.

### Downloading to RAM

- 1. You must first select either a Serial or PCI channel before opening the Download window. If performing a PCI download you can connect a serial port to another running PLXMon 98 application, and see the download in progress.

- Open the Download Window by clicking the download to embedded icon, which looks like a small disk with a downward facing arrow.

- 3. In the Device Configuration information, RAM data is stored in COFF format for the currently selected device. Therefore the default file type will be COFF.

- Go to the directory: <Install-Path>\PLX\PciSdk211\IOP\Samples\Hello\9054RDK-860 and select the file RamHello.cof.

- 5. Click on download. You can verify that the program was successfully downloaded by reading the status screen (See Figure 2-4).

#### **Burning a FLASH ROM**

*Note:* If in the course of writing a program to the FLASH an error occurs, do not shut down the computer until you have re-burned a valid ROM program. Failure to do so will require removal of the FLASH ROM chip and re-burning in an external device programmer.

- 1. Downloads to FLASH are currently only supported via the PCI bus. The option to FLASH program will be disabled if entered in Serial mode. Select the FLASH device.

- 2. After selecting FLASH, set the desired image type. It will also be necessary to give an offset from the physical FLASH address set in the configuration menu. This is necessary because certain RDKs produce FLASH data to be downloaded to different addresses. The following chart describes the offsets used for each RDK.

| RDK Type               | FLASH OFFSET<br>(in HEX) |

|------------------------|--------------------------|

| PCI 9054RDK-860        | 0                        |

| PCI 9080RDK-401B       | 60000                    |

| CompactPCI 9054RDK-860 | 0                        |

| PCI 9080RDK-860        | 0                        |

| PCI 9080RDK-RC32364    | N/A                      |

| PCI 9080RDK-SH3        | 0                        |

#### Valid FLASH Offsets

3. Go to the directory:

$< Install-Path > PLX \ E (3.11) OP \ Samples \ Dmaster \ 9054 RDK - 860 \ and \ select \ the \ file \ Rom DM.bin.$

4. Now click on download. Again you can verify that the download was successful by reading from the serial port on another PLXMon 98, and by reading the Status window as well. A good way to test the ROM code is to reset the RDK, and verify the same program is run after the reset.

For a more complete description of the IOP download function consult the reference section.

### 2.3.2 DMA Transfers

DMA transfers can be used to copy data rapidly between the IOP and the PCI bus. This PCI bus could be a user-mapped common buffer, or another RDK's local space window. This example will demonstrate how to set up a simple IOP to PCI DMA transfer.

1. To set up the DMA transfer, some registers must be properly initialized. First click on the LDR button, to display the registers to be modified.

- 2. Set up the DMA transfer as seen in Figure 2-5. The minimum requirement for set up of the mode register is to set the Ready Input Enable. It is also recommended, but not required to set

- the bus width to 32 bit. These combinations give the mode register a value of 43. The value in PCI Address, listed here as "MAILBOX 0" is any valid physical PCI address. The SDK driver will allocate a fixed size buffer (10000 bytes by default) and place a pointer to this buffer in mailbox 0. The Local Address given here is valid for all supported RDKs up to a size of 40000 bytes (hex). Transfer direction is set within the Descriptor Pointer, the value 8 indicates an IOP to PCI DMA transfer.

*Note:* Channell DMA registers and threshold data registers are not displayed here and can be ignored for this example.

| - DMA CH0                                                                     |                  |          |                         |  |

|-------------------------------------------------------------------------------|------------------|----------|-------------------------|--|

| Mode                                                                          | (100h)           | 000000   | 43 <u>D</u> etails      |  |

| PCI Address                                                                   | (104h)           | MAILBO)  | ×0                      |  |

| Local Address                                                                 | (108h)           | 100400   | 00                      |  |

| Transfer Size                                                                 | (10Ch)           | 000010   | 00                      |  |

| Descriptor Pointer                                                            | (110h)           | 000000   | 08 D <u>e</u> tails     |  |

| Command/Status (128h)<br>Register Value 11 Transfer<br>Ø Data Transfer Enable |                  |          |                         |  |

| <u>S</u> tart Transfer                                                        | A <u>b</u> ort 1 | Transfer | <u>C</u> lear Interrupt |  |

Figure 2-5 DMA Channel 0 registers

- 3. To start the transfer, first enable the transfer by clicking the Data Transfer Enable bit. Clicking on Start Transfer will begin the operation. As the transfer size is so small, The DMA status will only flicker to Transfer in Progress before returning to Transfer Complete / Ready.

- 4. To verify the data was retrieved, read the system variable hbuf which is the user pointer to the PCI common buffer.

This concludes the tour of PLXMon 98. Remember, if any problems arose while following this tutorial, check the troubleshooting section of the manual or call PLX technical support. Information on both these options are found in the appendices.

# 3. PLXMon 98 - Reference

The reference section is provided to give detailed information about every feature of the PLXMon 98 application. It is organized alphabetically by feature title.

# 3.1 Access Mode

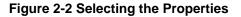

The two types of access to the RDKs are via the PCI bus and via the Serial port. See Figure 3-1.

## 3.1.1 PCI Mode

When PCI mode is selected all communication between PLXMon 98 and the PLX chip is done via the PCI SDK PCI (Host ) API and Windows device driver. This method will be familiar to users of PLXMon 97 and PLXMon 98 v2.0. The mode is selected by toggling the PCI button on the toolbar between PCI and Serial. Essentially this results in all communication to the PLX device via its PCI Bus interface. All RDK properties used in PCI communication are found in the Device Configuration menu.

## 3.1.2 Serial Mode

When serial communication mode is selected all communication between PLXMon 98 and the PLX device bypasses the PCI SDK API and device driver. Instead, PLXMon 98 communicates with the IOP's BEM module (refer to PCI SDK Programmer's Manual for BEM details). First the program queries RDK information such as the PLX register base address. Essentially this results in all communication to the PLX device via its Local Bus interface. Commands are limited to local reads and writes, and a local reset.

The following PLXMon 98 features are not available when operating in serial mode:

- Downloading to FLASH; and

- EEPROM Configuration.

Figure 3-1 PCI vs. Serial Data Flow

*Note:* To use this mode, your IOP software must contain the BEM module. All PLX RDKs support this mode by default.

## 3.2 Application Hot Links

PLXMon 98 offers the capability for users to add hot links to popular SDK applications. Typical applications that users may like to add hot links to are SDK samples, manufacturing test software, or custom applications.

| Application Ho |                     | ×                         |

|----------------|---------------------|---------------------------|

| Add to menu    | Application Name    | Executable File Browse    |

| <b>▽</b> 1     | WinNT DriverWizard  | DriverWizard.exe          |

| <b>▽</b> 2     | Direct Slave Sample | DSIave.exe                |

| <b>V</b> 3     | Block DMA Sample    | IntEvt.exe                |

| ☑ 4            | SGL DMA Sample      | Sgl.exe                   |

|                | Shuttle DMA Sample  | Shuttle.exe               |

| <b>▼</b> 6     | Calculator          | D:\WINDOWS\Calc.exe       |

| □ 7            |                     |                           |

| □ 8            |                     |                           |

| <b>9</b>       |                     |                           |

| <b>1</b> 0     |                     |                           |

|                |                     |                           |

|                |                     | <u>Q</u> K <u>C</u> ancel |

Figure 3-2 Application Hot Links dialog box

To use this feature you need to enter the Application Name and associated path to the executable in the Hotlinks pull-down menu. They will then appear in the Hot Link pull down menu.

# 3.3 Device Configuration

This dialog window can be found by pulling down the File menu then selecting Properties.

PLXMon 98 remembers program options for specific PLX RDKs and custom boards. These options are used throughout PLXMon 98 to setup default values for various program options. For example the flash properties are used by the loader to determine the flash programming method needed.

All supported device attributes are saved to a **Properties File**. This file has a default name PLXMon98.plx and is automatically loaded. PLXMon 98 will only search the current directory for this file so if the executable is moved, this file should be moved as well.

| Properties from File: PlxMon98.plx             | ×                                                        |

|------------------------------------------------|----------------------------------------------------------|

| Device Configuration Serial Communication Font | 1                                                        |

| PCI Device to Configure: 1085 77               | 109 ▼ <-Add Remove ->                                    |

| RDK Type:<br>oPCI 9054RDK-860                  | Eeprom Options                                           |

| Memory Region <u>0</u> : 20000000              | Flash options                                            |

| Memory Region <u>1</u> :                       | FLASH Device: AT 49LV040  FLASH Programming Method: HOST |

| ELASH Base Address: FFF00000                   | Other<br>Default Ram Application Format: COFF            |

| PLX Register <u>B</u> ase Address: 30000000    | Default Rom Application Format: BIN                      |

|                                                |                                                          |

|                                                | <u> </u>                                                 |

Figure 3-3 Device Configuration dialog box

PLXMon 98 uses the Vendor ID and Device ID to recognize a **supported** device. By adding a new entry to this list, a custom ID combination can be supported. Figure 3-3 shows the settings for the CompactPCI 9054RDK-860 board. Similar settings must be selected for each RDK that PLXMon 98 is used on.

When adding a new device, first enter the custom Vendor ID and Device ID. Then select its RDK type (if applicable). On hitting RDK Default, the normal settings for that RDK will be entered. Press Apply or OK to enter the data into the Properties file.

# 3.4 Downloading IOP Applications

In order to download to and execute programs on the IOP, the Download to IOP command is provided. This utility can be run by clicking on the icon, or by selecting it under the Command pull-down menu.

Files can be sent to either a RAM device or FLASH device and the base address is programmable.

Typically, all default values that are already selected will be correct for the download you wish to do. By selecting either RAM or FLASH, the file format will automatically be changed to the format that is specified for this device in the Device Config. menu

| Download to IOP                  |                                      |                |

|----------------------------------|--------------------------------------|----------------|

| Choose a file to download:       |                                      |                |

| D:\Plx\PciSDK\IOP\Samples\Hello\ | 9080RDK-401B\Romhello.bin            | •              |

| Device <u>T</u> ype              | Status:                              | <u>B</u> rowse |

| RAM device                       | Successful in finding PLX devices    |                |

| C FLAS <u>H</u> device           |                                      |                |

|                                  |                                      |                |

| Image Type                       |                                      |                |

| • COFF • IBM401 Image            |                                      |                |

| O Binary O <u>S</u> Record       |                                      |                |

| Data Properties                  |                                      |                |

| Memory Offset in HEX: Entry      | Point in HEX:                        |                |

|                                  |                                      |                |

|                                  | <u>H</u> ead Binary <u>D</u> ownload | <u>C</u> lose  |

|                                  |                                      |                |

|                                  |                                      |                |

Figure 3-4 File download dialog box

(Sect. 3.3). These features can be overridden, and by doing so the user should be knowledgeable about the format of these files and the memory map of the RDK being programmed.

*Note:* Programming the FLASH can be dangerous and it is important that the setup parameters be correct before the download is attempted. Data like RDK Type, Flash Address, Programming Method, and Memory Offset should be known beforehand.

To read the data on a FLASH device into a file, the <u>Read Binary</u> button can be used in conjunction with the memory offset window. This data will be retrieved unformatted and stored as a pure binary file. Currently the binary read function will create an image that starts at the memory offset provided and ends at the end of the usable flash range.

This utility also has the ability to program a device through the serial debug port. Currently the serial download supports only RAM programming.

# 3.5 Font Configuration

This dialog screen can be reached from the Properties option in the File pull-down menu. The font and point size will be changed in the display screen only. The appearance of the data in the dialog boxes will not be

changed.

| Default Properties                                                                |                                                         |                                               | ×     |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|-------|

| Device Configuration Serial Communication                                         | Font                                                    |                                               |       |

| Eont:<br>Courier<br>Arial Narrow<br>Bookman Old Style<br>Comic Sans MS<br>Courier | Font Style:<br>Regular<br>Bold<br>Italic<br>Bold Italic | Size:<br>11<br>10<br>▲<br>11<br>12<br>14<br>▼ |       |

| Effects<br>Stri <u>k</u> sout<br><u>U</u> nderline                                | ampleAaBb∛yZz                                           |                                               |       |

|                                                                                   | OK                                                      | Close                                         | Apply |

Figure 3-5 Font Select dialog box

# 3.6 The Interface

The PLXMon 98's main interface, shown in Figure 3-6 contains:

- A drop-down menu bar, with the five main drop-down menus. Depending on which PLX RDK is selected, certain options will be available. The PCI 9054 menu is shown here;

- A split screen interface used for simultaneous Command Line Interface (Lower Pane) and Serial Access (Upper Pane). Use the F6 key to toggle between active panes.

- An optional toolbar (for a full view, see Section 3.7.1);

- The status bar which reports the configuration file being used;

Figure 3-6 The PLXMon 98 Interface

• The Enter Serial Mode/Enter PCI Mode button that toggles between PCI and serial communication mode.

### 3.6.1 The PLXMon 98 Toolbar

The PLXMon 98 toolbar, shown in Figure 3-7, serves as an optional shortcut to the drop-down menu commands.

Figure 3-7 PLXMon 98 Toolbar

### 3.6.2 Status Bar

The status bar provides simple and useful tips. When the mouse is pointing on an object or a button, in the main window of PLXMon 98 the status bar displays some information about it. Tool-tips are also displayed when mouse pointer is held over an object for a short period.

### 3.6.3 Command Line Interface (CLI)

At the & prompt which is located in the Lower Pane, various commands can be entered to get

information on the RDK that is selected. This command line can be used in both PCI and Serial modes. To get a list of valid commands at any time in PLXMon 98, at the command line, type help or ?. The following sections will describe all the valid commands.

| •                                                          |                            |                         |              |

|------------------------------------------------------------|----------------------------|-------------------------|--------------|

| &help<br>Help is available for the fol<br>dl dw db el ew e | lowing commands:<br>b quit |                         |              |

| ? help r il iw i                                           | b vars                     |                         |              |

| ol ow ob ver reg<br>For more information, type HE<br>&     | pci<br>LP command.         |                         |              |

|                                                            |                            |                         |              |

| Ready                                                      | Active Pane: Lower Pane    | Communication Mode: PCI | PlxMon98.plx |

Figure 3-8 Valid Commands in PLXMon 98

Note: The CLI is not case sensitive.

### 3.6.3.1 Displaying Memory Via Memory Cycles, (dl, dw, db)

These commands display different sizes of data that are accessed through memory cycles. Using dl will return a 32-bit value, dw will return a 16-bit value, and db will return a 8-bit value.

They follow the format:

```

<command> <address> [[1] bytelength]

```

By default the bytelength is 80 [hex] bytes. Typing the command again with no arguments will make PLXMon 98 continue to display the range with the same bytelength as before.

### 3.6.3.2 Displaying Memory Via I/O Cycles, (il, iw, ib)

The iX commands are similar in syntax with the dX commands except they access memory using I/O cycles instead of memory cycles. They follow the format:

```

<command> <address> [[1] bytelength]

```

By default, the bytelength is dependent on the command. Using il will return 32 bits of data, iw will return 16 bits, and ib will return 1 byte. All these lengths can be overridden, however. By re-typing the command with no arguments, PLXMon 98 will continue to display the memory locations using the size of the data retrieved as the increment size.

### 3.6.3.3 Writing Memory Via Memory Cycles, (el, ew, eb)

Again the syntax of the write using memory cycles is similar to the dX commands. Using el will write values as 32 bit wide objects, ew will write on 16 bit values, and eb will write a byte at a time.

They follow the format:

```

<command> <address> [INC increment] [value]

```

While the input address is required, both the value and the increment parameter are optional. By not entering the [value] parameter, the program will query you for data in interactive mode. Interactive mode allows the user to press the space bar between after typing the value he/she want to enter and PLXMon 98 will auto-increment the write address the size of the data being entered. Press the enter key to exit the command. By changing the INC parameter in the command line above, the auto-increment value can be changed. What follows is a brief example of how to use this command.

If the user types the command  $eb \pm 0$  INC 4, they wish to interactively write bytes to the location  $\pm 0$  (which is a system label, more on this in section 3.7.3.6). Every time the user enters a value and hits space the program will query for the previous address plus INC which is 4. On

display of the memory range the user should see the following screen.

The 00: bytes that appear before each user entry are the previous values that are about to be overwritten by the user's data.

| •                                                                        |                         |                         |              |

|--------------------------------------------------------------------------|-------------------------|-------------------------|--------------|

| &eb s0 INC 4<br>80019000 00:a 00:b 00:c 00:d                             | 00:                     |                         |              |

| &dl s0 1 20<br>80019000: 0000000A 000000B<br>80019010: 00000000 00000000 |                         |                         |              |

| δ.                                                                       |                         |                         |              |

|                                                                          |                         |                         |              |

| Ready                                                                    | Active Pane: Lower Pane | Communication Mode: PCI | PlxMon98.plx |

Figure 3-9 Interactive Mode

### 3.6.3.4 Writing Memory Via I/O Cycles, (ol, ow, ob)

The oX commands are simpler syntactically than the memory cycle writes. Each command writes a different sized data object to a port address. They require only two parameters:

```

<command> <address> <value>

```

### 3.6.3.5 The Pci Command

This command allows read/write access the PCI configuration registers. It's syntax is as follows:

```

pci <pci offset> [value]

```

To write to the required offset, just add the value to write; otherwise the value will be displayed as a 32-bit register value.

Note: the offset will be different depending on the Access mode: PCI or Serial.

### 3.6.3.6 The Quit Command

The quit command terminates the application PLXMon 98.

### 3.6.3.7 The Reg Command

The reg command allows users access to the PLX RDK's local register sets. Data can be read or written in 32 bit sizes at a given byte boundary. The syntax of the command is as follows:

reg <register offset> [value]

If a [value] is given, the command will write the data to the specified address.

### 3.6.3.8 The Repeat Command (r)

The repeat command can is used to make PLXMon 98 repeat the command types before the r a set number of times. It's syntax is as follows:

[command] r [iterations]

If the number of iterations is not given, then PLXMon 98 will execute the command indefinitely until the user hits a key. The command to be repeated must be in the same expression as the r command.

This table lists the variables set by PLXMon 98 and what memory ranges they

represent:

### 3.6.3.9 User Variables (vars)

PLXMon 98 creates some user labels as a mnemonic aid for common memory locations. These strings can be used interchangeably with the values they represent.

| Variable Name   | Description                                         | PCI or Serial |

|-----------------|-----------------------------------------------------|---------------|

| hbuf            | User mapped region of the PCI common buffer.        | PCI           |

| PlxRegBase      | Memory-mapped PLX RDK registers                     | PCI           |

| PlxIoBase       | I/O mapped PLX RDK registers                        | PCI           |

| PlxLocalBusBase | Memory address which represents the Local Bus       | PCI           |

| s0              | Local Space 0                                       | PCI           |

| s1              | Local Space 1                                       | PCI           |

| s2              | Local Space 2                                       | PCI           |

| s3              | Local Space 3                                       | PCI           |

| pciVar          | Local address base of PCI registers                 | Serial        |

| lcrVar          | Local address base of local configuration registers | Serial        |

| rtrVar          | Local address base of runtime registers             | Serial        |

| dmaVar          | Local address base of DMA registers                 | Serial        |

| mqrVar          | Local address base of messaging queue registers     | Serial        |

**Figure 3-10 User Variables and their definitions**

### 3.6.3.10 The Ver Command

Displays the version data contained in the PCI SDK software release. This version of PLXMon 98 is compatible only with PCI SDK v2.1 Rev 1. This command is usable only during PCI accesses.

# 3.7 Print, Print Preview, and Print Setup

The print commands (Print, Print Preview, Print Setup...) can be found under the <u>File</u> pull-down menu. These selections enable the user to create a formatted picture of the display window. Print preview will allow you to see the formatted screen before you print.

## 3.8 Register Access/Register Sets

The contents of registers can be represented in one of two ways in PLXMon 98. Usually when a full 32-bit register is being displayed, it is shown in an edit box in hexadecimal format (*the 0x prefix is implied*). These boxes, if not greyed-out, can be modified by typing in new values. The value will be updated when the user closes the window or when the cursor is moved to another edit box.

Check boxes are also used to display and change individual bits on a register. If the check box is on a main dialog window then a state change is immediate. If the check box is in a Details dialog with other checkboxes, then only upon closing the dialog are the changes made.

Please refer to Appendices A and B for specific details on the PCI 9080 and PCI 9054 register set, respectively.

## 3.9 The Reset Button

Found on the taskbar, the reset button is signals the PLX RDK that is currently selected to reset both PCI and Serial modes.

*Note:* The method used to reset is customized for PLX RDKs. This feature should not be used on devices that do not support the reset algorithm. Consult the BSP source code for information on the algorithm used.

# **3.10 Selecting Devices**

The Select A Device menu item, shown in Figure 3-11, is used to select a PCI device to access. The pointer points to the currently selected device.

| Sele | ect a | Device   |      |           |           |              | _ 🗆 ×          |

|------|-------|----------|------|-----------|-----------|--------------|----------------|

| [    | elect | a Device |      |           |           |              |                |

|      |       | Bus      | Slot | Device ID | Vendor ID | Properties   |                |

|      |       | 0x00     | 0x13 | 0x401     | 0x10B5    | PlxMon98.plx | <u>0</u> K     |

|      |       | 0x00     | 0x12 | 0x1860    | 0x10B5    | PlxMon98.plx |                |

|      |       |          |      |           |           |              | <u>C</u> ancel |

|      | Ch    | ір Туре: |      | 09080     | PCI9054   |              |                |

|      |       |          |      |           |           |              |                |

Figure 3-11 Device Select dialog box

To select a new device, move the highlight to the desired PCI device by using either the mouse or the cursor arrow keys, and click the OK button or press the Enter key. The pointer will not move to the new selection until OK button is pressed or until the item is double-clicked.

The chip type radio button indicates which PLX device is present on the selected device.

Note: Only PLX devices are shown in the list.

# 3.11 Serial Configuration

PLXMon 98 offers the capability to communicate with the PLX device through the serial port. To

do so you must configure the appropriate serial port settings as shown in the figure below.

Communication ports COM1 through COM4 are supported. Baud rates 9600, 19200, 38400, and 57600 are supported.

*Note:* All PLX RDK's should be configured to 38400 baud, 8 Data Bits, No Parity, 1 Stop Bit, and no Flow Control.

| roperties from File: |                            |       |

|----------------------|----------------------------|-------|

| Device Configuration | Serial Communication Font  |       |

| ⊢ Po                 | ort Settings               |       |

|                      | Serial Port: COM 2         |       |

|                      | Baud Rate: 38400           |       |

|                      | Data Bits: 8               |       |

|                      | Parity: NONE               |       |

|                      | Stop Bits: 1               |       |

|                      | Flow Control: NDNE         |       |

|                      | ommunication Setting       |       |

|                      | <u>⊺</u> ime out (sec.): 2 |       |

|                      | Display BemL1 Reply        |       |

|                      |                            |       |

|                      |                            |       |

|                      | <u> </u>                   | spply |

Figure 3-12 Serial Communications Properties dialog box

## 3.12 Serial EEPROM Access

Pressing the Serial EEPROM *button* on the toolbar of PLXMon 98 will start the dialog

box seen below. No data will be written until the Write button is pressed. Clicking Refresh will overwrite any changes made.

Note: Having the wrong Serial EEPROM type selected in the Device Config. Menu can cause PLXMon 98 to read/write invalid data.

| Displaying 93CS56 EEPROM values                                                                                                                                                                                                                                                                                                                                               |                                                                                  |                                                                        |                                              |                                                                                                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Subsystem ID (2Ch) 9054 Sub Vendor ID (2                                                                                                                                                                                                                                                                                                                                      |                                                                                  | terrupt Line (3Ch) ∫<br>ax_Lat (3Fh) ∫                                 | Hot Swap Control O0 Interrupt Pin O0 Min_Gnt | (48h) 00004C06<br>(3Dh) 01<br>(3Eh) 00                                                                                     |  |  |

| Local Configuration Registers                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |                                                                        |                                              |                                                                                                                            |  |  |

| Remap for PCI to Local Address Space 0         (04h)           Local Arbitration Register         (08h)           Endian-Local Misc-VPD Boundary Register         (0Ch)           Range for PCI to Local Expansion RDM         (10h)           Remap for PCI to Local Expansion RDM         (14h)           Bus Region Descriptor for PCI to Local Access (18h)         [14h] | 00000001 Loc<br>0101000C → PCI<br>00305524 → PCI<br>00000000 Ran<br>00000010 Ren | cal Bus Address for D<br>I Base Address (Rem<br>I Config. Addr. Reg. f |                                              | (20h) 4000000<br>(24h) 5000000<br>(28h) 0000003 ⇒<br>(20h) 0000000 ⇒<br>(F0h) FF000000<br>(F4h) 1000001<br>(F8h) 0000040 ⇒ |  |  |

| Runtime Registers<br>Mailbox 0 (User Defined) (78h)                                                                                                                                                                                                                                                                                                                           | 00000000 Mai                                                                     | ilbox 1 (User Defined                                                  | )                                            | (7Ch) 00000000                                                                                                             |  |  |

| Show Offset in: C Serial EEPROM Offset C Mapping to PCI Configuration Addr. and PCI Offset from Base Addr. The EEPROM type you selected in the Configuration menu is NS93CS56.                                                                                                                                                                                                |                                                                                  |                                                                        |                                              |                                                                                                                            |  |  |

Figure 3-13 Serial EEPROM dialog box

# Appendix A. The PCI 9080 Register Set

Each of the PCI 9080's register groups has a distinct dialog box. Each dialog box has the register values, the register's PCI base addresses, and a description of the register. Some registers have check boxes and radio buttons to help in describing and setting the register values. Additional dialog boxes are available for more complex registers if necessary.

# A.1 The Register Group Dialog Boxes

The PLXMon 98's toolbar contains five buttons for register accesses. They are for PCI Configuration Registers (PCR), Local Configuration Registers (LCR), RunTime Registers (RTR), Local DMA Registers (LDR), and Messaging Queue Registers (MQR).

### A.1.1 PCI Configuration Register Group Dialog Box

The grayed text, in Figure A-1, on the PCI Configuration Registers dialog box indicates that the values cannot be modified using this dialog box. The radio buttons and check

| PCI Registers       |       |          |        |                   |            |                 |

|---------------------|-------|----------|--------|-------------------|------------|-----------------|

| Vendor ID           | (00h) | 10B5     |        | Device ID         | (02h)      | 0401            |

| Command             | (04h) | 0007     |        | Status            | (06h)      | 0280            |

| Revision ID         | (08h) | 01       |        | Class Code        | (09h)      | 068000          |

| Cache Line Size     | (0Ch) | 08       |        | Latency Timer     | (0Dh)      | 20              |

| Header Type         | (0Eh) | 00       |        | Build-In Self Te  | est (OFh)  | 00 🗌 BIST       |

| Base Address 0      | (10h) | E8000000 | □ 1/0  | ⊙ 32 ○ 1 MB       | O 64       | Prefetchable    |

| Base Address 1      | (14h) | 00006901 | ✓ 1/0  | ⊙ 32 ⊖ 1 MB       | O 64       | Prefetchable    |

| Base Address 2      | (18h) | 26000000 | □ 1/0  | ⊙ 32 ○ 1 MB       | O 64       | Prefetchable    |

| Base Address 3      | (1Ch) | 27000000 | □ 1/0  | ⊙ 32 ⊖ 1 MB       | O 64       | Prefetchable    |

| Base Address 4      | (20h) | 00000000 | □ 1/0  | ⊙ 32 ⊖ 1 MB       | O 64       | Prefetchable    |

| Base Address 5      | (24h) | 00000000 | □ 1/0  | ⊙ 32 ○ 1 MB       | O 64       | Prefetchable    |

| CardBus CIS Pointer | (28h) | 00000000 |        |                   |            |                 |

| Sub Vendor ID       | (2Ch) | 1085     |        | SubSystem ID      | (2Eh)      | 9080            |

| Expansion ROM       | (30h) | 00000000 | 🗖 Addr | ess Decode Enable |            |                 |

| Interrupt Line      | (3Ch) | 09       |        | Interrupt Pin     | (3Dh)      | 01              |

| Minimum Grant       | (3Eh) | 00       |        | Max Latency       | (3Fh)      | 00              |

|                     |       |          |        | _                 |            |                 |

|                     |       |          |        |                   | <u>0</u> K | <u>R</u> efresh |

Figure A-1 PCI Configuration Registers dialog box

boxes, indicate the current settings of the register bit fields. To update the contents of the dialog box push the Refresh button.

### A.1.2 Local Configuration Register Group Dialog Box

The Local Configuration register values are updated through the related edit and dialog boxes, in

Figure A-2, respectively. The size text box reflects the value (in bytes) of the associated register. The memory size is calculated from the corresponding register value and cannot be modified directly. To change the memory size, modify the associated register.

| L | ocal Configuration |                                                                                          | ¢ |

|---|--------------------|------------------------------------------------------------------------------------------|---|

|   | LocalO Range       | (00h) FF000000 Map into PCI Memory Space 💌 Encode 🛛 in 32 bit PCI Space 💌 🗖 Prefetchable |   |

|   |                    | Size in byte: 16,777,216                                                                 |   |

|   | Local0 Remap       | (04h) 00000001 🔽 Direct Slave Enabled                                                    |   |

|   | Local Arbitration  | (08h) 0021001C Details                                                                   |   |

|   | Endian Descriptor  | (0Ch) 000000C1 Dgtais                                                                    |   |

|   | Exp. ROM Range     | (10h) 00000000 Rom Size in byte: 0                                                       |   |

|   | Exp. ROM Remap     | (14h) 00000000 Delay 0 F BREQ Enable F BREQ Timer-Resolution                             |   |

|   | Region0 Descriptor | (18h) 47400343 Details                                                                   |   |

|   | Local DM Range     | (1Ch) F8000000 Size in byte: 134,217,728                                                 |   |

|   | Local DM Mem Base  | (20h) B8000000                                                                           |   |

|   | Local DM IO Base   | (24h) B0000000                                                                           |   |

|   | DM PCI Remap       | (28h) 00000003 Detgils                                                                   |   |

|   | DM Config IO Addr  | (2Ch) 00000000 Details                                                                   |   |

|   | Local1 Range       | (F0h) FF000000 Map into PCI Memory Space 💌 Encode in 32 bit PCI Space 💌 🏳 Prefetchable   |   |

|   |                    | Size in byte: 16,777,216                                                                 |   |

|   | Local1 Remap       | (F4h) 00000001 🔽 Direct Slave Enabled                                                    |   |

|   | Region1 Descriptor | (F8h) 00000343 Detais                                                                    |   |

|   |                    | <u>DK</u>                                                                                |   |

| _ |                    |                                                                                          |   |

Figure A-2 Local Configuration Registers dialog box

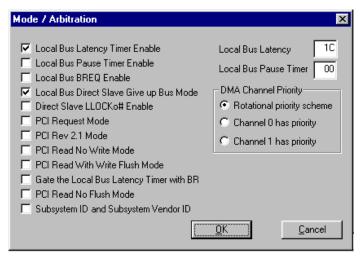

Six registers within the Local Configuration Register Group have a more detailed dialog box and are as follows:

- The Mode/Arbitration dialog box;

- The Endian Descriptor dialog box;

- The Space 0/Exp ROM dialog box;

- The DM PCI Remap dialog box;

- The DM Config IO Address dialog box; and,

- The Space 1 dialog box.

#### The Mode/Arbitration Dialog Box

The Mode/Arbitration dialog box provides information on the current value Local/DMA Arbitration register and allows modification of that value (see Figure A-3).

Figure A-3 Direct Master Mode / Arbitration dialog box

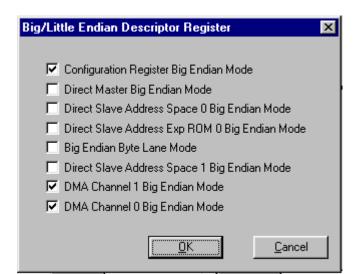

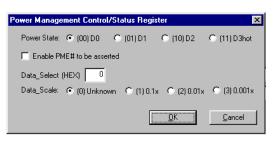

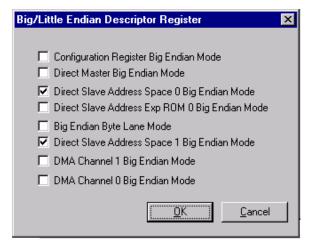

#### Figure A-4 Endian Descriptor dialog box

#### **Endian Descriptor Dialog Box**

The Endian Descriptor dialog box provides information on the current value of the Big/Little Endian Descriptor register and allows modification of that value (see Figure A-4).

# The Local Space 0/Exp ROM Dialog Box

The Region 0 Descriptor dialog box provides information on the current value of the Local Address Space 0/Expansion ROM Bus Region Descriptor register and allows modification of that value (see A-5).

| Region 0 Descriptor                                                                                                                                                | ×                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Space 0<br>Bus Width<br>S bit C 16 bit C 32 bit<br>Internal Wait State<br>Ready Input Enabled<br>BTERM# Input enabled<br>Prefetch Disabled<br>Burst Enabled | Expansion ROM Space<br>Bus Width<br>8 bit 16 bit 32 bit<br>Internal Wait States<br>Ready Input Enabled<br>BTERM# Input enabled<br>Prefetch Disabled<br>Burst Enabled |

| <ul> <li>Read Prefetch Count Enabled</li> <li>Extra Long Load from Serial EEPROM (</li> <li>Direct Slave Write</li> <li>Target Retry Delay</li> </ul>              | Prefetch Count 0<br>(Status)                                                                                                                                         |

Figure A-5 Local Space 0/Exp ROM dialog box

| DM PCI Remap Register                                                                                                                                                                                                     |                                                                                         | × |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---|--|--|

| Read Prefetch Size<br>C Continous<br>Up to 4 Lwords<br>Up to 8 Lwords<br>Up to 8 Lwords<br>Up to 16 Lwords                                                                                                                | Write Delay<br>No delay<br>Delay 4 PCI clock<br>Delay 8 PCI clock<br>Delay 16 PCI clocl |   |  |  |

| <ul> <li>DM Mem. Access Enable</li> <li>DM 10 Access Enabled</li> <li>LLOCK# Input Enabled</li> <li>DM PCI Read Mode</li> <li>Write and Invalidate Mode</li> <li>DM Prefetch Limitted</li> <li>Select IO Remap</li> </ul> | Almost Full 0<br>PCI Remap 0000                                                         |   |  |  |

| <u>OK</u> ancel                                                                                                                                                                                                           |                                                                                         |   |  |  |

Figure A-6 Direct Master PCI Remap dialog box

#### The Direct Master PCI Remap Dialog Box

The Direct Master (DM) PCI Remap dialog box provides information on the current value of the PCI Base Address (Remap) Register for Direct Master to PCI Memory and allows modification of that value (see Figure A-6).

#### The DM Configuration I/O Address Dialog Box

The DM Configuration I/O Address dialog box provides information on the current value of the PCI configuration Address Register for Direct Master to PCI I/O-CFG and allows for modification of that value (see Figure A-7).

| DM Config/IO                            | × |

|-----------------------------------------|---|

| Configuration Type<br>• Type 0 • Type 1 |   |

| Register Number 00                      |   |

| Function Number 00                      |   |

| Device Number 00                        |   |

| Bus Number 00                           |   |

| Configuration Enabled                   |   |

| Cancel                                  |   |

Figure A-7 Direct Master Configuration I/O Address dialog box

| Region 1 Descriptor                    | × |  |  |  |  |

|----------------------------------------|---|--|--|--|--|

| Bus Width<br>O 8 bit O 16 bit O 32 bit |   |  |  |  |  |

| Internal Wait State                    |   |  |  |  |  |

| 🔽 Ready Input Enabled                  |   |  |  |  |  |

| BTERM# Input enabled                   |   |  |  |  |  |

| 🔽 Burst Enabled                        |   |  |  |  |  |

| Prefetch Disabled                      |   |  |  |  |  |

| 🥅 Read Prefetch Count Enabled          |   |  |  |  |  |

| Prefetch Count                         |   |  |  |  |  |

| <u> </u>                               |   |  |  |  |  |

Figure A-8 Region 1 dialog box

### The Region 1 Dialog Box

The Region 1 dialog box provides information on the Local Address Space 1 Bus Region Descriptor register and allows modification of that value (see Figure A-8).

### A.1.3 The Runtime Register Group Dialog Box

The Runtime Register Group dialog box displays the current register values. All register values can be modified by changing the

contents of any register.

| Runtime Registers                 | ×                                                 |

|-----------------------------------|---------------------------------------------------|

| Mailbox Registers                 | Doorbell and Control Registers                    |

| Mailbox Register 0 (78h) 00611000 | PCI to LOC Doorbell Reg (60h)                     |

| Mailbox Register 1 (7Ch) 00000000 | LOC to PCI Doorbell Reg (64h) 00000000            |

| Mailbox Register 2 (48h) 00000000 | Interrupt Ctrl/Status Reg. (68h) 0F000001 Details |

| Mailbox Register 3 (4Ch) 00000000 | EEPROM, PCI, User IO (6Ch) 9803767E Details       |

| Mailbox Register 4 (50h)          | PCI Permanent Config ID (70h) 90801085            |

| Mailbox Register 5 (54h) 00000000 | PCI Permanent Revision (74h) 00000002             |

| Mailbox Register 6 (58h) 00000000 |                                                   |

| Mailbox Register 7 (5Ch) 00000000 | Close Befresh                                     |

|                                   | ii Henesh                                         |