Starting Materials and Functional Layers for The 2005 International Technology Roadmap for Semiconductors: Challenges and Opportunities

## Howard R. Huff<sup>(a)</sup>, David Myers<sup>(b)</sup>, Mike Walden<sup>(c)</sup>, Larry Beckwith<sup>(d)</sup>, Neil Weaver<sup>(e)</sup>, George Celler<sup>(f)</sup>, Bob Standley<sup>(g)</sup> and Mayank T. Bulsara<sup>(h)</sup>

(a) SEMATECH

(b) Texas Instruments, retired

(c) SUMCO

(d) National Semiconductor

(e) SEH

(f) SOITEC-USA

(g) MEMC

(h) Amberwave Systems

Accelerating the next technology revolution.

SEMATECH

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology

## **Starting Materials Team Members**

#### Howard Huff (ISMT) - Chair ; Mike Walden (SUMCO) - Co-Chair

| Physical Models &<br>Statistical Distributions | Polished / Epitaxial Wafer   | SOI Wafer                           | Metrology                      | Emerging Materials                  |  |  |  |

|------------------------------------------------|------------------------------|-------------------------------------|--------------------------------|-------------------------------------|--|--|--|

| Larry Beckwith (Ntl'I)                         | Olli Anttila (Okmetic Oyj)   | Michael Alles (Vanderbilt U.)       | George Brown (ISMT)            | Mayank T. Bulsara (AmberWave)       |  |  |  |

| W. Murray Bullis (Mtls & Metrology)            | Joel Barnett (ISMT)          | Luis Aparicio (Siltronic)           | Laszlo Fabry (Siltronic)       | George Celler (SOITEC)              |  |  |  |

| Bill Hughes (MEMC)                             | Juanita Chambers (Siltronic) | Mayank T. Bulsara (AmberWave)       | Dick Hockett (Charles Evans) * | Bruce Kellerman (MEMC)              |  |  |  |

| <mark>Mototaka Kamoshida (NEC Tokin)</mark>    | 'Roxanne Dulas (Siltronic)   | George Celler (SOITEC)              | Noel Poduje (ADE)              | Lalita Manchanda (SRC/Agere)        |  |  |  |

| Paul Langer (Komatsu)                          | Graham Fisher (MEMC)         | Michael Current (FSM)               | Chris Sparks (ISMT)            | Jim Moreland (Siltronic)            |  |  |  |

| Don McCormack (ISMT)                           | Glenn Gale (TEL) *           | Harry Hovel (IBM)                   | Bob Standley (MEMC)            | Doug Meyer (ATMI)                   |  |  |  |

| Noel Poduje (ADE)                              | Dinesh Gupta (STA)           | Sien Kang (SiGen)                   | Carl Treadwell (KLA-Tencor)    | Bob Standley (MEMC)                 |  |  |  |

|                                                | Kevin Han (TSMC)             | Jerry Liu (ADE)                     | Peter Wagner (Siltronic) *     | Neil Weaver (SEH)                   |  |  |  |

|                                                | Bob Johnston (SUMCO)         | Stephane Monfray (ST Micro)         |                                | Rick Wise (TI)                      |  |  |  |

|                                                | Susanne Weizbauer (Infineon) | Helmut Oefner (Infineon)            |                                | Ted White (Freescale Semiconductor) |  |  |  |

|                                                | Wen Lin (Consultant)         | Gerd Pfeiffer (IBM)                 |                                |                                     |  |  |  |

|                                                | Tom McKenna (TI)             | K.V. Ravi (Intel)                   |                                |                                     |  |  |  |

|                                                | Fred Meyer (Komatsu)         | Ted White (Freescale Semiconductor) |                                |                                     |  |  |  |

|                                                | Dave Myers (Consultant)      |                                     |                                |                                     |  |  |  |

|                                                | Pete Sandrow (LG Siltron)    |                                     |                                |                                     |  |  |  |

|                                                | Jack Thomas (AMD)            |                                     |                                |                                     |  |  |  |

|                                                | Neil Weaver (SEH)            |                                     |                                |                                     |  |  |  |

|                                                | Masaharu Watanabe (NuFlare)  |                                     |                                |                                     |  |  |  |

|                                                |                              |                                     |                                |                                     |  |  |  |

\* Corresponding Member

SEMATECH

## Agenda

- Introduction

- Challenges

- Site Flatness and Nanotopography

- Particle Size

- Wafer Edge Exclusion / Roll-Off

- 450 mm Diameter Wafers

- Opportunities

- SOI

- Strained Silicon (and Ge)

- Hybrid Structures

- Actions

SEMATECH

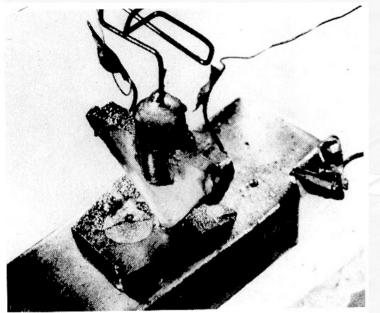

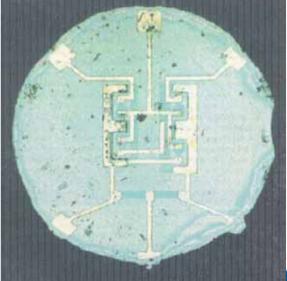

## **Transistors to Integrated Circuits**

Used with permission of the Estate of John Bardeen

Courtesy of Texas Instruments, Inc.20052005 International Conference

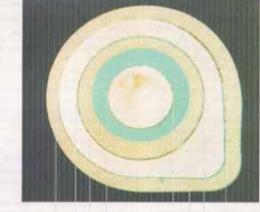

Reproduced by Permission of the IEEE, Inc.

Reproduced by Permission of the IEEE, Inc.

March 17, 2005

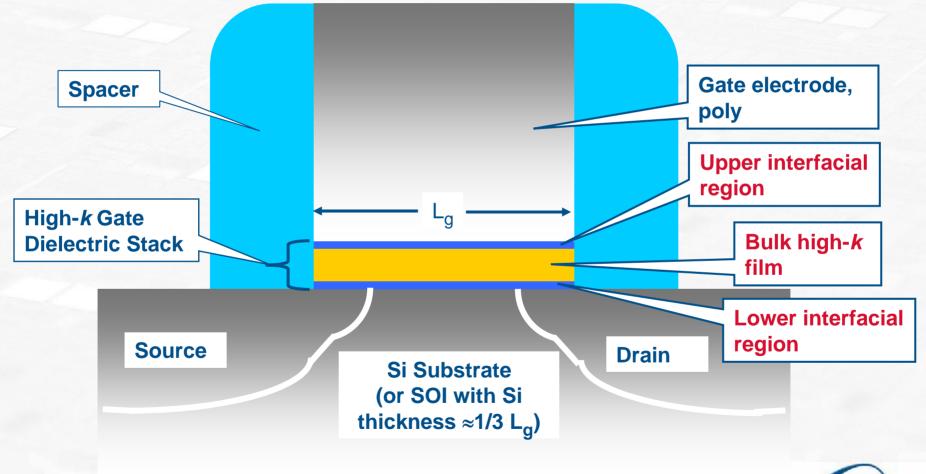

#### Simplified Cross-Section of MOSFET Transistor Structure

Modified From P.M. Zeitzoff, R.W. Murto and H.R. Huff, Solid State Technology, July 2002

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology A

Accelerating the next technology revolution.

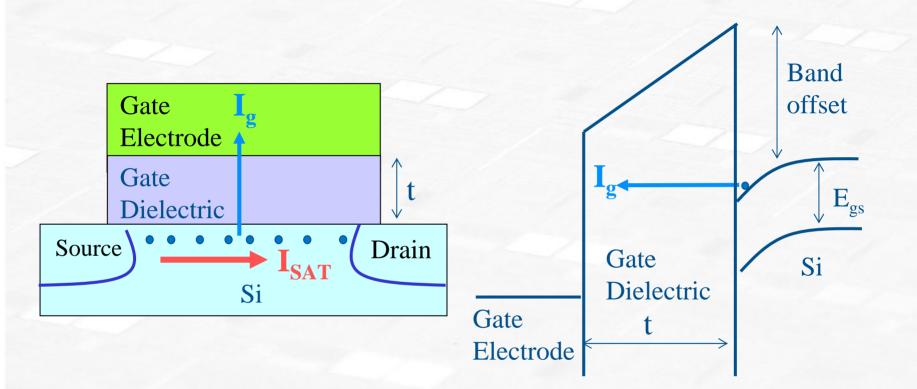

## **Transistor Scaling**

<u>Requirement</u>: Increase Isat  $\propto \mu \cdot \epsilon / t$  without increasing Ig  $\propto \exp(-t\phi^n)$

March 17, 2005

## Agenda

- Introduction

- Challenges

- Site Flatness and Nanotopography

- Particle Size

- Wafer Edge Exclusion / Roll-Off

- 450 mm Diameter Wafers

- Opportunities

- SOI

- Strained Silicon (and Ge)

- Hybrid Structures

- Actions

SEMATECH

#### Site Flatness and Nanotopography

- Appears 25 mm x 25 mm site still relevant trend

- SFSR still not standardized or widely accepted / used

- Bi-modal distribution of SFQR (survey result)

- SFQR ≈ technology generation

- SFQR significantly relaxed (≈ 40% larger than technology generation)

- Determination of nanotopography criticality

- Dipole characteristic, IDMs either very interested or not interested at all

#### **Critical Starting Materials: New Issues**

#### Chuck – Wafer Flatness Interaction

- Nature of chuck-wafer interaction is a 3-D challenge, especially dependent on leveling mechanism of chuck and chuck design in edge region, the latter affecting ability to obtain zero defocus

- Wide range of wafer chucks makes it virtually impossible for wafer suppliers to implement 100% chucked-wafer measurement

- · Wear of chucks in fabs exacerbates chuck flatness /chuck-wafer interaction

- Recommend further discussion of relevant issues through SEMI

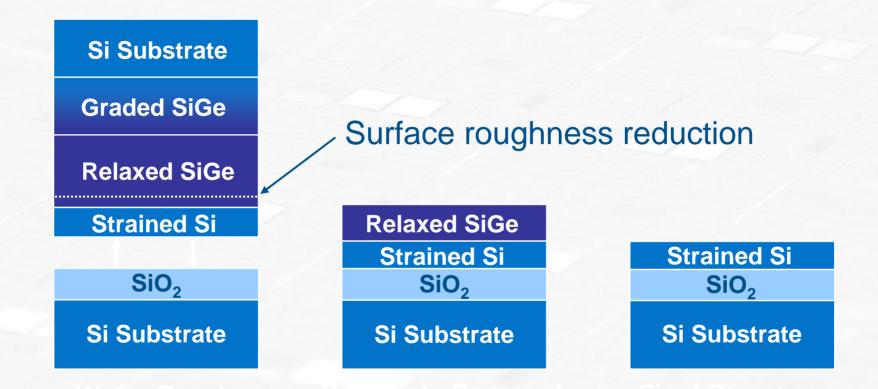

- Emerging Materials Focus (in 2003 ITRS revision)

- Novel structures and processing methods to enhance silicon-based CMOS technology to achieve ITRS device metrics

- Strained silicon and its embodiments (metrology)

- Bulk strained Si (on uniform SiGe on compositionally graded SiGe)

- Strained Si on uniform SiGe on Insulator (SGOI) partially / fully depleted

- Strained silicon on insulator (SSOI) or Ge partially / fully depleted

- Other areas under consideration include Ge MOSFET structures, highresistivity silicon, isotopically pure silicon and integrated optoelectronics on silicon

March 17, 2005

#### Particle Size Reduction – Some User Input

- "Folly to reduce particle size to ½ technology generation

- Absolute nonsense from many points of view, including necessity and metrology

- Surface preparation should increase their size to one technology generation (or even larger)"

- "Numerous process steps leading to pre-gate level exceptionally convoluted

- Incoming wafer may play only a limited role in performance

- Beyond actual processing steps which offer ready particle sources, effect of in-line metrology cannot be discounted

- Although same piece of silicon enters process, it clearly changes over time

- From Starting Materials perspective, not obvious that two teams must publish equivalent trends in ITRS tables

- Many existence proofs, based upon actual customer specifications, particles ≥ one technology generation ample to meet requirements"

#### **Nevertheless**, Surface Preparation claims IDMs indeed need / require particle size = ½ technology generation

## **Defect Density Challenges**

- Assess viability of continued utilization of Maly equation to calculate defect density, kill ratio assumption as well as identification of appropriate kill ratio

- $Y = exp [-D_P R A_{Active Chip}]$

- Viability of utilizing square law relation

- $D_2 / D_1 = (\text{Tech. Gen.}_1 / \text{Tech. Gen.}_2)^2$

- Should we list values of defects appropriate to variously configured SOI and other Emerging Material structural configurations?

Some guidance and trends appear to be useful

March 17, 2005

#### **Critical Starting Materials** (Old Issue Re-Addressed)

#### Surface Preparation sub-TWG has noted

- Starting Materials methodology of increasing particles and metals (by 2x the Maly derived value) enhances expectation that Surface Preparation can surely remove these increased levels

- Wrong message may be sent to suppliers of cleans equipment who have to deal with in-line (pre-gate) requirements (i.e., Surface Preparation) and yet work with wafers that are "looser" in incoming metal and particle levels

#### Wafer Edge Exclusion

- Edge exclusion (EE) needs to be consistent for Starting Materials, Yield Enhancement and Factory Integration(FI)

- ITRS Governing Body decision:

- Factory Integration decides EE die/wafer

- Some types of SOI structures are currently incapable of achieving the 1mm EE mandated by FI

- ITRS denotes what perceived to be needed, even if tool is not yet available, per se

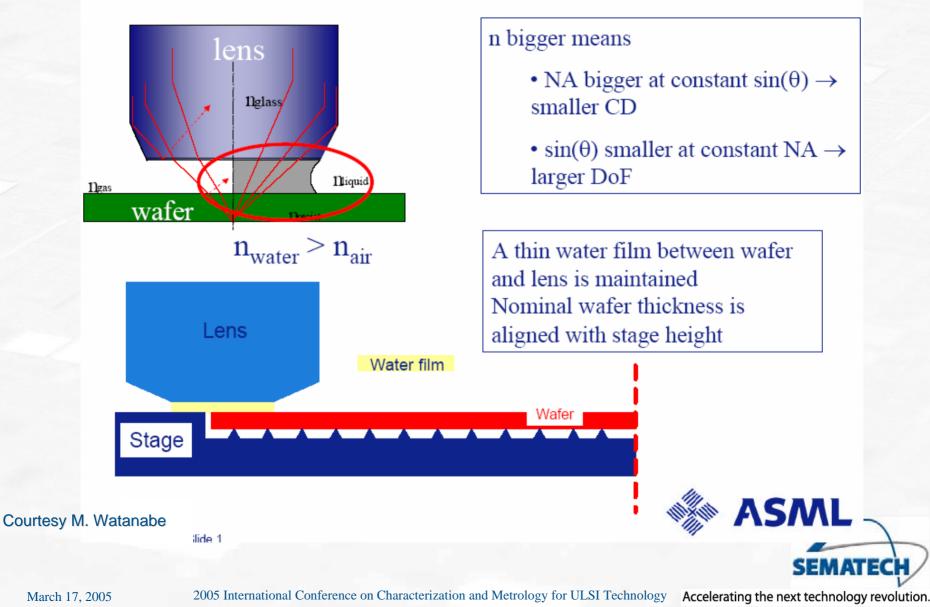

#### Wafer Roll-Off – Possible Impact on NGL

#### **Immersion Lithography Concept**

#### Wafer Roll-Off

#### Wafer edge thickness variation

March 17, 2005

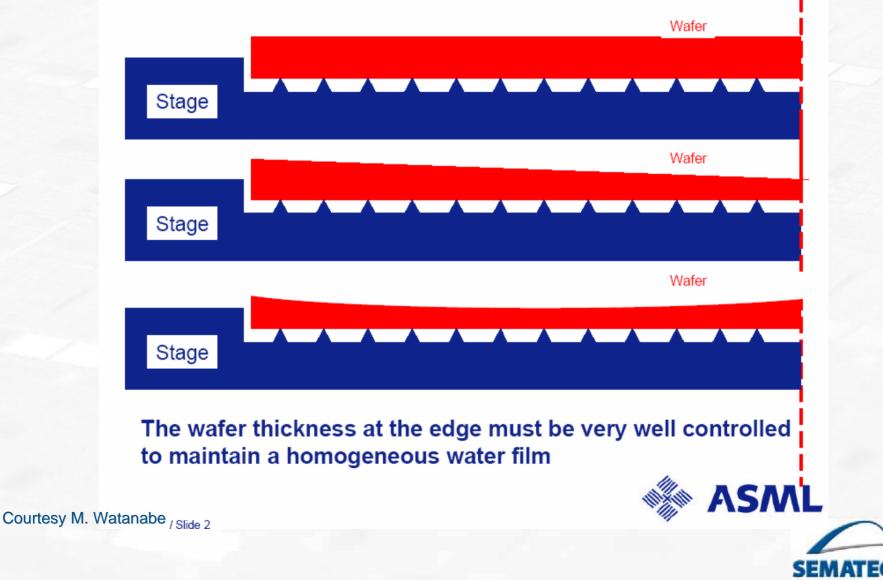

#### Wafer Roll-Off

#### Conclusions

- SEMI specifications for 300mm wafers:

- Thickness, center point: 775 um +/- 20um

- Total Thickness Variation (GBIR) max: 10um

- This yields a maximum edge height variation of +/- 30um

#### **Question:**

/ Clide 2

Can this edge height variation be reduced?

Courtesy M. Watanabe

SEMATECH

March 17, 2005

Periodic wafer diameter increases key element in remaining on Moore's law

- "When the wafer area increases by >2 times, but the cost of the new tool set for the same number of wafer starts increases by only 30-40% (which is typical), the cost per area decreases by 30-50% -- an annualized improvement of ~4% when wafer size changes occur about every 10 years."

R. Goodall, D. Fandel, A. Allan, P. Landler, and H. Huff, Semiconductor Silicon/2002, ECS PV 2002-2, 125-143 (2002)

D. Myers, Microelectronic Materials Strategy Symposium, SEMI, San Jose, CA, 9/24/02.

However, it is also imperative to be cognizant of starting wafer cost as the expected timing of transition may intersect ITRS at a point where non-standard material types are predominant

- Very useful to maintain two year technology cycle

- Migration to three year technology cycle may be likely

- Will nanotechnology-based manufacturing paradigm facilitate off-the-roadmap perspective and obviate 450mm diameter perceived need

- Extrapolation forward (business as usual) hoping world not change

- Need further assessment of assumptions related to perceived wafer diameter change

- Nine year wafer diameter development cycle previously noted

- Therefore, we may already be somewhat behind for 2011 450mm diameter wafer assessment at IDMs

- Assess potential alternatives to wafer diameter change

- Role / impact of emerging technologies requires consideration

- 450mm anticipated to present severe financial crisis for silicon and equipment suppliers

- Changes in functionality of automated material handling system (AMHS) not fully comprehended

- Although ITRS fundamental technology trend guide for industry, it does not directly address economic factors

- Consequence of strict adherence to historic trends without utmost due diligence represents clear issue to viability of IC industry

#### **Connecting Economic & Technology Challenges**

Industry strategy for next wafer size transition to include:

- Initial concepts for fab design, operations, and integration

- Supply chain impact and key intercept points

- Timing & cost of transition

- ISMI View, based on Member Company feedback (July-04)

- Further modeling and analysis needed

- Must leverage all TWGs addressing the issue

- Too early for substantial resource commitments

ISMI

#### Is 2012 appropriate for 450mm / how funded?

- How and when will issue(s) and decision(s) be resolved

- Need further discussion and more serious consideration for alternative solutions to productivity enhancement

- Fundamental diameter issues addressed by ITRS Tables are for 300 mm but MANY IDM's have announced aggressive geometry production on 200mm (90 nm technology generations and potentially beyond)

- If SOI and 450mm both become necessary at about same time things could become very interesting

- May be unlikely, however, since SOI seems more poised for implementation than 450mm (and is indeed impacting available wafer substrate types in market-place)

### **Learnings From 300mm Experience?**

- Establish earlier consensus on fab architecture & operations

- One company driving strategy is suboptimal

- Need to comprehend wafer size bridging in toolset

- Drive business models and architectural strategies

- Leave supply chain pricing to the market

- Develop standards early to reduce costs

- Support multiple leading-edge operational modes

- High-volume/low-mix, High-volume/high-mix, etc.

- Continuously evaluate and adjust, including:

- Impact of technology on next wafer size transition timing

- Tradeoffs and timing using modeling and simulation tools

- Industry coordination is crucial and valuable

March 17, 2005

ISMI

#### **Critical Starting Materials: New Issues**

#### Chuck – Wafer Flatness Interaction

- Nature of chuck-wafer interaction is a 3-D challenge, especially dependent on leveling mechanism of chuck and chuck design in edge region, latter affecting ability to obtain zero defocus

- Wide range of wafer chucks makes it virtually impossible for wafer suppliers to implement 100% chucked-wafer measurement

- Wear of chucks in fabs exacerbates chuck flatness /chuck-wafer interaction

- Recommend further discussion of relevant issues through SEMI

#### • Emerging Materials Focus (in 2003 ITRS revision)

- Novel structures and processing methods to enhance silicon-based CMOS technology to achieve ITRS device metrics

- Strained silicon and its embodiments (metrology)

- Bulk strained Si (on uniform SiGe on compositionally graded SiGe)

- Strained Si on uniform SiGe on Insulator (SGOI) partially / fully depleted

- Strained silicon on insulator (SSOI) or Ge partially / fully depleted

- Other areas under consideration include Ge MOSFET structures, highresistivity silicon, isotopically pure silicon and integrated optoelectronics on silicon

March 17, 2005

## Agenda

- Introduction

- Challenges

- Site Flatness and Nanotopography

- Particle Size

- Wafer Edge Exclusion / Roll-Off

- 450 mm Diameter Wafers

- Opportunities

- SOI

- Strained Silicon (and Ge) Global versus Local

- Hybrid Structures

- Actions

SEMATECH

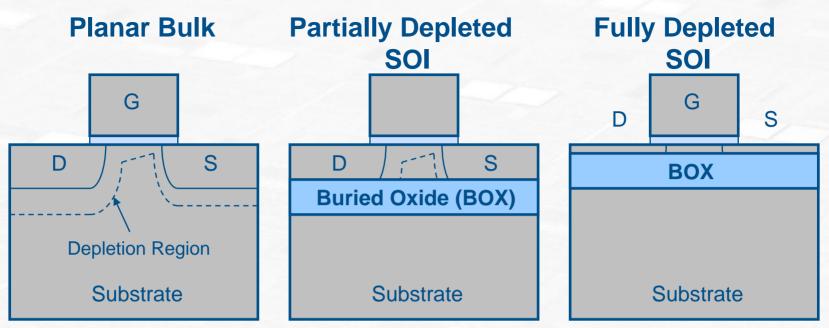

#### **Transistor Structures**

#### + Wafer cost / availability

- SCE scaling difficult

- High doping effects and statistical variation

- Parasitic junction capacitance

+ Lower junction cap

- + F.B. performance boost

- F.B. history effect

- SCE scaling difficult

- Wafer cost/availability

#### + Lower junction cap

- SCE scaling difficult

- High R<sub>series.s/d</sub>⇒raised S/D

- Sensitivity to Si thickness (very thin)

- Wafer cost/availability

1. P. Zeitzoff, J. Hutchby and H. Huff, Internat. Jour. High Speed Electronics & Systems

2. Mark Bohr, ECS Meeting PV 2001-2, Spring, 2001

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

E E C

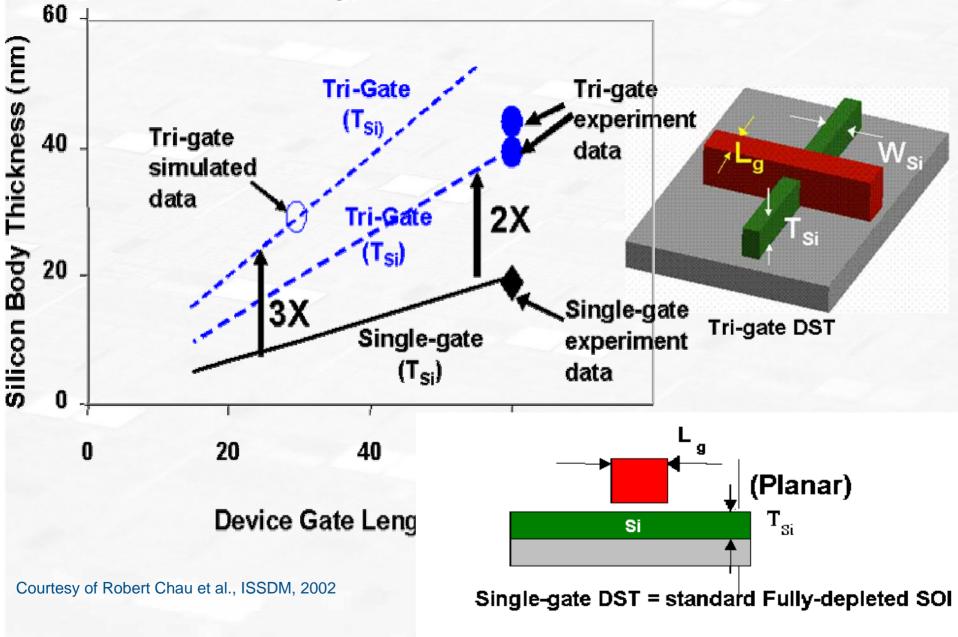

#### **Tri-gate Relaxes T<sub>Si</sub> Requirement of Single-gate**

March 17, 2005

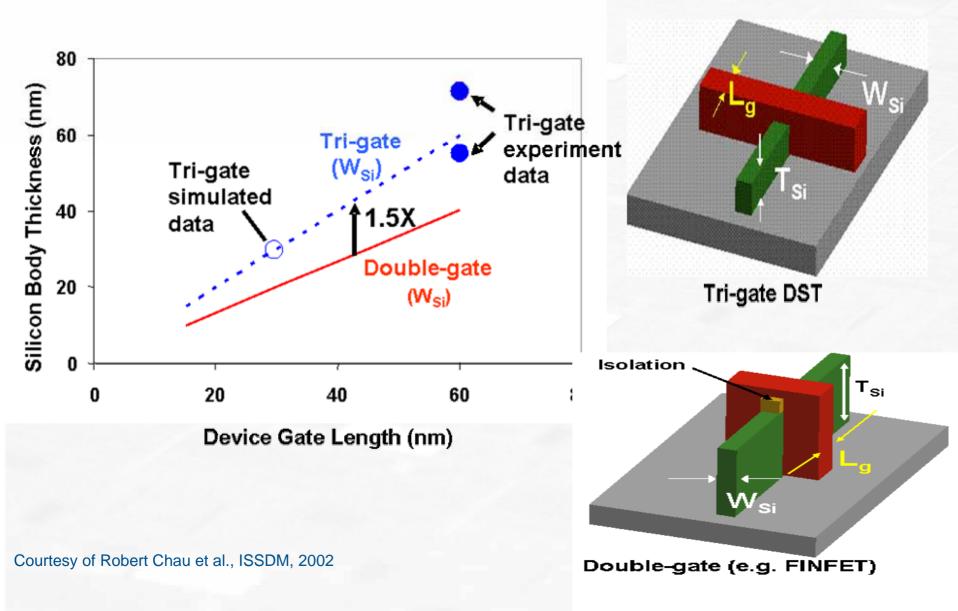

#### **Tri-gate Relaxes W<sub>Si</sub> Requirement of Double-gate**

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

1

#### **Potential Solutions: 2004 Update** Changed SOI to clear colorization in 2004 and cross-hatched shading in 2006 to ensure consistency with commercial reality

| First Year of IC Production                                     | 2003<br>100 nm | 2004<br>90nm                                                           | 2005<br>80nm | 2006<br>70nm |                           | 2008<br>57nm | 2009<br>50nm |           |         |                                                                                                     | 2013<br>32nm |        |        |        | 2017<br>20nm |        | 2019 |   | 123 |   |

|-----------------------------------------------------------------|----------------|------------------------------------------------------------------------|--------------|--------------|---------------------------|--------------|--------------|-----------|---------|-----------------------------------------------------------------------------------------------------|--------------|--------|--------|--------|--------------|--------|------|---|-----|---|

|                                                                 |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     | / |

| 300mm Leading Edge                                              |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Materials Selection                                             |                |                                                                        |              | _            |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Defect Engineered                                               |                |                                                                        |              | _            |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| CZ Wafers include:<br>• P/P+ and P/P++ epi                      | -              | Z Wafe                                                                 | -            | -            |                           |              | /            |           | -       |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| • P/P+ and P/P++ epi<br>• P/P- epi                              |                | Defect-engineered<br>CZ Wafers                                         |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Annealed Wafers                                                 |                | CZW                                                                    | aters        |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Slow pull/slow cool                                             |                |                                                                        |              | -            |                           | /            | /            | /         |         | /                                                                                                   | <u>/</u>     |        |        | _      |              | _      |      |   |     |   |

|                                                                 | _              | Emerging Materials (Strained materials/layers, high resistivity, etc.) |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        | -            |        |      |   |     |   |

| SOI includes:                                                   |                | (Stra                                                                  | unea m       | ateria       | is/laye                   | nis, nig     |              | suvity, e | N.      | <u> </u>                                                                                            |              |        |        |        |              |        |      |   |     |   |

| Bonded Wafers                                                   | 0.01           | 0                                                                      | 01           |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| SIMOX Wafers                                                    | SOI<br>Wafers  | Wa                                                                     | 8            |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Selective SOI areas                                             | Warers         | VVa                                                                    | leis         |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| w ithin the IC chip                                             |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| lefe a Diama ta a                                               | 450            | mm                                                                     |              |              | 450                       | mm           |              |           |         |                                                                                                     |              |        | 450 m  | m      |              |        |      |   |     |   |

| <u>Vafer Diameter</u>                                           |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 | Alterna        | tives to                                                               | large-       | (In o        | Includes novel substrates |              |              |           | 675 m m |                                                                                                     |              |        | 675 mm |        |              |        |      |   |     |   |

|                                                                 |                | Alternatives to large-<br>Diameter Si Wafers and new circuit appro     |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 |                |                                                                        |              | anu          |                           |              | ppilat       |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| ite Flatness                                                    |                |                                                                        |              | _            |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| ite Flathess                                                    | Dou            | ble-sic                                                                | ded Pol      | ish          |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 |                |                                                                        | New          |              |                           |              | New          |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 |                | Tech-                                                                  |              |              |                           |              | Tech-        |           |         | New Technology (Includes CMP; Orientation Dependent Etch;                                           |              |        |        |        |              |        |      |   |     |   |

|                                                                 | _              | nology                                                                 |              |              |                           |              |              |           |         | Localized Etch; Localized Deposition + blanket etch or CMP;<br>Blanket layer + blanket etch or CMP) |              |        |        |        |              |        |      | _ |     |   |

|                                                                 | _              |                                                                        | lology       |              |                           |              | lineiegy     |           | Dialike | t layer                                                                                             | - Dialine    |        |        |        |              |        | 1    |   |     |   |

| bio lowand indicates the time durin                             | a which a      |                                                                        | daval        |              |                           |              | ficatio      |           |         | i'n n ok                                                                                            |              | ki     |        |        | h            |        |      |   |     |   |

| <b>his legend indicates the time durin</b><br>Research Required | y which re     | searci                                                                 | i, devel     | opinei       | n, anu                    | quan         | licatio      | n/pre-p   | nouuc   | tion si                                                                                             | oura         | elakii | ny pra | Leiori | ne son       | ation. |      |   |     |   |

| evelopment Underway                                             |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| ualification / Pre-Production                                   |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

| Continuous Improvement                                          |                |                                                                        |              |              |                           | -            |              |           | -       |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

|                                                                 |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     | - |

| -                                                               |                |                                                                        |              |              |                           |              |              |           |         |                                                                                                     |              |        |        |        |              |        |      |   |     |   |

SEMATEO

## SOI

- SOI implementation will at some point become necessary to solve leakage issues that are limiting further reductions in feature size

- There will be a point at which it will not be possible to maintain shrink progression that enables Moore's Law, without SOI

- Becomes a "timing" issue because there is question as to exactly when that point will come—as a matter of physics, economics, and technological readiness

#### SOI

- Economic issues are price of SOI wafers and timing that each IC company uses for SOI implementation

- Ideally should be implemented somewhat before becomes physically impossible to otherwise progress, because there

[is] a learning curve involved in maximizing its yield

- Technological readiness issues have to do with capabilities of SOI wafers, for example metrology limitations / film thickness uniformity concerns

- Resolution of some issues depend on device structures (i.e., FinFET) required when SOI becomes imperative

- Therefore, very important for industry to have an accurate forecast of which technology node will absolutely require SOI, from a physics standpoint

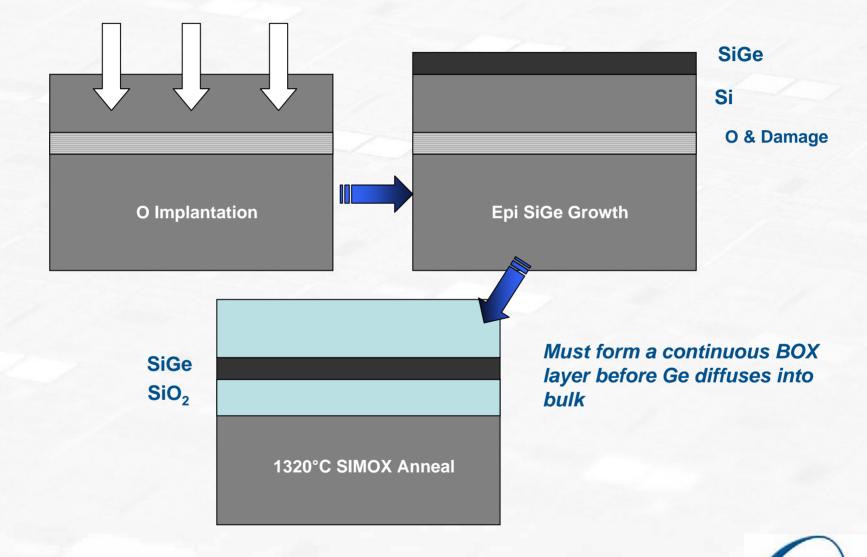

#### **Methods of Forming Strained Si / SGOI**

#### Bonding and Layer Transfer

#### Thermal Mixing of SiGe with SOI

#### Integrated SIMOX-SGOI

Sadana / Current, SOI Technology Symposium, Oct. 18, 2004

March 17, 2005

## **SSOI Substrate Fabrication Process**

#### Starting material quality critical to process

March 17, 2005

## **Integrated SIMOX and SGOI Process**

Sadana / Current, SOI Technology Symposium, Oct. 18, 2004

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

TEC

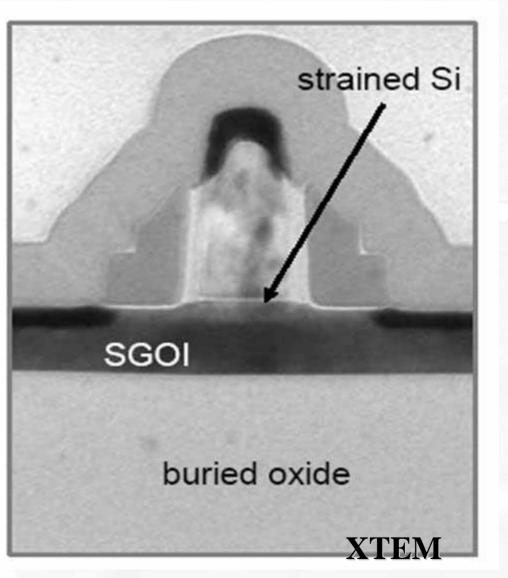

## 300 mm SGOI/Strain-Si FET

Sadana / Current, SOI Technology Symposium, Oct. 18, 2004

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

ATEC

# Strained Silicon Motivation: Mobility $\mu = |e| \tau / m^*$ |e| = absolute value of electronic charge $- \tau = scattering rate$ $- m^* = effective mass$

$\mu = \delta v / \varepsilon$

## $\delta v = incremental speed gained per applied electric field <math>\epsilon$

March 17, 2005

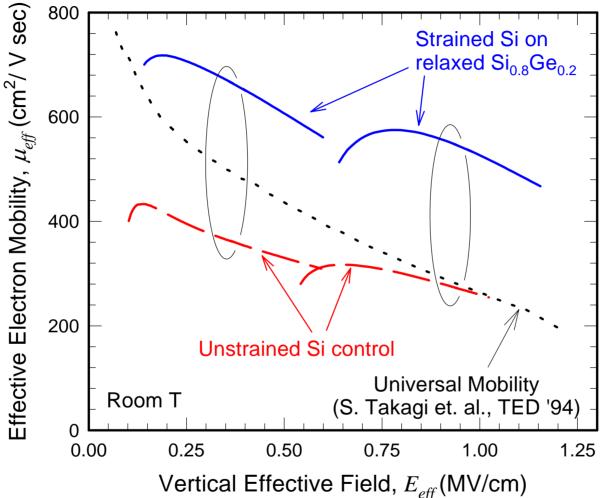

#### Electron Mobility Enhancement in Strained Si MOSFETs (Rim.et al., IEDM 1998)

Electron mobility enhancement of ~ 1.8X persists up to high E<sub>eff</sub> (~ 1MV/cm)

Strained-Si allows "moving off" universal mobility curve

Judy Hoyt, MIT

March 17, 2005

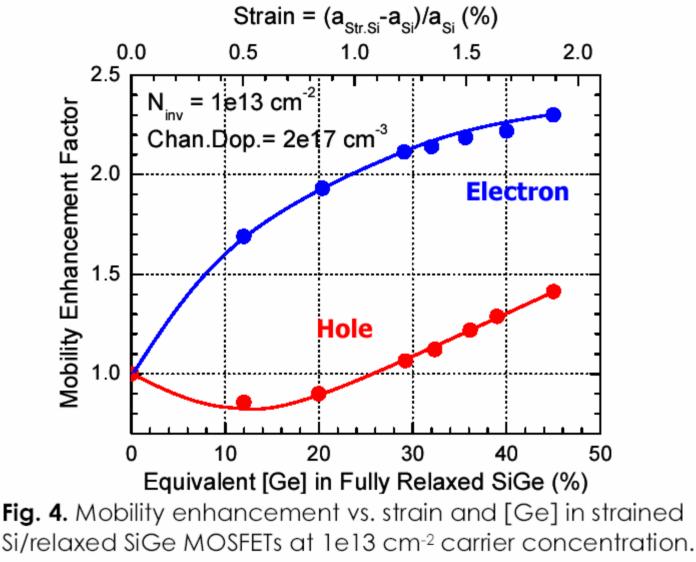

#### **Strain Effect on Carrier Mobility**

Hole mobility enhancement requires large amount of strain.

IBM, Rim et al, IEDM, Tech Dig, p. 49 (2003)

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

EC

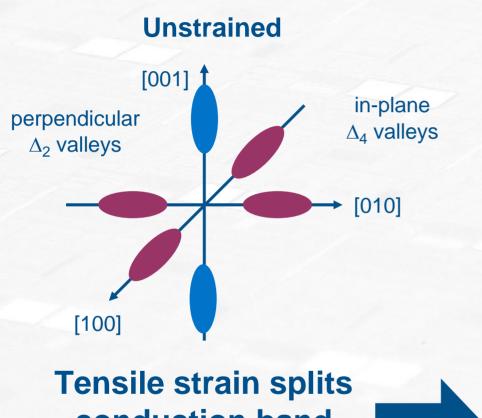

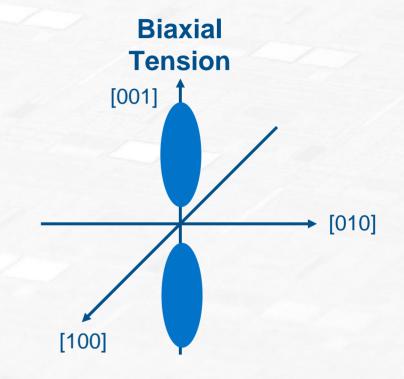

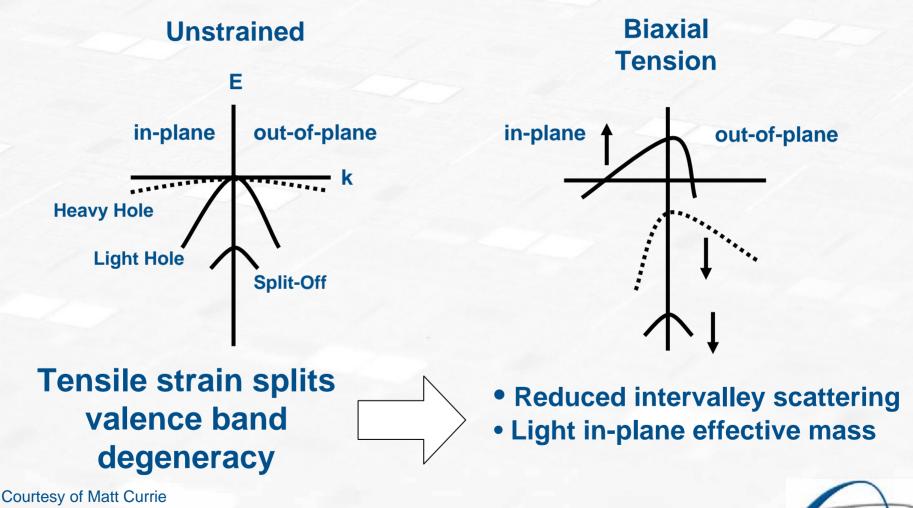

### **Electron Transport in εMOS™**

#### Tensile strain splits conduction band degeneracy

Courtesy of Matt Currie AmberWave Systems Corp.

# Reduced intervalley scattering Light in-plane effective mass

March 17, 2005

### **Hole Transport** in ε**MOS**<sup>™</sup>

AmberWave Systems Corp.

March 17, 2005

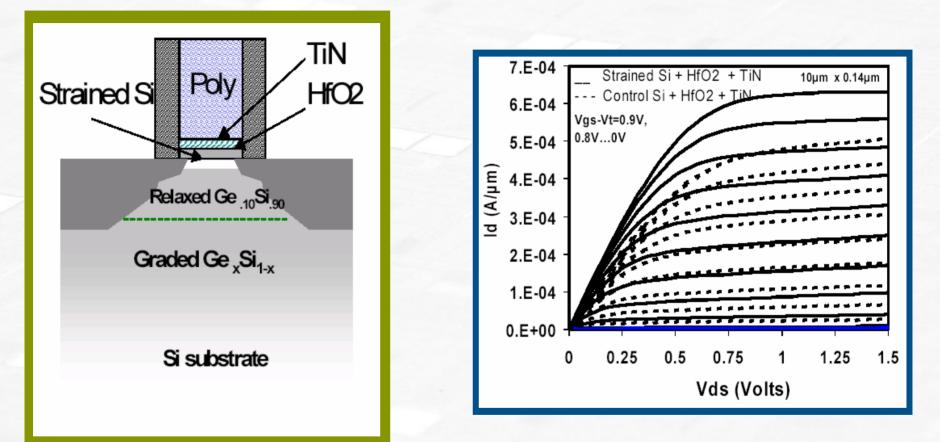

### **Key Strained Si Performance Results**

- Many manufacturers have reported performance enhancements with strained Si

- IBM, AMD, UMC, TSMC, Texas Instruments, Toshiba, Intel

- Strained silicon provides higher speed, lower power transistors than bulk silicon

- Compatibility with 45 nm 130 nm DRs (depending on structure and device)

- Integrated with high K and metal gate

- Benefits for RF application

- 20%  $I_{d,sat}$  enhancement demonstrated for  $L_g = 25$  nm

- > 30% ring oscillator performance enhancement reported

March 17, 2005

### Integration with High K and Metal Gate

#### **24% DC I**<sub>d,sat</sub> enhancement with good matching of V<sub>t</sub> and subthreshold

INTEL, Datta, et al, IEDM, Tech. Dig., p. 653 (2003)

March 17, 2005

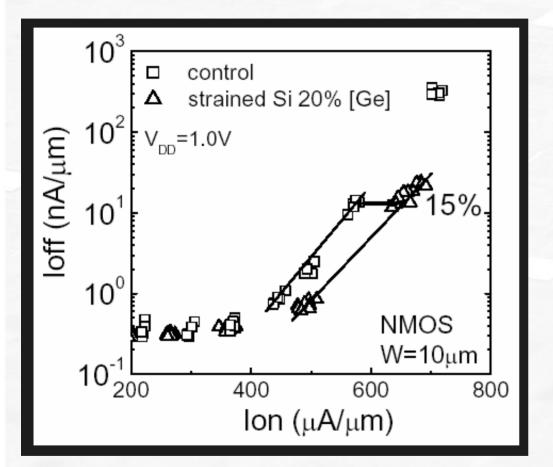

# NMOS Ion-Ioff Benefit

L<sub>gate</sub> down to 60nm 1.7 nm EOT

**15% DC enhancement** largest ever reported

Correction for self heating adds approximately 10% more enhancement

TSMC, Wang et al, IEDM, Tech. Dig., p. 61 (2003)

March 17, 2005

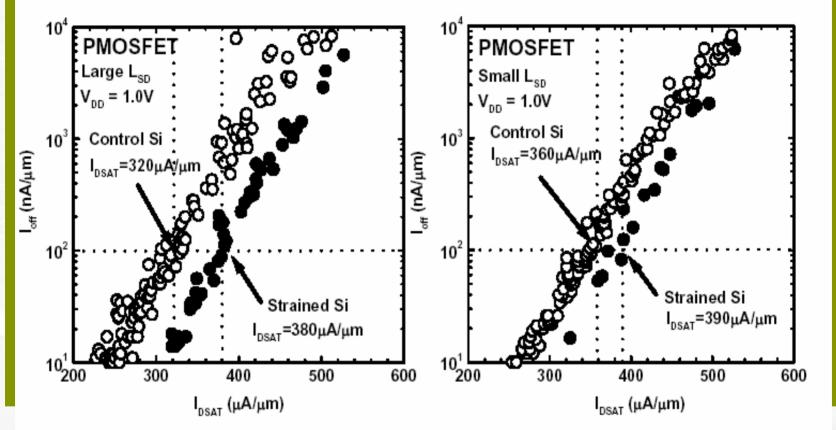

### PMOS Ion-Ioff Benefit

11-19% enhancement due to strained Si

SEMATECH

Toshiba, Sanuki et al, IEDM, Tech. Dig., p. 65 (2003)

March 17, 2005

March 17, 2005

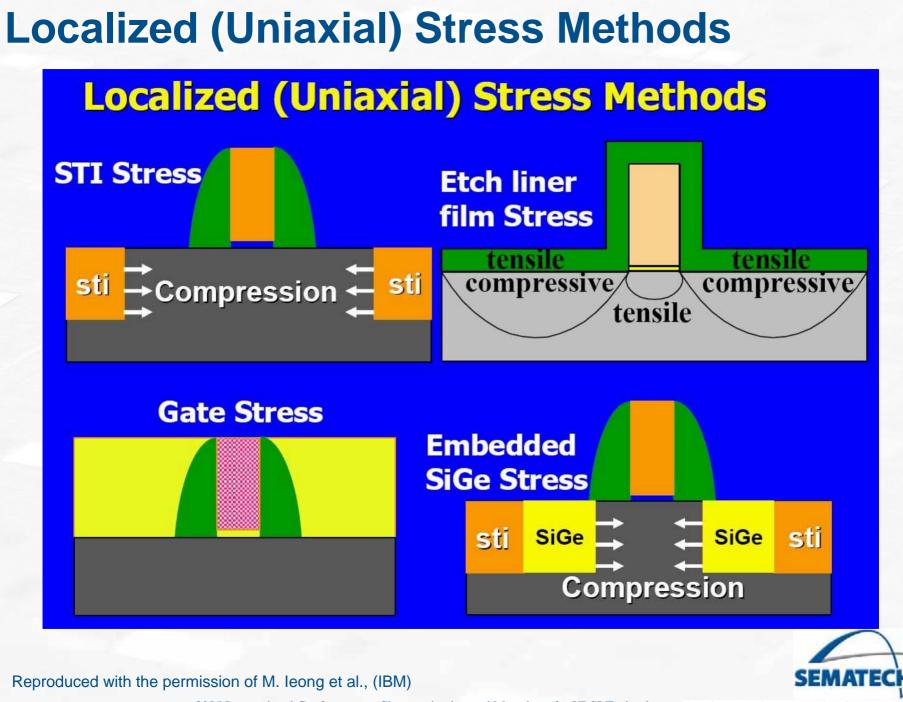

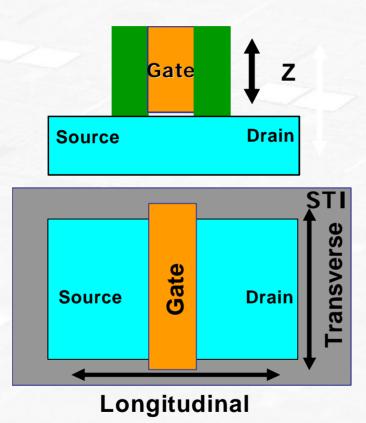

### **Tensile / Compressive Stress Relations**

#### Desired Stress:

|      | Tran. | Long. | Z |

|------|-------|-------|---|

| pFET | Т     | С     | Т |

| nFET | Т     | Т     | С |

T: Tensile stress C: Compressive stress

Dependence of device performance on the types and directions of uni-axial stresses. Reproduced with the permission of M. leong et al., (IBM) and The Electrochemical Society, Inc.

March 17, 2005

# Agenda

- Introduction

- Challenges

- Site Flatness and Nanotopography

- Particle Size

- Wafer Edge Exclusion / Roll-Off

- 450 mm Diameter Wafers

- Opportunities

- SOI

- Strained Silicon (and Ge)

- Hybrid Structures

- Actions

SEMATECH

March 17, 2005

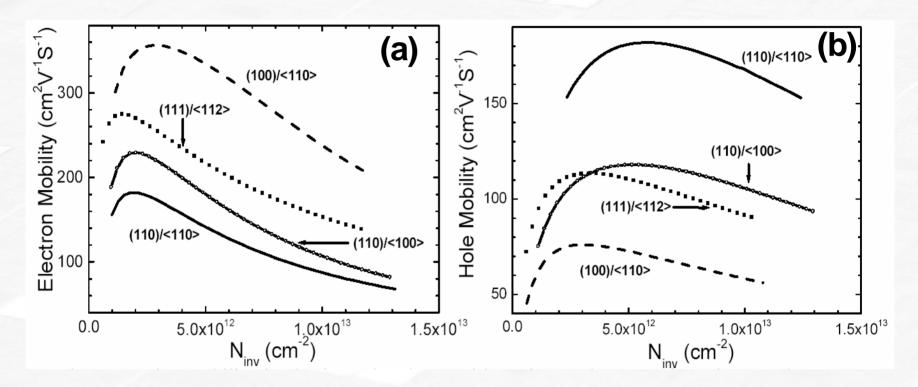

#### **Orientation Effect on Effective Electron and Hole Mobility**

Orientation effect on the (a) effective electron mobility, (b) effective hole mobility as a function of inversion carrier density. Electron mobility is the highest on the (100) surface while the hole mobility on the (110) surface is more than 2.5 times higher than that on the (100) surface. Reproduced with the permission of M. leong et al., (IBM) and The Electrochemical Society, Inc.

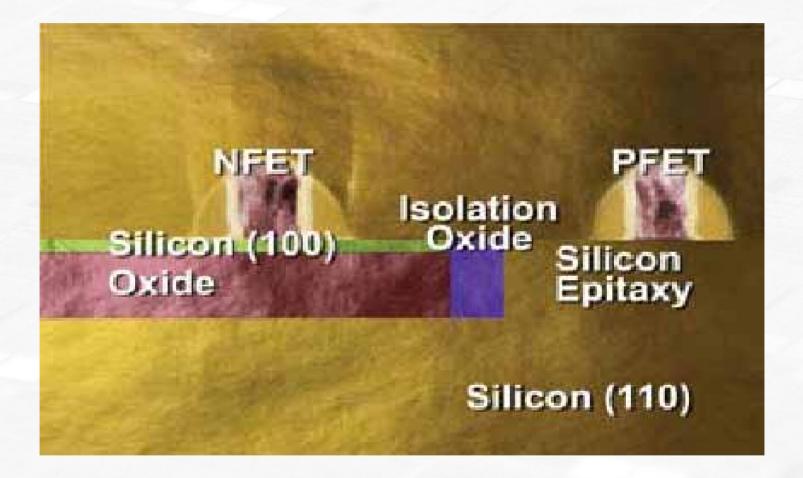

### **Hybrid OrientationTechnology**

Hybrid Orientation Technology (HOT). PFET on (110) surface and nFET on (100) surface. Planar structure, fully compatible with standard CMOS processes. Reproduced with permission of Min Yang et al., (IBM) and the IEEE (© 2003 IEEE).

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

TEC

# Agenda

- Introduction

- Challenges

- Site Flatness and Nanotopography

- Particle Size

- Wafer Edge Exclusion / Roll-Off

- 450 mm Diameter Wafers

- Opportunities

- SOI

- Strained Silicon (and Ge)

- Hybrid Structures

- Actions

March 17, 2005

### Actions

- Assess updated survey responses from IDMs for 2005 ITRS

- 1:1 dialogue with silicon suppliers to ensure integrity of silicon and SOI suppliers cell colorization and manufacturing capability

- Significant loss of silicon mtl's expertise in IDMs due to evolving industrial focus on IC scaling

- Silicon suppliers expected to fill required research

- Silicon suppliers are resource and extremely financial limited

- 'Silicon still substrate for building these [nonclassical CMOS] devices'\* although many components inside CMOS-like transistors will be very different, including many manufacturing processes

<sup>^</sup> Ken David (Intel)

March 17, 2005

#### **Acknowledgements**

- Surface Preparation, Thermal / Thin Films, PIDS, Yield Enhancement and Factory Integration ITRS TWGs

- ISMI personnel at SEMATECH

March 17, 2005

# **Supplemental Material**

March 17, 2005

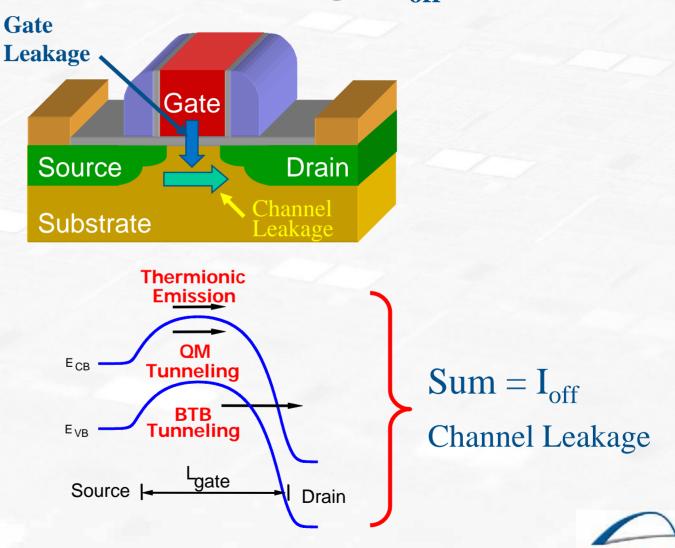

### Electrostatic Scaling of Classical CMOS Channel Leakage (I<sub>off</sub>)

Jim Hutchby

March 17, 2005

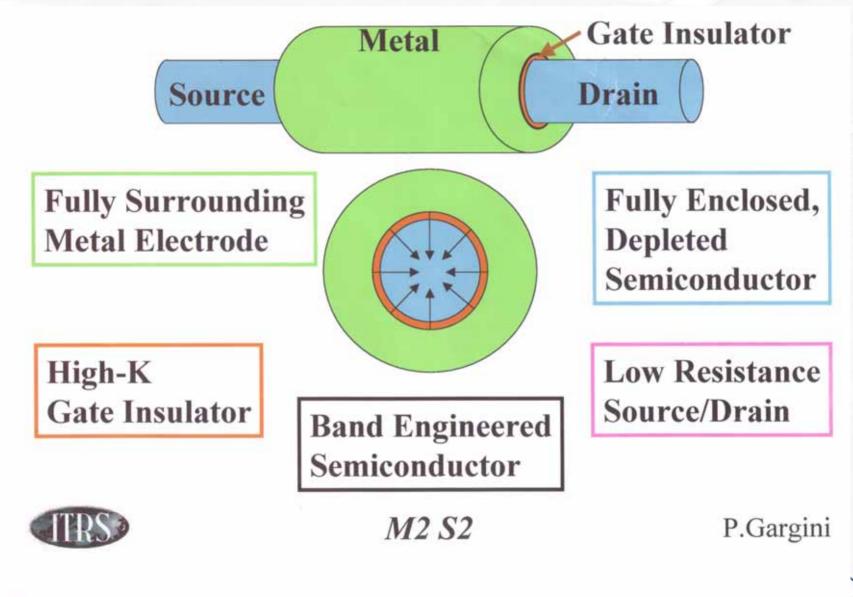

### **The Ideal MOS Transistor**

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelerating the next technology revolution.

SEM

### Non-classical CMOS does not include:

#### Classical CMOS : planar bulk CMOS / partially depleted SOI

- Materials, processes and device structures used since 1980's with extensive scaling (per Moore's Law)

- Beyond-CMOS devices: fabricated with unique, non-Si material or utilizing non-MOSFET operation

- Single-electron transistor, quantum cellular array, neuromorphic, molecular, fullerenes, carbon nanotubes, or optical materials, etc.

- Expected beyond time period of current ITRS.

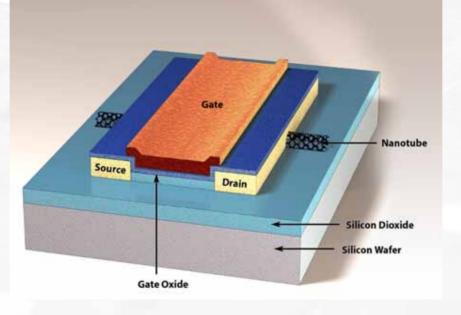

Nanotube FET [IBM]

March 17, 2005

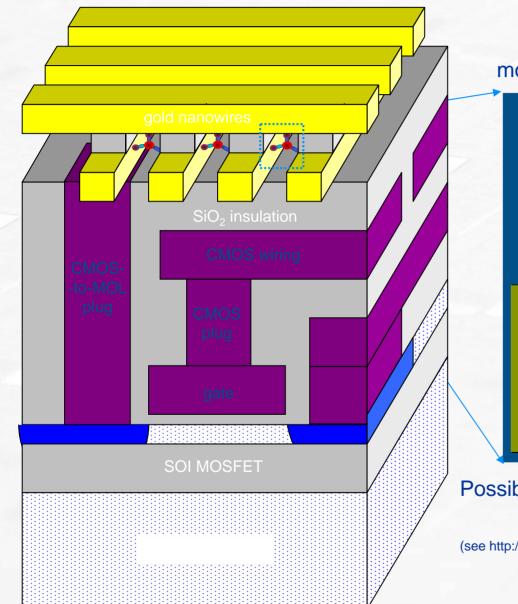

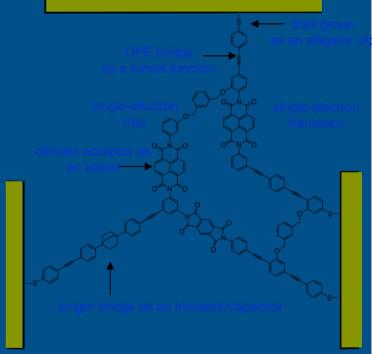

### **CMOL CONCEPT**

molecular single-electron latching switch

Possible density: 3×10<sup>12</sup> functions per cm<sup>2</sup>

K. Likharev and A. Mayr, 2002

(see http://rsfq1.physics.sunysb.edu/~likharev/nano/GigaNano010603.pdf)

March 17, 2005

### **Microelectronics Revolution**

#### Gordon Moore (a)

- "But then you see the numbers or hear your company's name on the evening news ... and you are once again reminded that this is no longer just an industry, but an economic and cultural phenomenon, a crucial force at the heart of the modern world."

#### Gordon Moore (b)

– "No exponential is forever: but "forever" can be delayed!"

(a) Beyond Imagination:Commemorating 25 Years, SIA (2002) [Introduction by Gordon Moore](b) ISSCC 2003 / Session 1/ Plenary 1.1 (2003)

March 17, 2005

#### **Gordon Moore**

March 17, 2005

#### **John Bardeen**

SEMATECH

Courtesy of Lillian Hoddeson

March 17, 2005

# **Bob Dennard**

March 17, 2005

2005 International Conference on Characterization and Metrology for ULSI Technology Accelera

Accelerating the next technology revolution.