#### Multilevel DC Link Inverters Submitted to the IEEE IAS 2002 Annual meeting

## Multilevel DC Link Inverters

Gui-Jia Su and Donald J. Adams Oak Ridge National Laboratory, Oak Ridge, TN, U.S.A.

### Abstract\*

This paper presents a new class of multilevel inverters based on a multilevel dc link (MLDCL). An MLDCL can be a diode-clamped phase leg, or a flying capacitor phase leg; or it can be constructed by connecting in series a number of half-bridge cells, each having its own dc source. A multilevel voltage source inverter can be formed by connecting an MLDCL with a single-phase bridge inverter. The MLDCL provides a dc voltage with the shape of a staircase, with or without pulse width modulation, to the bridge inverter, which in turn alternates the polarity to produce an ac voltage. Compared with the cascaded H-bridge, diode-clamped, and flying capacitor multilevel inverters, the MLDCL inverters can significantly reduce the switch count as the number of voltage levels increases beyond five. For a given number of voltage levels, m, the required number of active switches is  $2 \times (m-1)$  for the existing multilevel inverters but is m+3 for the MLDCL inverters. The operating principles of the MLDCL inverters and design guidelines are included.

Corresponding Author: Gui-Jia Su

National Transportation Research Center

Oak Ridge National Laboratory

2360 Cherahala Blvd. Knoxville, TN 37932

**USA**

Phone (865) 946-1330, Fax (865) 946-1262

Email: sugi@ornl.gov

Prepared by Oak Ridge National Laboratory, managed by UT-Battelle, LLC, for the U.S. Dept. of Energy under contract DE-AC05-00OR22725.

The submitted manuscript has been authored by a contractor of the U.S. Government under contract DE-AC05-00OR22725. Accordingly, the U.S. Government retains a nonexclusive, royalty-free license to publish or reproduce the published form of this contribution, or allow others to do so, for U.S. Government purposes.

## Multilevel DC Link Inverters

# Digest

#### I INTRODUCTION

Traditionally, GTO-based two-level inverters were the choice for medium- or high-voltage level applications such as motor drives and static var compensation. Multilevel inverters using IGBTs are proposed for replacing the GTO-based two-level inverters in medium-voltage applications. Because IGBTs can switch faster and have less-demanding gate drive requirements than GTOs, IGBT-based multilevel inverters can significantly reduce the size and weight of passive filter components and offer better voltage waveforms. As the number of voltage levels, m, grows, the number of active switches increases according to  $2\times(m-1)$  for the cascaded H-bridge, diode-clamped and flying capacitor multilevel inverters  $\lceil 1-7 \rceil$ .

This paper presents a new class of multilevel inverters based on a multilevel dc link (MLDCL). An MLDCL can be a diode-clamped phase leg or a flying capacitor phase leg; or it can be constructed by connecting in series a number of half-bridge cells, each having its own dc source. A multilevel voltage source inverter can be formed by connecting an MLDCL with a single-phase bridge inverter. The MLDCL provides a dc voltage with the shape of a staircase, with or without pulse width modulation (PWM), to the bridge inverter, which in turn alternates the polarity to produce an ac voltage. Compared with the existing multilevel inverters, the new MLDCL inverters can significantly reduce the switch count as the number of voltage levels increases beyond five. For a given number of voltage levels, *m*, the new inverters requires *m*+3 active switches.

#### II PROPOSED MLDCL INVERTER TOPOLOGIES

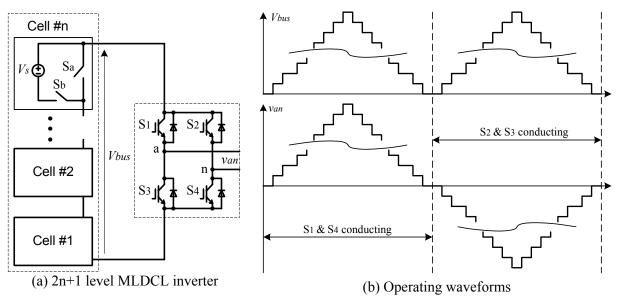

Fig. 1(a) shows a proposed inverter topology, which consists of a multilevel dc source and a single-phase full-bridge (SPB) inverter. The dc source is formed by connecting a number of half-bridge cells in series with each cell having a voltage source controlled by two switches. The two switches, Sa and Sb, operate in a toggle fashion. The cell source is bypassed with Sa on and Sb off, or adds to the dc link voltage by reversing the switches. Fig. 1(b) illustrates the operating principle. The MLDCL provides a dc bus voltage,  $V_{bus}$ , with the shape of a staircase to the SPB inverter, which in turn alternates the voltage polarity to produce an ac voltage of the staircase shape,  $v_{an}$ . The switches, Sa and Sb, can also perform PWM if necessary. This topology was introduced in [8] to reduce current ripple for brushless dc motors with an extremely low leakage inductance.

Fig. 1. A proposed MLDCL inverter based on half-bridge cells.

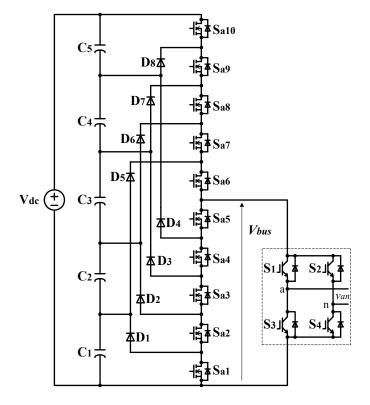

Fig. 2 shows an 11-level MLDCL inverter based on a diode-clamped phase leg. Similarly to the half-bridge cell-based MLDCL inverter, the diode-clamped MLDCL provides a dc bus voltage,  $V_{bus}$ , with the shape of a staircase to the SPB inverter, which in turn alternates the voltage polarity to produce an ac voltage of the staircase shape,  $v_{an}$ .

In a similar way, the flying capacitor—clamped phase leg can be used to replace the diode-clamped MLDCL; this alternative will be discussed in the full paper.

### III SIMULATION RESULTS

Detailed circuit simulation was conducted to verify the inverter operation.

Fig. 2. An 11-level MLDCL inverter based on a diodeclamped phase leg.

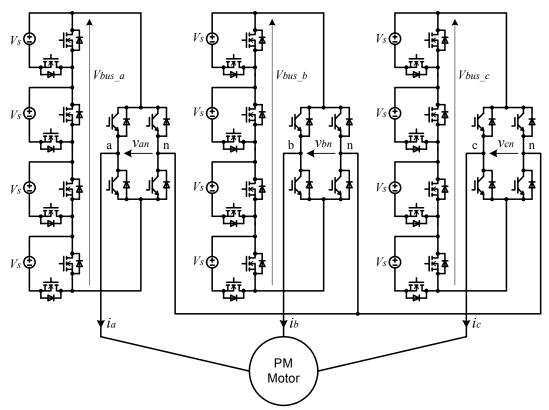

Fig. 3 shows a 9-level half-bridge cell-based MLDCL inverter for powering a permanent magnet (PM) ac synchronous motor. The PM motor is designed for hybrid electric vehicle applications with a

continuous rating of 30 kW and a very low leakage inductance of 25 µH per phase. The voltage of each dc source, *Vs*, is set at 36 V. Low-voltage MOSFETs, which switch at 20 kHz, are chosen for the cell switches because of their low on-resistance, leading to significantly reduced conduction losses. IGBTs are used for the SPB inverters and switch at the fundamental frequency.

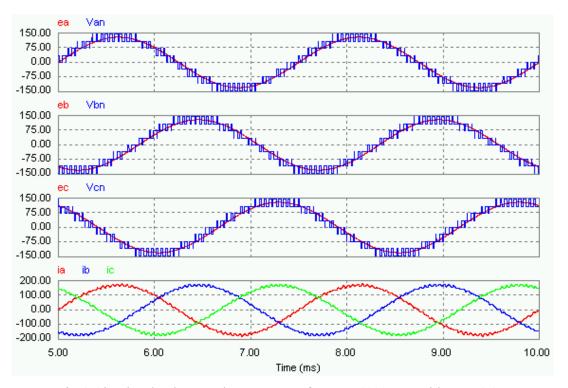

Fig. 4 shows simulated voltage and current waveforms when the motor operates at the maximum speed of 4000 rpm, where *ea*, *eb*, and *ec* are the back EMFs. Despite the very low leakage inductance, the rms value of the motor current ripple is only 3.6 % of the fundamental current, which is 120 Arms.

Fig. 3. A 9-level MLDCL inverter powering a PM ac synchronous motor.

#### IV CONCLUSIONS

The proposed MLDCL inverters can significantly reduce the switch count as the number of voltage levels increases beyond five. One application area for the MLDCL inverters is in PM motor drives with a very low leakage inductance. The proposed inverters can dramatically reduce current and torque ripples and can improve motor efficiency by reducing the associated copper and iron losses resulting from the current ripple.

For high-voltage applications, HV IGBTs or GTOs, switching at the fundamental frequency, can be used in the single-phase bridge inverters; while lower-voltage IGBTs performing PWM may be employed

in the MLDCL sources.

Fig. 4. Simulated voltage and current waveforms at 4000 rpm with  $V_S = 36V$ .

### REFERENCES

- [1] A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," *IEEE Trans. Ind. Applicat.*, vol. 17, no. 5, pp. 518–523, Sept./Oct. 1981.

- [2] R. W. Menzies, P. Steimer, and J. K. Steike, "Five-Level GTO Inverters for Large Induction Motor Drives," *IEEE/IAS Annual Meeting*, pp. 595–601, 1993.

- [3] C. Hochgraf, R. Lasseter, D. Divan, and T. A. Lipo, "Comparison of Multilevel Inverters for Static var Compensation," *IEEE/IAS Annual Meeting*, pp.921–928, 1994.

- [4] J. Zhang, "High Performance Control of a 3 Level IGBT Inverter Fed AC Drive," in *Proc. IEEE-IAS* '95 Conf., 1995, pp. 22–28.

- [5] P. W. Hammond, "Medium Voltage PWM Drive and Method," U. S. Patent 5,625,545, 1997.

- [6] J. S. Lai and F. Z. Peng, "Multilevel Converters A New Breed of Power Converters," *IEEE/IAS Annual Meeting*, pp. 2348–2356, Oct. 8–12, 1995.

- [7] F. Z. Peng, J. S. Lai, J. W. McKeever, and J. VanCoevering, "A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation," *IEEE Trans. Ind. Applicat.*, vol. 32, No. 5, pp. 1130–1138, Sept./Oct. 1996.

- [8] G. J. Su and D. J. Adams, "Multilevel DC Link Inverter for Brushless Permanent Magnet Motors with Very Low Inductance," *IEEE/IAS Annual Meeting*, vol. 2, pp. 829–834, Sept. 30–Oct. 5, 2001.