Available online at www.sciencedirect.com

Microelectronic Engineering 73-74 (2004) 695-700

www.elsevier.com/locate/mee

# Processing issues in top-down approaches to quantum computer development in silicon

S.-J. Park <sup>a</sup>, A. Persaud <sup>a</sup>, J.A. Liddle <sup>a,\*</sup>, J. Nilsson <sup>b</sup>, J. Bokor <sup>a,c</sup>, D.H. Schneider <sup>c</sup>, I.W. Rangelow <sup>d</sup>, T. Schenkel <sup>a</sup>

<sup>a</sup> Lawrence Berkeley National Laboratory, Berkeley, CA 94720, USA

<sup>b</sup> Lawrence Livermore National Laboratory, Livermore, CA, USA

<sup>c</sup> Department of EECS, University of California, Berkeley, CA, USA

<sup>d</sup> Institute of Microstructure Technologies and Analytics, University of Kassel, Germany

Available online 20 April 2004

#### Abstract

We describe critical processing issues in our development of single-atom devices for solid-state quantum information processing. Integration of single <sup>31</sup>P atoms with control gates and single electron transistor (SET) readout structures is addressed in a silicon-based approach. Results on electrical activation of low-energy (15 keV) P implants in silicon show a strong dose effect on the electrical activation fractions. We identify dopant segregation to the SiO<sub>2</sub>/Si interface during rapid thermal annealing as a dopant loss mechanism and discuss means to minimize it. Silicon nanowire SET pairs with nanowire width of 10–20 nm are formed by electron-beam lithography in SOI. We present initial results from Coulomb blockade experiments and discuss issues of control gate integration for sub-40 nm gate pitches.

Keywords: Quantum computer; Qubit; Ion implantation; Electron-beam lithography

### 1. Introduction

The potential of quantum systems to process information very efficiently has been under intensive investigation since the development of suitable algorithms by Shor [1] and Grover [2]. There are a number of techniques for creating suitable systems such as NMR [3], ion trapping [4] and a variety of solid-state approaches [5]. Although NMR and

ion-trap methods have successfully demonstrated the fundamental concepts, it is unlikely that they can be scaled effectively to produce an integrated system of qubits to the point where it becomes computationally interesting (>1000 qubits). For this reason we have chosen to examine in detail a solid-state scheme because such an approach holds out the promise of full scalability. Further, we have chosen to use a Si-based architecture because it can, in principle, be integrated with more conventional electronic devices and because the intensive study of Si and Si-processing makes it more likely that we can achieve the necessary atomic

<sup>\*</sup>Corresponding author.

E-mail address: jaliddle@lbl.gov (J.A. Liddle).

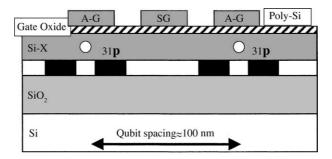

Fig. 1. Conceptual layout of a two-qubit test structure showing the two - <sup>31</sup>P-atom qubits aligned to the source (S) and drain (D) regions of the corresponding SET's. The electron-shuttling gate (SG) that controls the interaction between the two qubits is aligned between them, while the spin-state controlling gates (A–G) are aligned directly over them.

scale control of structural and electronic material properties.

Electron or nuclear spins of single donors, e.g., <sup>31</sup>P atoms in silicon, are suitable two-level systems with which to encode quantum information and promising candidates for the realization of scalable solid-state quantum computer architectures (Fig. 1) [6–8]. Irrespective of the details of the computation scheme three components are required in order to fabricate a test device: (1) an array of single, activated <sup>31</sup>P atoms, (2) single-spin readout devices (e.g., single electron transistors (SETs) [9]), and (3) integrated control gates [10].

It is crucial to perform experimental tests of the key tasks that need to be addressed for basic qubit scheme validation: single-spin manipulation, single-spin detection, coherent electron transfer, and two-qubit operations. Our development of an integrated two-qubit device is thus geared to provide access to the physics of the <sup>31</sup>P qubit in silicon as a suitable test vehicle.

In this paper, we will describe our development of single ion implantation technology, our current process flow, including the initial results of our Si SET effort, and discuss the challenges involved in completing the device with integrated control gates.

## 2. Single ion implantation

Three criteria must be met for the successful formation of a single atom array of <sup>31</sup>P qubits: (1) individual atoms must be delivered to the sub-

strate, (2) they must be electrically active and (3) they must be in known and stable locations.

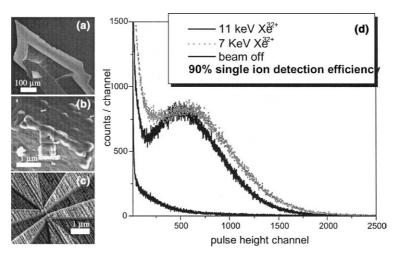

Single ion implantation with low-energy (<20 keV), highly charged ions offers a path to the formation of single <sup>31</sup>P atom arrays [11]. Fig. 2(a) illustrates our single ion implantation system individual ions pass through a small aperture fabricated at the end of a conventional SPM probe tip [12,13]. The tip can be positioned precisely with respect to substrate topography and the implantation of a single ion is detected by the burst of secondary electrons emitted when it is incident on the surface. Fig. 2(b) shows an example of pulse height distributions from detection of secondary electron bursts from low energy xenon ions. The high charge-state of the ion, together with the detector configuration, ensures that a sufficient number of secondaries are emitted and detected with each sample impact to guarantee a large enough signal to permit unambiguous discrimination between sample impacts and those much weaker signals from impacts on other system components [11,12]. The small aperture size and its precise location ensure that each atom is precisely placed. Apertures with diameters as small as 4.3 nm have been formed by focused ion beam drilling in combination with local thin film deposition [13].

A qubit spacing of 20 nm, equivalent to about 10 effective Bohr radii of the bound donor electron of a P atom in a silicon matrix, was envisioned in the original Kane proposal [6]. This spacing allows two-qubit operations through exchange interaction mediated by direct wave function overlap [14].

Fig. 2. Illustration of the single ion implantation scheme where individual highly charged dopant ions are implanted aligned by scanning probe microscopy (SPM) to sample features. Following one ion impact, the beam is blocked, and the sample moved to the next implant position. Apertures are formed by FIB drilling of  $\sim$ 100 nm holes and size reduction by local deposition of a Pt film. (a) SPM cantilever, (b) Hollow SPM tip with 30 nm wide aperture, (c) SPM image of a Silicon nanowire SET pair, (d) Example of pulse height distributions from detection of secondary electrons in the single ion implanter following the impact of low energy ions on silicon. The kinetic energies of  $Xe^{32+}$  ions were 11 keV (grey) and 7 keV (black). Potential electron emission yields increase for lower impact energies enabling efficient detection of very low energy ions.

$^{31}$ P atom spacings of  $\sim 100$  nm are possible when spin-coherent electron shuttling can be developed as a means for two qubit interactions [7]. The equivalent doses for qubit arrays are  $10^{10}$ – $2 \times 10^{11}$   $^{31}$ P/cm². In single ion implantation, ions are implanted to a depth of about 10–20 nm. An implant energy of 10–20 keV is favorable since it allows implantation through a pre-formed gate dielectric with minimal dopant loss in the dielectric layer. Also, the single ion positioning uncertainty from range straggling is kept below 10 nm.

Following implantation, wafers have to be annealed for damage repair and to ensure electrical activation of the dopants. Diffusion and segregation of dopants during rapid thermal annealing have to be minimized, while activation efficiencies close to 100% are mandatory for devices whose functionality is based on control of electron spin states in single atoms.

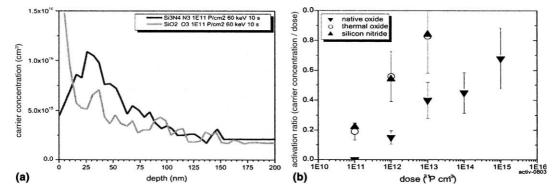

In Fig. 3(a), we show spreading resistance analysis (SRA) data from a 60 keV,  $10^{11}$  cm<sup>-2</sup> implant of P in silicon. Implanting at 60 keV places the peak of the carrier distribution at a depth of 30 nm and allows us to delineate a segregation effect with SRA. Data in the figure compare the post-

annealing profiles for SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> surface layers. For SiO<sub>2</sub>, we observe strong segregation towards the interface, while for Si<sub>3</sub>N<sub>4</sub>, we do not. The activation ratios, i.e., the ratio of measured carrier concentration to implanted dose, are  $80 \pm 25\%$  for both samples. Note that the large errors in activation ratios make direct comparisons between samples of limited value. However, we might speculate that the strong segregation effect for the oxide limits activation ratios for lower energy implants. The dose dependence of P activation in silicon is shown in Fig. 3(b) for 15 keV implants. Very low electrical activation fractions for low dose implants can be attributed to dopant loss at the interface. SiO<sub>2</sub> injects interstitials during rapid thermal annealing that aid in the segregation of P atoms towards the interface. P atoms can replace undercoordinated silicon atoms at the interface. The P remains then in a neutral state and is not electrically active [15]. The observed dopant loss mechanism is dose dependent, and we are currently investigating co-implantation of silicon ions to change the interstitial-vacancy balance, together with aggressive pre-implant anneals to further enhance activation ratios in the low dose, low energy implant regime.

Fig. 3. (a) Carrier concentration as a function of depth from spreading resistance analysis of P implanted silicon (60 keV,  $10^{11}$  cm<sup>-2</sup>). Black: 7 nm silicon nitride layer, gray: 5 nm thermal SiO<sub>2</sub> layer. (b) Activation ratios determined by spreading resistance analysis as a function of ion dose. The corresponding dose for a Kane-type solid-state quantum computer is  $10^{10}$ –  $2 \times 10^{11}$  cm<sup>-2</sup>. All samples were annealed for 10 s at 1000 °C in a  $N_2$  atmosphere.

#### 3. Process integration

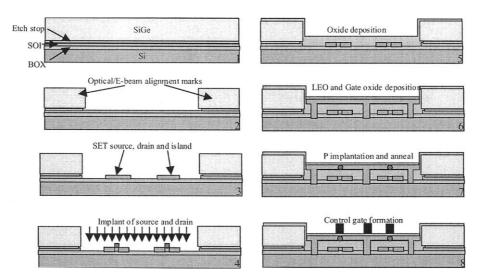

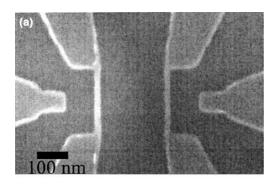

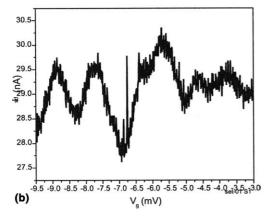

Fig. 4 outlines the process flow, while Fig. 5(a) shows an SEM image of a Si-nanowire SET pair in silicon-on-insulator (SOI). Here, the nanowire thickness is 30 nm, and the wire region is undoped. Gate, source and drain regions were highly n-type doped. Fig. 5(b) shows initial results from electrical characterization of devices at 4.2 K.

Coulomb blockade effects have been observed in silicon nanostructures for many years [16]. In our application of Si-SETs as sensitive electrometers in spin dependent charge measurements [9], operation at liquid-He temperatures is desirable. Consequently, the size requirements for our SETs are determined by need for the SET-island charging energy to exceed 10 kT. Coulomb blockade is likely to result from defects and local inhomoge-

Fig. 4. Process flow. Alignment marks are created in a SiGe layer (2) and are used for both optical and electron beam lithography. The SET islands and source and drain are defined in a thin (<30 nm) SOI layer (3). The island regions are masked during the implantation step that creates the source and drain (4). Oxide is deposited over the SET structure (5). Lateral expitaxial overgrowth (LEO) is used to create a high-quality <sup>28</sup>Si layer and a gate oxide is grown upon it (6). The <sup>31</sup>P ions are implanted and activated with an anneal (7). The control gates are then fabricated (8). Finally a series of conventional optical lithography steps create the contacts to the small-scale features.

Fig. 5. (a) SEM of a Si SET-pair structure in silicon-on-insulator. The silicon nanowire is undoped. The SOI thickness is 30 nm on 400 nm buried oxide (BOX). Source, drain and gate leads are highly n-type doped. (b) Coulomb blockade oscillations in a silicon nanowire SET at 4.2 K.

neities in the nanowire and the interface of the nanowire to the highly n-type doped source and drain leads. While Coulomb oscillations of regular period are desirable, stability of device characteristics is of even greater importance for SET sensors. We are now investigating the latter in systematic studies.

An important criticism of solid-state approaches to quantum computer development is that all devices components will have minute differences [17], which will result in a need for diligent calibration of components. SOI allows a high degree of control over process parameters, and is compatible with high temperature processes. The latter is important for reduction of defect densities. Defects stable on the time scale of 10<sup>4</sup> qubit manipulations (tens of milliseconds) might also be permissible [5].

## 4. Control gates

Local control of electron wave functions is at the heart of all atom-based solid-state qubit proposals. This local control can be achieved with electrical gates, which tune single electrons into resonance with external magnetic fields for singlequbit operations. For two-qubit operations, a control gate can act on the extent of electron wave function overlap between neighboring atoms. Gate width requirements depend on the qubit spacing. In the original Kane proposal, two A gates controlling the electron/nuclear spin-state – , and one J gate – controlling the wavefunction overlap of adjacent qubits - are required with a qubit spacing of 20 nm. An equivalent gate pitch of 10 nm (5 nm gate width, and 5 nm spacing) is beyond current state-of-the-art for dense patterns. While isolated lines with widths of only a few nm have been formed for many years, the key problem is the development of dense pattern capabilities at a 10 nm gate pitch. An additional boundary condition is that gates have to be aligned to within a few nm to the single atom arrays. Gate integration at this level is a crucial issue both for top-down (with single ion implantation) and bottom-up (with scanning tunneling microscopy) [18,19] based device fabrication strategies. Gateless, all-optical control of atom qubits has recently been proposed, but issues of multi-qubit entanglement remain to be addressed [20].

Alternatives to a 10 nm gate pitch require strategies to increase the qubit spacing. Use of silicon-germanium heterostructures has been suggested by Virjen et al. [21]. The resulting Landé gfactor engineering can result in usable Bohr radii of about an order of magnitude in excess of values for a bare silicon matrix. Design of the heterostructures comes with its own challenges. An alternative is to shuttle electrons between P atoms to mediate two-qubit operations [7]. This requires encoding of a logical qubit in the electron and nuclear spin of a P atom. It also requires design of silicon quantum well structures that allow reliable movement of a single electron over distances of hundreds of lattice spacings, without losing the electron and without modifying its carefully prepared spin state (orientation and phase). Clearly,

spin coherent single electron transport is a crucial experimental challenge in silicon based quantum computer development. An important recent result is that spin coherence times have been shown to depend on P atom spacing: for larger P atom separations (>100 nm), decoherence times of tens of milliseconds have been found in bulk measurements [22].

#### 5. Conclusions

In this article, we address several critical issues in the development of a two 31P qubit device in silicon that allows testing of basic operations, and that can be used to validate basic quantum information processing schemes. Single ion implantation aligned with a scanning probe is a path to formation of nanometer-scale single P atom arrays in silicon. Single ion registration is achieved through detection of secondary electron bursts from highly charged ion impacts. Achieving essentially full electrical activation of a low energy, low-dose P implant is crucial for device development. We show an effect of dopant segregation towards the SiO<sub>2</sub>/Si interface at the 10<sup>11</sup> cm<sup>-2</sup> dose level. Measures to eliminate this effect currently under investigation are: annealing under nitridation conditions, aggressive hydrogen anneals before implantation, and co-implantation of silicon.

Silicon nanowire SET pairs were formed in SOI with linewidth of 10–20 nm. We discuss lithography and pattern transfer process issues and present first results from Coulomb blockade studies at liquid helium temperatures. Design and fabrication of control gates is another critical issue, where two qubit operation schemes and lithographically achievable gate widths have to be balanced.

While significant technical challenges remain to be resolved, we present a workable processing path towards achieving fabrication of all silicon two qubit test structures in the near future.

## Acknowledgements

This work was supported by the NSA and ARDA under ARO contract number MOD707-

501, by the US DOE under contract No. DE-AC03-76SF00098 and by DARPA under contract No. MDA972-98-C-0007. Work at LLNL was performed under the auspices of the US DOE under contract No. W-7405-ENG-48. We thank the staff of the UC Microlab and the NCEM for their support.

#### References

- [1] P.W. Shor, SIAM J. Comput. 26 (1997) 1484.

- [2] L.K. Grover, Phys. Rev. Lett. 79 (1997) 325.

- [3] N.A. Gershenfeld, I.L. Chuang, Science 275 (1997) 350.

- [4] D. Kielpinski, C. Monroe, D.J. Wineland, Nature 417 (2002) 709.

- [5] M.A. Nielsen, I.L. Chuang, Quantum Information Science, Cambridge University Press, Cambridge, 2000.

- [6] B.E. Kane, Nature 393 (1998) 133.

- [7] A.J. Skinner, M.E. Davenport, B.E. Kane, Phys. Rev. Lett. 90 (2003) 087901.

- [8] A roadmap for quantum information science and technology was recently published under: http://qist.lanl.gov/.

- [9] T.M. Buehler, D.J. Reilly, R. Brenner, A.R. Hamilton, A.S. Dzurak, R.G. Clark, Appl. Phys. Lett. 82 (2003) 577

- [10] T. Schenkel, A. Persaud, S.J. Park, J. Nilsson, J. Bokor, J.A. Liddle, R. Keller, D.H. Schneider, D.W. Cheng, D.E. Humphries, J. Appl. Phys. 94 (2003) 7017.

- [11] T. Schenkel, A. Persaud, S.J. Park, J. Meijer, J.R. Kingsley, J.W. McDonald, J.P. Holder, J. Bokor, D.H. Schneider, J. Vac. Sci. Technol. B 20 (2002) 2819.

- [12] T. Schenkel, I.W. Rangelow, R. Keller, S.J. Park, J. Nilsson, A. Persaud, V.R. Radmilovic, P. Grabiec, D.H. Schneider, J.A. Liddle, J. Bokor, Nucl. Instr. Meth. B 219– 220 (2004) 200–205.

- [13] P. Grabiec et al., J. Vac. Sci. Technol. B 22 (2004) 16; T. Schenkel et al., J. Vac. Sci. Technol. B 21 (2003) 2720.

- [14] A. Fang, Y.C. Chang, J.R. Tucker, Phys. Rev. B 66 (2002) 155331.

- [15] J. Dabrowski, H.-J. Müssig, V. Zavodinsky, R. Baierle, M.J. Caldas, Phys. Rev. B 65 (2002) 245305.

- [16] see, e. g., H. Ahmed, J. Vac. Sci. Technol. B 15 (1997) 2101.

- [17] R.W. Keyes, Appl. Phys. A 76 (2003) 737.

- [18] T.C. Shen et al., Appl. Phys. Lett. 80 (2002) 1580.

- [19] J.L. O'Brien et al., Phys. Rev. B 64 (2001) 1401.

- [20] A.M. Stoneham, A.J. Fischer, P.T. Greenland, J Phys.: Cond. Matt. 15 (2003) L447.

- [21] R. Vrijen et al., Phys. Rev. A 62 (2000) 12306.

- [22] A.M. Tyryshkin, S.A. Lyon, A.V. Astashkin, A.M. Raitsimring, Phys. Rev. B 68 (2003) 193207.