# On the Analog CMOS Peak Detect and Hold Circuit Part 2. Offset-Free Rail-to-Rail and Derandomizing Configuration<sup>1</sup>

Gianluigi De Geronimo, Paul O'Connor and Anand Kandasamy

Brookhaven National Laboratory, Instrumentation Division, Bldg 535B, Upton, NY 11973, USA

#### Abstract

An analog CMOS peak detect and hold (PDH) circuit which combines high speed and accuracy, rail-to-rail sensing and driving, low power, and buffering is presented. It is based on a configuration that *cancels* the major error sources of the classical CMOS PDH, including *offset* and common mode gain, by re-using the same amplifier for tracking, peak sensing, and output buffering. By virtue of its high *absolute* accuracy, two or more PDHs can be used in parallel to serve as a data-driven analog memory for derandomization.

First experimental results on the new peak detector and derandomizer (PDD) circuit, fabricated in 0.35 µm CMOS technology, include a 0.2 % *absolute* accuracy for pulses with 500 ns peaking time, 2.7 V linear input range, 3.5 mW power dissipation, 250 mV/s droop rate, and negligible dead time. The use of such a high performance analog PDD can greatly relax the requirements on the digitization in multi-channel systems.

## I. INTRODUCTION

A common problem in scientific instrumentation is to measure charge impulses from a multichannel detector. The first element of the electronic chain in such a system is a low-noise, charge-sensitive preamplifier, followed by circuit blocks that perform further processing such as filtering (pulse shaping), peak detection, and determining the time of occurrence. The most flexible method of pulse processing is to digitize the signal directly after the lownoise preamplifier. Once the waveform has been recorded as a series of digital samples of sufficient precision and sampling frequency, the subsequent operations can be performed very efficiently by modern digital signal processing hardware.

For systems with many channels, however, a fully digital signal processing chain can be impractical. Since only the most cost- and power-insensitive applications can allocate an ADC per channel, usually the events of interest are multiplexed into a more limited number of ADCs. In order to identify the events to digitize, a trigger of some type is necessary. An auxiliary detector may generate the trigger, or it may be formed from the charge measurement channels themselves. The trigger can be global, in which case it signals only the occurrence of an event somewhere in the detector, or it may identify the occupied channels as well.

In response to the trigger, the system may sample the analog waveform (*track-and-hold* configuration) for later digitization, or activate a multiplexer which sends the waveform of the occupied channel directly to an ADC.

Triggered systems suffer from two sources of inefficiency and inaccuracy. First, uncertainty in the time of occurrence means that precise peak samples are not always acquired. The timing uncertainty may arise from the method of generating the trigger or from propagation delays throughout the detector. To deal with this time uncertainty, some systems employ multiple sampling of the waveform to capture pre- and post-peak information; the precise timing and peak height are recovered in offline analysis (typically four to sixteen samples are recorded per trigger). Second, global triggers require that samples from all channels be recorded, even those that are not occupied. Usually the unoccupied channels are identified and eliminated (sparsified) after digitization.

The ADC resources needed to support a globally-triggered, multiply-sampled readout system are high. If the channel count is N<sub>ch</sub> and the number of time samples recorded per trigger is  $n_t$ , then the total number of digital samples to be acquired is  $N_{ch} \cdot n_t$  (note that the system can contain many ADCs operating in parallel by means of a suitable multiplexing arrangement). Since most systems cannot simultaneously acquire new data and read out old data, they are blocked or "dead" during readout; the readout must be completed before new data can be acquired. Hence, the digitization must be completed in a time t<sub>block</sub>, the maximum tolerable dead time. This requires the digitization system to work at a rate  $R_{trg} = N_{ch} \cdot n_t / t_{block}$ samples per second. The requirements on the digitization system can be greatly relaxed by the availability of a fast and accurate *peak detect and hold (PDH)* circuit.

With an ideal PDH, timing uncertainty is eliminated and a precise peak sample is always obtained, so  $n_t = 1$ . The PDH automatically sets a flag when it is occupied, making sparsification feasible before digitization. Furthermore, the hold capacitor of the PDH acts as an analog memory; hence two or more PDH circuits can be placed in parallel and operated alternately, providing a derandomizing capability that practically eliminates readout dead time. We refer to this as a *peak detector and derandomizer (PDD)* configuration.

With the PDD, the number of samples per trigger is only  $N_{occ}$ , where  $N_{occ}$  is the number of occupied channels, and the sampling can occur at a rate equal to the average event rate  $1/t_{event}$ . A system implemented with PDDs thus requires an overall digitizing rate  $R_{PDD} = N_{occ} / t_{event}$ . The reduction in required rate compared with a triggered, multiply-sampled system is given by:

$$\frac{\mathbf{R}_{PDD}}{\mathbf{R}_{trg}} = \left(\frac{1}{n_t}\right) \left(\frac{\mathbf{N}_{occ}}{\mathbf{N}_{ch}}\right) \left(\frac{\mathbf{t}_{block}}{\mathbf{t}_{event}}\right) , \qquad (1)$$

where first factor comes from the precise peak timing, the

<sup>&</sup>lt;sup>1</sup> Work supported by the US Department of Energy, Contract No. DE-AC02-98CH10886. Patent pending.

second is due to self-sparsification, and the last factor is from the buffering and derandomizing function of the PDD. Overall, the PDD can reduce the digitizing requirement by several orders of magnitude. In the case of a trigger identifying the occupied channel the second factor in Eq. (1) becomes one ( $N_{ch} = N_{occ}$ ), but the PDD can still greatly relax the digitizing requirement due to the two remaining factors. In addition, the peak detector eliminates the need for a trigger. Indeed the PDH itself can signal the time of occurrence of the peak.

Several analog PDH circuit solutions were proposed during the past years, all based on a feedback loop and a rectifying element, and ranging from the classical diode to the current mode and current conveyor approach [1-5]. Among the integrated circuit realizations the one originally proposed by Kruiskamp and Leenaerts [1, 6-8] is particularly attractive the Kruiskamp-Leenaerts circuit, which uses a current mirror as rectifying and loopstabilizing element, can be considered the current state of the art. Both this and the other CMOS compatible PDH circuits, while promising, were not widely adopted in multi-channel CMOS front-ends because they suffer from significant limits in accuracy, speed, and dynamic range (analyzed in a companion paper in this issue [9]). These limits can be only partially alleviated by direct solutions such as in-loop buffering and proper MOSFET sizing, as each of these direct solutions introduces further errors.

In this paper we propose and experimentally demonstrate a new CMOS PDH circuit solution that overcomes these drawbacks. It is based on a two-phase approach that cancels the offset (the major error source) by re-using the peak sensing amplifier as an output buffer. By employing a fast and stable amplifier with rail-to-rail sensing and driving capability, it provides a substantial improvement in speed, accuracy, and dynamic range over the current state of the art. In addition, we show that it is possible to use multiple PDH circuits in parallel for high rate operation and derandomization without introducing appreciable error.

The operation and limits of the classical state-of-the-art CMOS PDH were discussed in a related paper [9]. The proposed two-phase CMOS PDH is discussed in Section II while the derandomizing configuration (PDD) is discussed in section III. Section IV reports the experimental results.

## II. THE TWO-PHASE CMOS PDH

What we propose is a solution (the *two-phase CMOS PDH*) that overcomes the major limits of the classical CMOS PDH [9]. In particular, the proposed configuration exhibits the following improvements.

- It is *offset-free* (i.e. the accuracy is not affected by the offset V<sub>off</sub> of the amplifier).

- Its accuracy is not affected by common-mode errors of the amplifier.

- The input MOSFETs can be properly sized to minimize the impact of their parasitic capacitances on the accuracy, without regard to mismatch effects.

- A rail-to-rail input and rail-to-rail output OTA is implemented so that it can accurately process rail-to-rail pulses.

- The MOSFET M<sub>1</sub> can be properly sized to minimize its impact on the accuracy.

- It is characterized by rail-to-rail *high driving capability*.

In this Section the operation (A), accuracy and stability (B), amplifier and logic realization (C) of the proposed two-phase PDH are discussed.

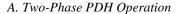

Fig. 1 - Simplified schematic of the two-phase PDH.

In Fig. 1 a simplified schematic of the two-phase PDH for positive peak detection is shown. In the first phase (WRITE phase, W) switches S3, S4 and S5 are open while S1 and S2 are closed. The operational transconductance amplifier, OTA, supplies current to the current mirror  $M_1 - M_2$  so as to charge the hold capacitor, Ch. In this configuration the circuit provides tracking, peak detection and hold [9]. In the second phase (READ phase, R) switches S1 and S2 open, breaking the loop and isolating the PDH from any additional input signal. Switch S5 closes, shutting off M<sub>1</sub> to ensure that no currents other than leakage disturb the peak voltage V<sub>h</sub> stored in the hold capacitor C<sub>h</sub>. Switch S3 in closed position turns the OTA into a unity gain buffer, with V<sub>h</sub> as its input signal. Finally, S4 connects the buffered peak sample to the read-out system, represented by the load impedance Z<sub>L</sub>. Once the read-out has been completed, the reset switch S6 closes momentarily to reset  $V_{\rm h}$  to a chosen baseline  $V_{\rm BL}.$  The PDH can then be returned to the W state, ready to process the next pulse.

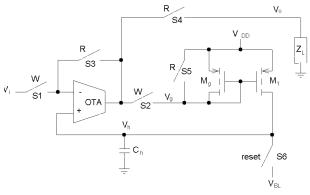

To see how the two-phase configuration leads to offset cancellation, refer to Fig. 2a. In the WRITE phase, the amplifier offset  $V_{off}$  corrupts the peak voltage stored on  $C_h$ . During the second phase (Fig. 2b), the amplifier acting as a follower of the voltage held on Ch. The offset voltage  $V_{off}$  is now subtracted from the held peak value, canceling the error.

Figure 2 Simplified schematic of the two-phase peak detector. (a) WRITE phase, (b) READ phase.

We can make the circuit switch automatically from the WRITE state to the READ state by sensing the signal at node  $V_g$  in Fig. 1. When a pulse is being tracked,  $V_g$  falls to a level at least  $|V_T|$  below  $V_{DD}$  to provide current to charge the hold capacitor  $C_h$ . After the peak  $V_g$  makes an upward transition to switch off the current into  $C_h$ . This low-to-high transition can be detected with an appropriate comparator and used to put the circuit into the R state to await read-out. Moreover, the upward  $V_g$  transition serves as an accurate time maker to indicate the time of arrival of the pulse for those systems requiring such an information.

It is important to note that no switch is directly connected to the hold capacitor, other than the reset switch (not active during the sensing and readout of the pulse). The sensitive hold node is thus isolated from switching noise. The only design criterion to be applied for the switches is related to minimizing the parasitic time constants introduced in the loops.

To acquire the baseline, the reset level  $V_{BL}$  can simply be set to a voltage lower than the signal baseline. In the W state the PDH can be easily stabilized as discussed in Section II.C. of Ref. 9, while in the R state the stabilization of the unity gain configuration may require the simple addition of a compensation capacitor in parallel to  $Z_L$ .

## B. Residual Error

Concerning the accuracy, in the W state the PDH is subject to all the limits discussed in Section II.B. of Ref. 9, due to  $M_1$  ( $C_{gd}$ ,  $Q_{ch}$ ,  $C_d$ ) and OTA ( $V_{o,cm}$ ,  $A_0$ , CMRR,  $C_c$ ,  $C_i$ , speed).

The rail-to-rail output capability of the OTA, by Eq. (2) of Part 1 allows the use of minimum values for the size of  $M_1$ , thus improving the accuracy. The positive impact on the equations for the stability should also be considered with respect to the configurations in Fig. 13 of Ref. 9 (see also Sections II.C. and II.E. of Ref. 9).

The input stage of the OTA (see Fig. 3) uses two differential pairs in parallel (one NMOS and one PMOS) to achieve rail-to-rail sensing. The two major consequences are an offset  $V_{off}$  (mainly due to the mismatch between the differential couple, and different for the two couples) which depends on the input voltage, and higher values for  $C_c$  and  $C_i$ .

On the other hand the impact of  $V_{off}$  on the accuracy of the two-phase PDH is zero: the error  $V_{e,dc,W} = V_{hp}-V_{ip}$  in the W

state is given by [9]:

$$V_{e,dc} \approx \frac{V_{gp} - V_{o,cm}}{A_0} + V_{off} - \frac{1}{CMRR} \frac{2V_i - V_{DD}}{2}$$

(2)

where  $V_{o,cm}$  is the common mode output reference for  $V_i^+ = V_i^- = V_{DD}/2$ ,  $V_{gp}$  is the gate voltage in proximity of the peak and  $A_0$  is the open-loop dc voltage gain.

The error  $V_{e,dc,R} = V_o - V_{hp}$  in the R state is easily calculated as:

$$V_{e,dc,R} \approx -\frac{V_{ip} - V_{o,cm}}{A_0} - V_{off} + \frac{1}{CMRR} \frac{2V_i - V_{DD}}{2}$$

(3)

where we assumed that  $A_0$  is negligibly affected by  $Z_L$ . The total error  $V_0$ - $V_{ip} = V_{e,dc}$  is given by:

$$V_{o} - V_{ip} = V_{e,dc} \approx \frac{V_{gp} - V_{ip}}{A_{0}}$$

(4)

The errors introduced by  $V_{off}$ ,  $V_{o,cm}$ , and CMRR are thus *canceled*, while the residual error from Eq. (4) can be minimized by maximizing the dc voltage gain  $A_0$ . This result also indicates that it is now possible to minimize the size of the input MOSFETs of the double differential stage disregarding any mismatch and consequent offset. In this way the minimization of  $C_c$  and  $C_i$  is obtained.

Under these conditions, the accuracy of the two-phase PDH is to some extent limited only by  $A_0$  as from Eq. (4), and by the finite speed of the OTA (see Eq. (15) of Ref. 9).

### C. Rail-to-Rail OTA

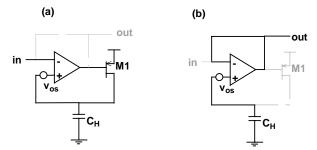

Of the several schemes of OTA available in the CMOS literature [10-12], none seemed to match this requirement in a reasonable amount (few mW) of dissipated power. We have consequently developed an OTA which matches the needs of the PDH. A schematic of the OTA is shown in Fig. 3 where, in order to simplify the concept to the reader, each stage has been separated and linked to the others through labels (a through j excluding h and i).

If current-mirror compensation is adopted, the maximum value of the pole  $\omega_{a,max}$  at the output node of the OTA is achieved when the input slope equals  $V'_{imax}$ . It can be written (see Appendix C and Eq. (A3) of Ref. 9):

$$\frac{1}{\omega_{a,max}} \approx \frac{C_g}{\lambda g_{m,max}} < \frac{C_h}{A_{0,max} g_{m,max}} \approx \frac{V_{DD} - V_T}{V_i' \max A_{0,max}} , \qquad (5)$$

where  $A_{0,max}$  is the dc voltage gain in proximity of the peak, i.e. the value to be used in Eq. (2). When fast pulses need to be processed, the condition (3) may become so stringent that the secondary poles of the OTA start to play a role in the stability of the loop. In practical cases the influence of the secondary poles will force us to choose values for W<sub>g</sub> relatively larger than the mere equality in (C8) of Ref. 9. The resulting increase in the value of C<sub>g</sub> has negative impact on the power dissipated by the OTA

or on its speed. In order to minimize this impact, an OTA with secondary poles located at as high as possible frequency should be implemented.

Fig. 3 - Schematic of the OTA

The two (n-MOSFET and p-MOSFET) differential stages sum their current at nodes d1 and d2. A dc voltage gain of about 10 is achieved at these nodes, with time constant located at very high frequency. The two followers  $M_{fw}$ drive the output stage (slightly simplified in Fig. 3) which provides an additional dc voltage gain of the order of 100 for a total dc voltage gain (i.e.  $A_{0,max}$ ) of the order of 1000. The common-mode feedback (CMF) controls the common mode current of the input stage through M<sub>nd</sub>. A lead-lag compensation (R<sub>cmp</sub> and C<sub>cmp</sub>) for stabilizing the commonmode loop is also included. A cross-connection at the input disables the CMF whenever one of the two M<sub>no</sub> is shut off, thus minimizing its impact on the differential gain. The dynamic current bias stage provides dc biasing of nodes a, b and j and dynamic biasing of node g. When, for large signals, the p-MOSFET differential stage approaches the shut off, a current starts to flow through the n-MOSFET differential stage. This maintains a relatively constant gain over the whole rail-to-rail swing.

In the version that we implemented in the PDH the value of the bias current Ib was set to  $\approx 66\mu$ A, while values for the multiplicity factors N and No of 4 and 6 respectively were chosen. Values of  $W_g = 4\mu m$  and  $W_g = 12\mu m$  were chosen for the input n-MOSFETs and the input p-MOSFETs respectively.

Table 1 - PSpice BSIM3v3.1 simulated performance of the OTA.

| Parameter          | Value                        |

|--------------------|------------------------------|

| GBW                | 80 GHz                       |

| Output resistance  | 200 kΩ                       |

| Dc voltage gain    | 1.45k                        |

| Dissipated power   | $3.3V \times 1.06mA = 3.5mW$ |

| Max output current | 500 µA                       |

| Output pole        | 56 MHz                       |

| Second pole        | 960 MHz                      |

| Third pole         | 2.6 GHz                      |

Simulation results of the unloaded OTA using BSIM3v3.1 modeling of MOSFETs and including source and drain parasitic capacitors are shown in Table 1. The stabilization of the unity gain configuration requires a minimum capacitive load at the output node of the order of 1pF. The dc voltage gain is nearly constant up to  $\approx$  500mV from the rails, then it starts to decrease. Gain of about 100 at  $\approx$  250mV from the rails was simulated.

### III. THE PEAK DETECTOR AND DERANDOMIZER (PDD)

The need to measure the amplitudes of randomly-arriving pulses is not uncommon in nuclear electronics. As discussed in Section I, a PDH system capable of accurately processing and storing several pulses in parallel can greatly relax the requirements on the following ADC, which now needs to convert only one value for each pulse, and at a rate equal to the average rate of the arriving pulses (time domain derandomization).

In Section II we showed how the two-phase PDH can achieve rail-to-rail absolute accuracy which is independent of process variations. This opens up the possibility of using several two-phase PDHs in parallel without adding the complexity of a separate and voltage dependent calibration for each PDH. A further possibility is to construct a two-phase PDH with multiple hold capacitors and suitable switches to store and readout more than one peak. By combining the peak detection and analog storage functions of the PDH with suitable control logic, the PDD can be made to behave like a data-driven analog FIFO. In this Section the peak detector and derandomizer configuration (PDD), based on the use of several twophase PDHs operating in parallel, is discussed. The first experimental results from a dual version are reported in section IV.

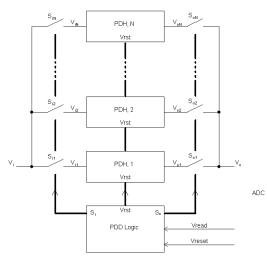

In Fig. 4 a simplified schematic of the PDD based on N copies of the two-phase PDH is shown. The block labeled *PDD Logic* keeps track of the next empty PDH and maintains an ordered list of occupied PDH cells awaiting readout.

Fig. 4 - Simplified schematic of the PDD for storing and derandomizing up to N samples.

When a new pulse arrives, it is detected and held on the storage capacitor of the n<sup>th</sup> peak detector (PDH-n). The PDD logic opens the input switch  $S_{in}$ , then selects the n+1<sup>st</sup> PDH available for input and closes the corresponding input switch  $S_{in+1}$ . In the mean time it stores the address in a N-deep first-in-first-out memory (readout FIFO). Up to N pulses can be processed and stored without requiring the read-out.

When the ADC is ready to convert a value, the external logic sends a signal Vread to the PDD. The PDD logic selects the first PDH address from the readout FIFO and closes the corresponding output switch. Once the conversion is completed, the external logic sends a signal Vreset to the PDD, resetting the PDH and making it available for a further input processing.

While one PDH is being read out, another can accept input pulses. By choosing a large enough buffer size N, we can eliminate nearly all dead time while clocking the ADC at the average event rate.

In a more complex system, channel ID and timing information for every hit can be combined with the PDH address and stored in the readout FIFO. Then the data acquisition system can read amplitude, position, and time for every pulse.

#### IV. THE PEAK DETECTOR AND DERANDOMIZER (PDD)

In this section we report the experimental results on the two phase PDH (A) and the first experimental results on the PDD.

## A. Experimental Results on the PDH

In Fig. 5 the complete layout of the analog section (a)  $(340 \times 50 \ \mu\text{m}^2)$  and of the digital section (b)  $(245 \times 50 \ \mu\text{m}^2)$  of the PDH are shown. The 0.35 $\mu$ m CMOS technology from TSMC was used for this realization. Separate grounds and supplies and additional mixed signal layout techniques were used in order to minimize the digital noise.

Fig. 5 - Layout of the Two-Phase PDH (a = analog, b = digital) for a  $0.35\mu m$  CMOS technology.

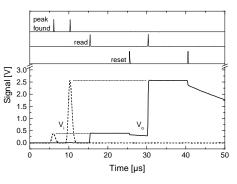

In Fig. 6 the measured signals  $V_i$ ,  $V_h$ ,  $V_o$  and  $V_g/V_{DD}$  from two different samples are shown. No averaging was used for these acquisitions. The input signal  $V_i$  (dot-dash) is a semigaussian pulse with peak amplitude  $V_{ip} \approx 600$ mV and peaking time  $\tau_p \approx 1.2\mu$ s. The circuit is reset at  $t = 3\mu$ s.

Fig. 6 - Measured signals  $V_i$ ,  $V_h$ ,  $V_o$  and  $V_g/V_{DD}$  from identical PDH circuits on two different chips. Note that the two circuits show oppositesign offset errors at the hold node  $V_h$ , but that these errors are cancelled at the output  $V_o$ .

The hold signal  $V_h$  (dash) is read out through a buffer realized by using an OTA identical to the one described in sub-section III.C. The peak amplitude stored at the hold node,  $V_{hp}$ , is strongly affected by the offset  $V_{off}$  of the OTAs and is strongly different between the two chips. On the other hand, the output signal  $V_o$  (solid) doesn't seem to be affected by the offset, in agreement with Eq. (4).

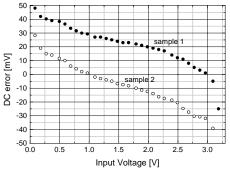

Fig. 7 - Measured dc accuracy of the OTA in buffer configuration from two different chips.

As previously discussed, the major consequence of the implementation of a double differential input stage for the OTA is that the offset  $V_{off}$  becomes voltage dependent. As example, in Fig. 7 the DC error normalized to  $V_{DD}$ , measured at the input of the OTA in the buffer configuration as function of the input voltage for two different samples is shown. From a comparison to PSpice simulations an offset +30mV for the n-MOSFET and -12mV for the p-MOSFET for case (a) and -4mV for the n-MOSFET and -40mV for the p-MOSFET for case (b) were extracted. Other sources of error are due to the reduction of the gain in proximity of the rail and to the CMRR as in Eq. (1).

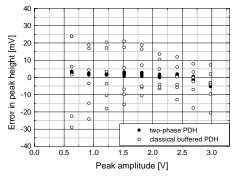

Fig. 8 - Measured error of the classical (open circles) and two-phase (solid circles) PDH versus input peak amplitude. For the classical PDH an on-chip unity-gain follower buffers the peak voltage stored on the hold capacitor. Eight different chips of the two-phase PDH and six of the traditional PDH were measured. Note the dramatic reduction in both the error and dispersion when the two-phase approach is used, due to its offset-canceling property. Semigaussian pulses of 4  $\mu$ s peaking time were used as input.

In Fig. 8 the measured error of the PDH from different chips (solid circles) is shown, for different amplitudes and  $\tau_p \approx 4\mu s$ . The error measured at the hold node through a buffer (open circles) realized by using the OTA is also shown. Even if the measurements were performed on different chips, a 0.2% absolute accuracy was observed for amplitudes 300mV from the rails, compared to 1.1% in the buffered case. The error showed less than 2.5 mV chip-to-chip variation for the two-phase circuit, compared to 53 mV for the single-phase PDH. The dependence of the error on the peak voltage, in agreement with Eq.(4) and with the reduction of the OTA gain in proximity of the rail, can also be observed.

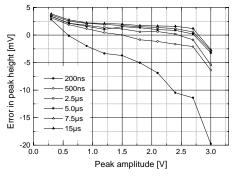

Fig. 9 - Measured error of the two-phase PDH, normalized to  $V_{\rm DD},$  with semigaussian input pulses of different amplitudes and peaking time.

In Fig. 9 the measured error of the PDH for different peaking times  $\tau_p = 200$ ns (solid line), 500ns, 2.5µs, 5µs, 7.5µs and 15µs, normalized to V<sub>DD</sub>, is shown. Better than 0.2% absolute accuracy can be achieved with this version of PDH for  $\tau_p \approx 500$ ns, while it deteriorates to  $\approx 0.7\%$  for  $\tau_p \approx 200$ ns. This is consequence of the finite speed of the loop as described in Section II.B of Ref. 1 and can be improved by increasing the power dissipated by the OTA for accurate processing of sub-100ns pulses.

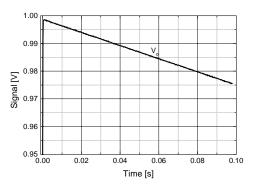

Fig. 10 - Measured droop rate of the two-phase PDH.

In Fig. 10 shows the droop rate of the PDH. The droop, due to the leakage of the reset switch, is of the order of 0.24 V/s. From this value and the value of the hold capacitor  $C_h \approx 2pF$  a leakage current  $\approx 500$  fA can be inferred.

## B. First Experimental Results on the PDD

A version of the PDD with N = 2 was realized in the 0.35 $\mu$ m CMOS technology from TSMC. In Fig. 11 the measured analog and digital signals for a sequence of two semigaussian input pulses V<sub>i</sub> with peak amplitude  $\approx$  360mV and  $\approx$  2.55V respectively, peaking time 1.2 $\mu$ s, and delay  $\approx$  5 $\mu$ s.

Fig. 11 - Measured response of the PDD ( $V_{o}$ , solid trace) to an input sequence of two semigaussian pulses of different amplitude ( $V_{i}$ , dashed trace). Digital input and output of the PDD are also shown. After each read request, the PDD presents the next analog sample at the output. Two samples can be stored in the PDD before readout.

In Fig. 11 the two *peak-found* pulses generated by the PDD logic in correspondence of each peak, the *read* request and PDH *reset* signals generated by the external logic are also shown. For every *read* pulse the PDD makes available at

the output a peak height, following the same order of the input; in correspondence of each *reset* pulse the PDD resets the last PDH read. The discharge of the output node when all output switches  $S_o$  are open can be observed. The two readings are separated by  $15\mu$ s. The dual PDD was tested by using a sequence of two input pulses of different amplitudes separated by 4  $\mu$ s. In Fig. 11, for example, the pulses are 360mV and 2.55V. The logic was designed so that the next PDH available for processing was the last one read. In this way each amplitude was alternatively stored in each PDH in *ping-pong* fashion.

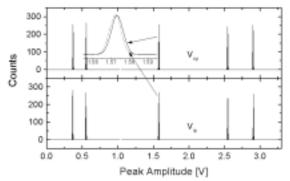

Fig. 12 - Measured input and output peak histograms (1k counts) for Vin = 0.38, 0.57, 1.59, 2.56, and 2.92 V. The insets shows a detail for the  $\approx$ 1.5V spectral line.

We measured the amplitudes of the input peaks and of the outputs for several pairs of amplitudes ranging from  $\approx$  380mV up to  $\approx$  2.9V using an external 12 bit ADC. The amplitude histograms are shown in Fig. 12.

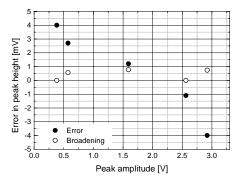

Figure 13 Difference in mean (absolute error) and standard deviation (broadening, quadratic subtraction) of the peak amplitude histograms at the input and output of the PDD. The corresponding spectra are shown in Fig. 12.

From the histograms of peak amplitudes we extracted the first and second order statistic values in order to evaluate if any line broadening was occurring as consequence of pingpong alternation of the two different PDHs for each amplitude. The results, reported in Figure 13, show the negligible impact of the use of multiple PDHs on the accuracy of the peak height.

## V. CONCLUSIONS

The present work demonstrates that the two-phase peak

detect and hold circuit overcomes the major limitations of the classical single-phase approach. By re-using the tracking amplifier as an output follower, offset and CMRR errors are eliminated and the circuit can maintain 0.2% *absolute* accuracy within 300mV from the rails. Taking advantage of the offset-free operation, we have also developed an analog derandomizer using two peak detectors in parallel with a data-driven controller. First experimental results show that the derandomizer functions properly and introduces negligible error. The performance of the PDD circuit is summarized in Table 2.

In the future we plan to extend these techniques to include accurate time measurement and to build an efficient, selftriggered readout for large detectors.

| Parameter           | Value                     |

|---------------------|---------------------------|

| Technology          | 0.35 µm DP4m CMOS         |

| Supply voltage      | 3.3 V                     |

| Input voltage range | 0.3 – 3 V                 |

| Absolute accuracy   | 0.2 % at 500ns            |

|                     | 0.7% at 200ns             |

| Droop rate          | 0.25 V/s                  |

| Derandomizing       | 2 events                  |

| Power dissipation   | $3.5 \text{ mW} \times 2$ |

#### **ACKNOWLEDGEMENTS**

The authors would like to acknowledge V. Radeka (BNL) and A. Hrisoho (LAL, Orsay) for help and encouragement with this project and John Triolo for the technical assistance.

#### REFERENCES

[1] M. W. Kruiskamp, D. M. W. Leenaerts, "A CMOS peak detect sample and hold circuit", IEEE Transactions on Nuclear Science, Vol. 41, No. 1, pp. 295-298, 1994.

[2] K. Koli, K. Halonen, "Low voltage MOS-transistor-only precision current peak detector with signal independent discharge time constant", Proc. IEEE International Symposium on Circuits and Systems (ISCAS'97), Hong Kong, June 1997.

[3] A. M. L. S. Morgado, J. B. Simões, J. Landeck, M. F. Correia, P. Almeida, J. L. Malaquias, C. M. Correia, "A pulse processing station", Proc. IEEE Nuclear Science Symposium (NSS'97), Albuquerque, NM, USA, November 1997.

[4] L. Fabris, P. G. Allen, J. J. Bucher, N. M. Edelstein, D. A. Landis, N. W. Madden, D. K. Shuh, "Fast peak detector stretchers for use in XAFS applications", Proc. IEEE Nuclear Science Symposium (NSS'98), Toronto, Canada, November 1998.

[5] K. O. Wessendorf, J. C. Lund, B. A. Brunett, G. R. Laguna, J. W. Clements, "Very low-power consumption analog pulse processing ASIC for semiconductor radiation detectors", Proc. IEEE Nuclear Science Symposium (NSS'98), Toronto, Canada, November 1998.

[6] M. N. Ericson, M. L. Simpson, C. L. Britton, M. D. Allen, R. A. Kroeger, S. E. Inderhees, "A low-power, CMOS peak detect and hold circuit for nuclear pulse spectroscopy", IEEE Transactions on Nuclear Science, Vol. 42, No. 4, pp. 724-728, 1995.

[7] C. Fiorini, A. Pullia, P. Novellini, E. Gatti, A. Longoni, W. Buttler, "A monolithic implementation of a switched-current "wheel" amplifier for multi-channel silicon drift detectors", Proc. IEEE Nuclear Science Symposium (NSS'98), Toronto, Canada, November 1998.

[8] U. Jagadish, C. L. Britton Jr., M. N. Ericson, W. L. Bryan, W. G. Schwarz, M. E. Read, R. A. Kroeger, "A preamplifier-shaper-stretcher integrated circuit system for use with Germanium strip detectors", IEEE Transactions on Nuclear Science, Vol. 47, No. 6, pp. 1868-1871, 2000.

[9] G. De Geronimo, A. Kandasamy, P. O'Connor, "On the analog CMOS peak detect and hold circuit – Part 1. Analysis of the classical configuration", this issue.

[9] M. J. M. Pelgrom, M. Vertregt, "CMOS technology for mixed signal ICs", Nuclear Instruments and Methods in Physics Research, Vol. A 395, pp. 298-305, 1997.

[10] C. C. Hung, M. Ismail, K. Halonen, Veikko Porra, "A low-voltage rain-to-rail CMOS V-I converter", IEEE Transactions on Circuits and Systems, Vol. 46, No. 6, pp. 816-820, 1999.

[11] A. Ryan, M. Neag, O. McCarthy "CMOS operational transconductance amplifier for PRML read channel applications", Proc. IEEE International Symposium on Circuits and Systems (ISCAS'99), Orlando, Florida, May 1999.

[12] H. Elwan, W. Gao, R. Sadkowski, M. Ismail "A low voltage CMOS class AB operational transconductance amplifier", Proc. IEEE International Symposium on Circuits and Systems (ISCAS'99), Orlando, Florida, May 1999.