**BAE SYSTEMS**

# Advanced Microprocessor Technologies

## and Challenges for Space Applications

Nadim F. Haddad

(nadim.haddad@baesystems.com)

2001 IEEE Microelectronics Reliability and Qualification Workshop

December 11-12

Pasadena, CA

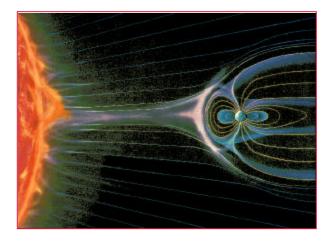

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

**BAE SYSTEMS**

Nikkei Science, Inc. of Japan, by K. Endo

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

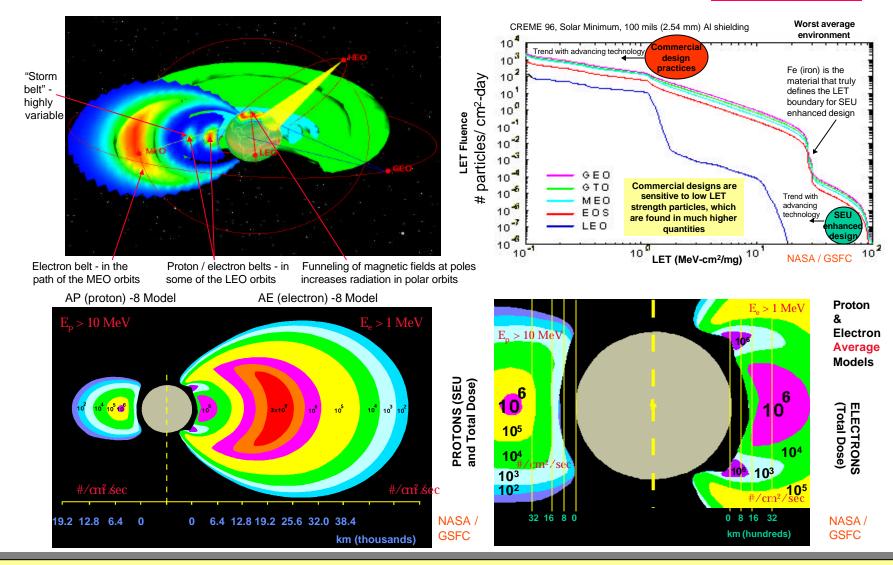

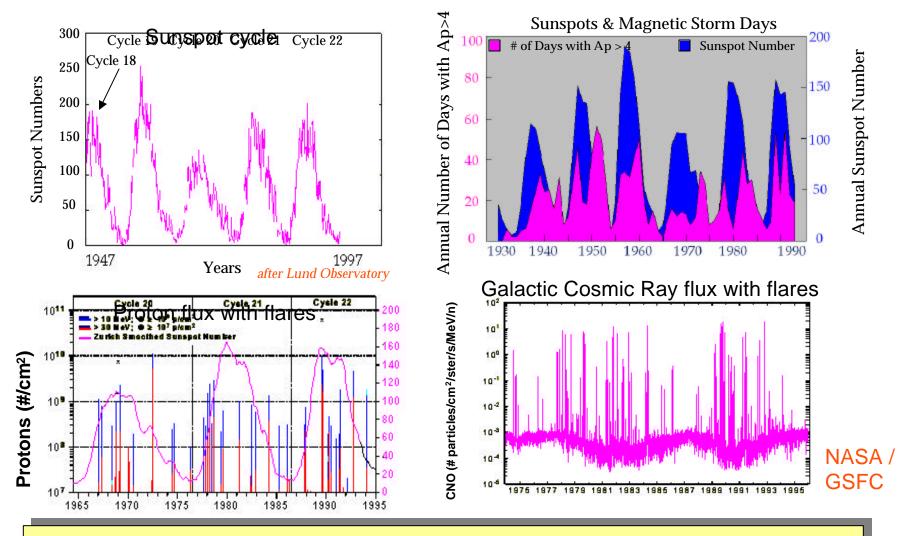

## **Variations in Radiation Flux Density**

BAE SYSTEMS

### Variability of radiation environments affects the applicability of COTS in space

Cleared for Public Domain Release © 2001 BAE SYSTEMS DoD/ 01-S-1376, 2/01 All Rights Reserved

## **Extreme Conditions - Solar Flares**

#### BAE SYSTEMS

## Space environment is very variable - solar flares are unpredictable and create a severe environment

Cleared for Public Domain Release © 2001 BAE SYSTEMS DoD/ 01-S-1376, 2/01 All Rights Reserved

## **Issues Associated with Space**

### BAE SYSTEMS

- Radiation environment

- <u>Total lonizing Dose</u> (TID) accumulation of radiation over time

- Prompt Dose ability to function during a massive burst of radiation

- <u>Survivability</u> ability to function after a massive burst of radiation

- <u>Single Event Effects</u> (SEE) soft or hard errors as the result of the penetration of a single charged particle

- <u>Single Event Upset</u> (SEU) state change of a storage node

- <u>Single Event Transient</u> (SET) pulse injection into combinational logic

- <u>Single Event Gate Rupture</u> (SEGR) destruction of the gate of a transistor

- <u>Single Event Latchup</u> (SEL) "lock-up" of a device; must remove power to reset

- <u>Single Event Burnout</u> (SEB) Burnout, especially in power devices

- Wide temperature range and stresses

- High reliability

- Mechanical stresses

- Severe mass and power constraints

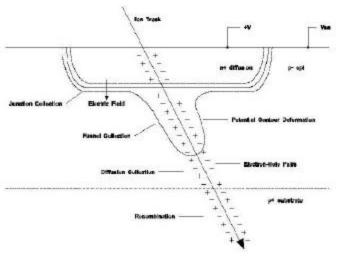

Charge from single event impact

## Spacecraft electronics are expected to overcome severe environmental conditions

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

## **Trends in Commercial Technology**

|                                  | Commercial CMOS Technology  |                             |                 |                     | <u>ogy</u>          | У        |                     |                |

|----------------------------------|-----------------------------|-----------------------------|-----------------|---------------------|---------------------|----------|---------------------|----------------|

| Environment                      | 0.8 <b>m</b> m              | 0.5 mm                      | 0.35 <b>m</b> m | 0.25 <b>m</b> n     | 0.18 <b>m</b> m     | 0.13 mm  | 0.18 mm<br>SOI      | <u>Hard</u>    |

| Total Dose<br>(Krad(Si))         | 10 - 20                     | 20 - 40                     | 20 – 50         | 40 - 100            | 40 - 150            | 40 – 150 | 30 – 50             | 200 –<br>1,000 |

| SEU (u/b-d)<br>(90% W.C.<br>Geo) | 1E-7                        | 1E-6                        | 2E-6            | 5E-6                | 1E-5                | >1E-5    | 1E-6 to<br>1E-7     | < 1E-10        |

| Prompt<br>Dose Upset<br>(rad/s)  | 1E7                         | 1E7-1E8                     | 1E7-1E8         | 1E7-1E8             | 1E7                 | <1E7     | 1E8                 | > 1E9          |

| Latch up                         | Generally<br>prone          | Some<br>prone               | Some<br>prone   | Generally<br>immune | Generally<br>immune | ?        | Possibly self-latch | Immune         |

| Neutron<br>(u/cm <sup>2</sup> )  | 1E14<br>(limited<br>by TID) | 1E14<br>(limited<br>by TID) | 1E14            | 1E13-<br>1E14       | ?                   | ?        | ?                   | 1E14           |

Trends in commercial technologies have not always been favorable for spaceborne application, given the various failure mechanisms

#### Effect of Scaling on Single Event Upset **BAE SYSTEMS** SIZE DURATION STRENGTH Diffusion 1.0um node $\wedge V = \wedge Q/C$ @ 5 MHz, pulse = 100 ns.0.18um Nodal cap < 1/10xתוקהאקרוקוקוקוקות הקה הקורקהוקוקה הקורקוקה הקה הקה הקורקוקוקוקוקו Current drive < 1/3x@ 500 MHz, Charge pulse = 1 ns.Therefore, susceptibility of collection 1.0µm CMOS to an area LET=10-20 translates to SEU Pulse = 0.3 ns. susceptibility of 0.18 µm

## Technology scaling is driving a multi-exponential increase in sensitivity to SEU / SET

CMOS to an LET = 0.3-0.7

Cleared for Public Domain Release DoD/ 01-S-1376, 2/01 © 2001 BAE SYSTEMS All Rights Reserved

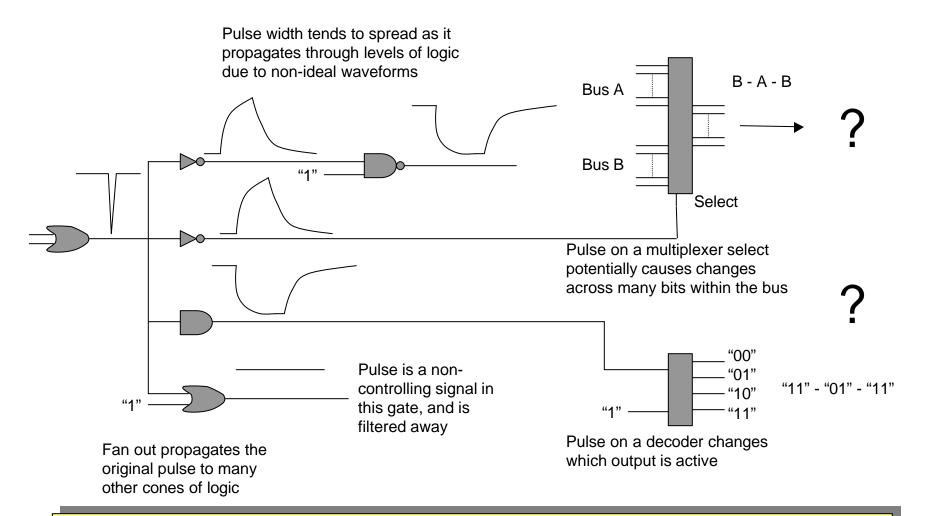

## **Single Event Transient (SET)**

#### BAE SYSTEMS

An injected pulse can propagate far beyond it's point of inception, based on logic design paths

## **SEU Susceptibility in Dynamic Circuitry**

**BAE SYSTEMS**

- Global block select decoder

- Classic pre-charged dynamic circuit used in: decode, buffers, datapaths, logic, and clocks

- Operation:

- CLOCK = "0" results in output pre-charge to "1"

- CLOCK = "1" results in valid signal output, based on input conditions

- Very soft, due to:

- Small bleeder device holding "1" state

- Switching due to SET pulse on clock line

- Upset will select wrong block of data (1 block = 32K bits)

| VDD<br>IB4<br>S<br>G<br>G<br>Q<br>CLOCK ■<br>CLOCK ■  | Tiny "bleeder" device<br>holds output to "1"<br>S [183<br>AØ X O BLOCK                                                                                                                                                                                                                                                                             | <_SEL |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                       | Clock line and devices<br>dynamically control<br>output state                                                                                                                                                                                                                                                                                      |       |

| B ■ G   A<br>B ■ G   A<br>IB8 D<br>IB8 D<br>C ■ G   A | Input devices<br>configured as<br>3-input NAND                                                                                                                                                                                                                                                                                                     |       |

| GNC                                                   | ranene enen enen enen enen enen enen eren eren eren eren bieten beide bezen bei bezen eren bieten beid bezen b<br>Kalen beid bezen beid beid beide beid beide beid beide beide beid bezen beid bezen beid beide beid beide beid<br>Tenens beid beides beid beid beide beid beide |       |

## Exotic circuit design techniques (common in recent COTS products) increase density and performance, but are more susceptible to SEU/SET

# Estimated SEU Rates by Commercial Processor Generation

#### BAE SYSTEMS

|   | RSC - "G0(?)"                                                                                                                   | 601 - "G1"                                 | 603 / 603e - "G2"                                                                | 750 - "G3"                                   | 7400 - "G4"                                   |

|---|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|

|   | <b>Fechnology:</b> 0.8 μm<br><b>Fransistors:</b> 1.0 M<br><b>Supply:</b> 3.6 V<br><b>Speed:</b> 33 MHz<br><b>Released:</b> 1992 | 0.6 µm<br>2.8 M<br>3.6 V<br>50 MHz<br>1993 | 0.5 / 0.35 µm<br>1.6 / 2.6 M<br>3.3 V / 2.5 V<br>80 MHz / 200 MHz<br>1994 / 1995 | 0.25 µm<br>6.4 M<br>2.5 V<br>266 MHz<br>1997 | 0.18 µm<br>10.5 M<br>1.8 V<br>450 MHz<br>1999 |

| ç | Estimated SEU Rate<br>90% GEO:<br>1 / 60 days<br>During Flares:<br>0.02 - 2 / min                                               | 1 / 8 days<br>0.1 - 9 / min                | 1 / 5 days / 1 / day<br>0.2 - 14 /min / 1 - 100 / min                            | 1 / hour<br>0.3 - 27 / sec                   | 3 / hour<br>1 - 100 / sec                     |

\* SET upsets begin to increase at 0.35 micron and then accelerate, due to small devices, low supply, and high clock rates

Across Generations, the Increase in SEU/SET Susceptibility is Dramatic

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

## **Total Dose Mitigation**

| Total Dose Environment for Various Orbits (10 Year Mission Assumed) |            |                       |                   |  |  |  |

|---------------------------------------------------------------------|------------|-----------------------|-------------------|--|--|--|

| Or                                                                  | <u>bit</u> | Total Dose (krad(Si)) |                   |  |  |  |

| Altitude(Km) Inclination(Degree)                                    |            | <u>100 mil Al</u>     | <u>250 mil Al</u> |  |  |  |

| 850                                                                 | 28         | 22                    | 12                |  |  |  |

| 1,350                                                               | 90         | 56                    | 38                |  |  |  |

| 1,400                                                               | 53         | 130                   | 50                |  |  |  |

| 1,500                                                               | 30         | 240                   | 100               |  |  |  |

| Geo                                                                 | 00         | 400                   | 20                |  |  |  |

| 1/2Geo                                                              | 60         | 3,000                 | 100               |  |  |  |

|                                                                     |            |                       |                   |  |  |  |

Shielding is an effective way to reduce total dose, but it comes at a cost... It is also ineffective in mitigating single event effects

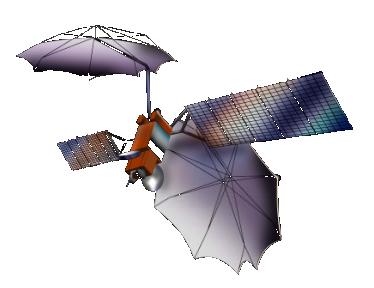

## **SEU Mitigation - Redundant System Example**

### BAE SYSTEMS

### Hardware redundancy functions

- Multiple voting functions check the CPU outputs, confirming correct results or identifying the "bad" CPU

- If a fail is detected:

- The controller uses that information to shut down (hard reset) the failing CPU

- Begins recovery routine

- The selector sends good output to the I/O and/or memory

- Approximately two cycles of latency are added to I/O and memory operations

### • Software redundancy functions

- Regular "sweep" issued to cause output for checking

- Either clears key embedded memories (caches, branching) during each regular sweep, or during a recovery operation

- Match up the processors at a "work task" boundary, and start simultaneous processing again

## Redundant systems operate by detecting errors in processing functions after they occur and removing them through voting

# Applicability of Redundant COTS Electronics in Space

## **Orbital variations**

- Low LEO is the most benign (below 800 km)

- Polar more severe than near equatorial

- Upper LEO is more severe for both Total Dose and SEU

- The South Atlantic Anomaly is the worst case in LEO orbits

- MEO is worst for Total Dose

- GEO is worst for Cosmic Rays

- Long term missions encounter extreme conditions at some point (solar flares and coronal mass ejections); these conditions REQUIRE SEU immune design redundancy is not applicable

## Application variations

**BAE SYSTEMS**

- Short term applications (example: shuttle) may be timed around extremes

- Some unpredictability exists

- Some years are better than others

- Applications that can accept outages (1-4 days in length) can simply shut down during solar flares (example: geology, telescope)

- New ASIC designs can address some of the problem in design

- TMR at each latch

- Error correct embedded memories

- Addressing SET errors is more difficult

- Real time / critical applications have a problem; they CAN'T shut down (example: cell phone, internet, video, weather, global positioning, military)

The Ability to Consider TMR is a Function of Both Orbit and Application

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

# Redundant Modern Commercial Processors in Space

### BAE SYSTEMS

## Size, weight, and power (SWAP)

### • Size

- TMR requires significant board space

- 3-4 CPUs

- Voting Chip

- Will not fit on a 3U format

### • Weight

About 2X weight of Single Processor Solution

### • Power

- Increased Component Count

- Increased processing for upset checking / recovery

- About 3X Power

### Software effort and overhead

- Effort

- "Upset checking" routine

- Split application code for regular checking

- Recovery routine

### Overhead

- Interrupted processing

- Increased check pointing

- 50% Performance loss Typical

- (through HW & SW)

## <u>SEU / SET</u> susceptibility

- Upset mechanisms

- Dynamic logic

- Storage nodes

- Transient (SET) propagation

### • Flux rate

- GCR Cause 1-2 upsets / hr

- Protons at LEO cause

0.3-0.7 upsets / hr

- Solar flares cause 0.1 20 upsets / sec

### Recovery

- TMR recovery will typically require several minutes

- Upsets may not be detected in time to respond

Expect trouble during

- flares

### Product cost

### Component costs

- Rad-hard voting chip has high recurring cost in addition to NRE

- Commercial CPUs have cost advantage

### Software costs

- NRE for development of checking and recovery routines

- Board costs

More complex board design with lead time vs. a standard radhard product

### **Commercial Processors, Even with Redundancy, Have Issues and Exposures** that Far Outweigh their Benefits Compared to Enhanced Processor Solutions

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

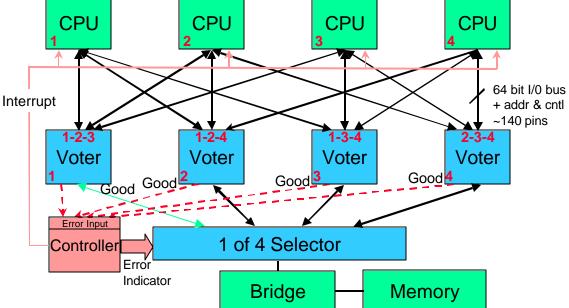

## **SEU Mitigation - Redundant Circuitry Example BAE SYSTEMS**

Redundant storage cells with time shifted clocks fight SET upsets by attempting to filter out the pulse prior to capturing it

Cleared for Public Domain Release DoD/ 01-S-2540, 4/01 © 2001 BAE SYSTEMS All Rights Reserved

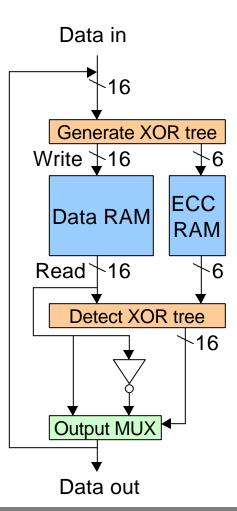

## **SEU Mitigation - In-line Error Correction**

BAE SYSTEMS

- Typical uses

- Memory subsystems

- Communication links

- Sequence for Single Error Correct Double Error Detect (SECDED):

- Generate error bits via XOR based on masking

- Detect error via XOR with masking

- No mismatch indicates good data

- Valid value identifies bit in error

- Invalid value defines uncorrectable errors

- Multiplex data or inversion bit-by-bit to correct

- Radiation mitigation:

- Employ variable rate "scrubbing" (read, test, correct and write back if needed) sequence at varying rates, based on rate of errors induced

- Useful until error rate exceeds ability to fix or ability to perform both function and correction

- Combination with hardened Cache reduces functional access demand

## Error correction removes errors that occur within stored memory by generating codes that uniquely identify the validity of each bit of data

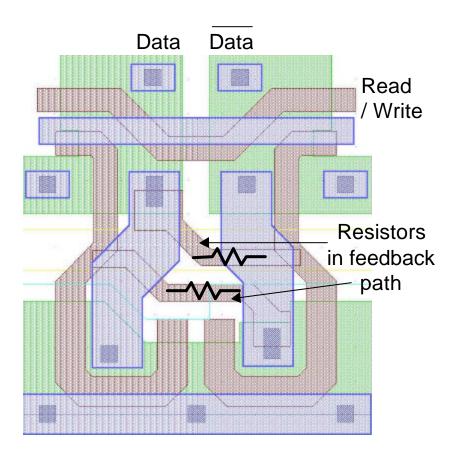

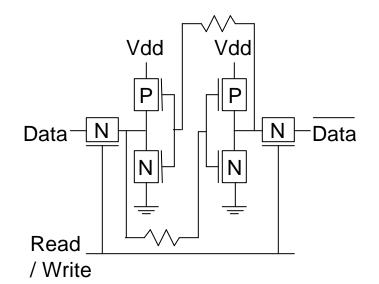

## **SEU Mitigation - Hardened Circuitry Example**

BAE SYSTEMS

- Large resistance in the feedback path fights state change in the cell via RC time constant

- Typically employs unique manufacturing process steps

- Adverse effects on Write time and circuit density

## Radiation hardened circuits prevent upsets through design techniques that fight against the charge deposit from the impact

Cleared for Public Domain Release © 2001 BAE SYSTEMS AI

DoD/ 01-S-2540, 4/01 All Rights Reserved

#### BAE SYSTEMS

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

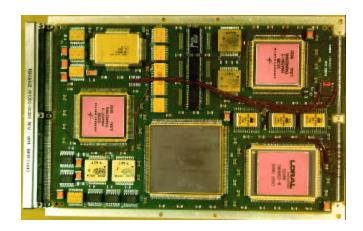

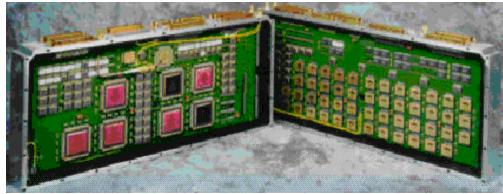

# 90 satellites currently on orbit with 286 single board computers\*

\* As of November 30, 2001

Cassini GVSC processor

### SBIRS Low/Orbview RAD6000™

CCP drop in tray (GVSC) Over 500 flight boards delivered or ordered for new launches through 2006

VME 6U RAD6000<sup>TM</sup> board \* \* as used on FHLP

Our processors have been the standard in space for many years, with millions of hours of flawless operation in a variety of applications

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation DoD/ 99-S-2438, 7/99 All Rights Reserved

### BAE SYSTEMS

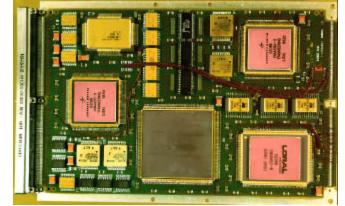

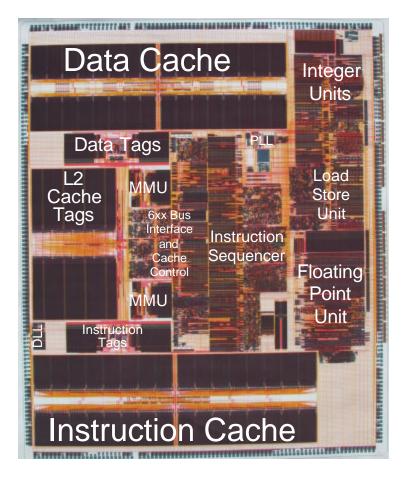

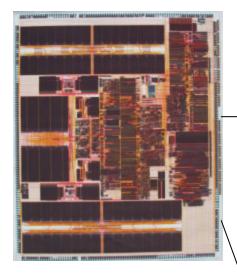

# Three generations of radiation hardened microprocessors

#### BAE SYSTEMS

- 1991 GVSC 1750 1.0 μm Radiation Hardened CMOS – MIL-STD-1750A architecture – 4 by 88 sq mm – 0.3 M transistors

- 20 MHz

- 3 MIPS

### 1996 RAD6000™

- $0.5\ \mu m$  Radiation Hardened CMOS

- RS/6000 "Power" architecture

- 145 sq mm

- 1.1 M transistors

- 33 MHz

- 35 MIPS

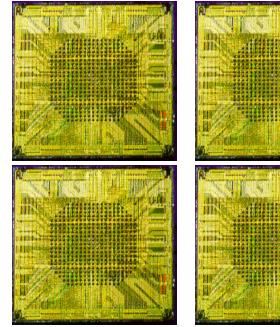

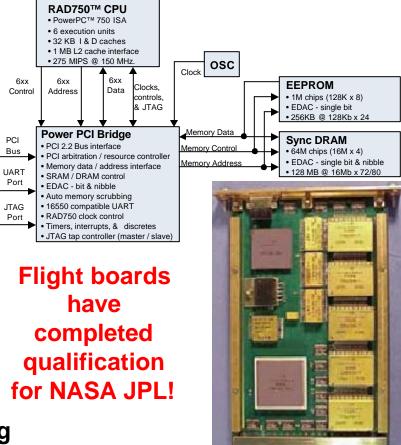

### 2001 RAD750™

$0.25\,\mu m$  Radiation Hardened CMOS

- PowerPC architecture family

– 130 sq mm

- 10.4 M transistors

- 133 166 MHz (up to 200 as available)

- -240 300 MIPS (up to 366 as available)

## The RAD750 represents our third generation product, with architectural and technological enhancements that improve power/performance

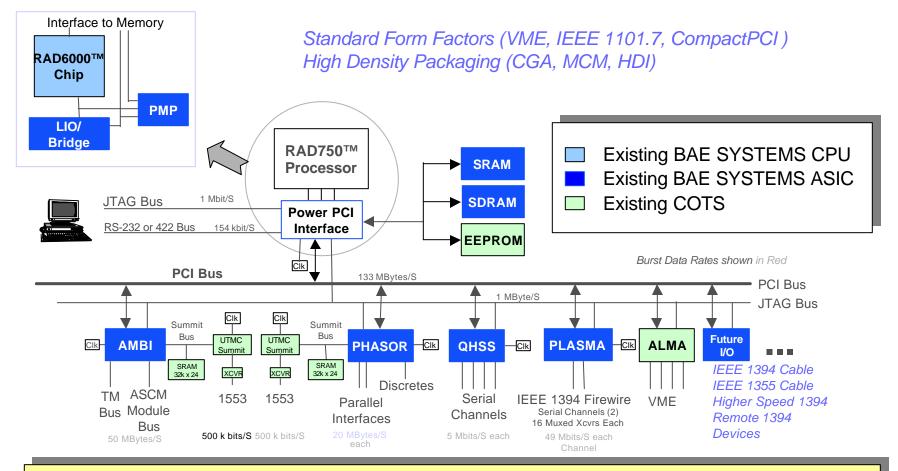

## RAD750<sup>™</sup> - Power PCI RAD6000<sup>™</sup> architecture compatibility

## The RAD750<sup>™</sup> and Power PCI easily replace the current RAD6000<sup>™</sup> and LIO in our processor board architecture

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

## **RAD750<sup>™</sup> specifications**

#### BAE SYSTEMS

| Specifications                                              |                                                                                                     |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Processor Speed                                             | 110 to 133 MHz                                                                                      |

| Process Technology                                          | 0.25 um (0.18 um Leff) CMOS, 6 levels of metal                                                      |

| Die Size                                                    | 10.4 mm. by 12.5 mm.                                                                                |

| RAD750™ Performand<br>without L2 (est)<br>with 1MB L2 (est) | e<br>6.5 SPECint95 3.9 SPECfp95 @ 150 MHz.<br>7.0 SPECint95 4.7 SPECfp95 @ 150 MHz.                 |

| Signal I/O                                                  | 256 (including L2 port)                                                                             |

| Power Supply                                                | 2.5 V + / - 5% core<br>2.5 or 3.3 V + / - 10% I/O                                                   |

| Power Dissipation                                           | 5.0 watts at 133 MHz, 2.5V                                                                          |

| Temperature Range                                           | -55°C to +125°C                                                                                     |

| Packaging                                                   | 25.0 mm. by 25.0 mm. by 6.22 mm.<br>360 pin Column Grid Array (CGA)                                 |

| Mass                                                        | 9.0 grams                                                                                           |

| Radiation Hardness                                          | Total Ionizing Dose: 200 Krad (Si)<br>SEU: 1E-10 upsets / bit-day (W.C. 90% GEO)<br>Latchup: Immune |

| Mean Time Between<br>Failures (MTBF)                        | > 4.3M hours                                                                                        |

### The final design has completed characterization and qualification

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

## **RAD750<sup>™</sup> Testing Status**

#### BAE SYSTEMS

- RAD750<sup>™</sup> Testing was completed October 31 (functional equivalency to PowerPC<sup>™</sup> 750 verified)

- Environmental testing proved successful across the full military temperature and voltage ranges

- Performance specification will be 110 MHz 133 MHz based upon screening levels

- Radiation testing results support flight requirements

- No latchup nor gate rupture

- -TID >200Krad(Si)

- SEU <1E-10 error/bit.day

- Threshold LET(@10% of Saturation) = 45 MeV/mg/cm<sup>2</sup>

- RAD750<sup>™</sup> Specification Updated to reflect testing

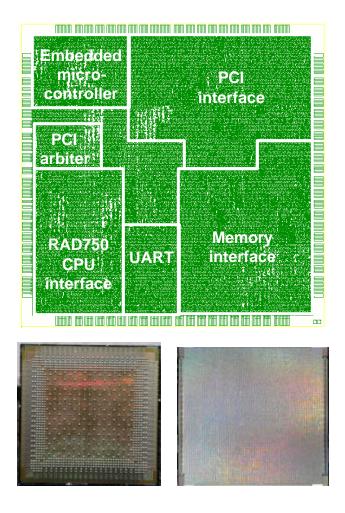

## **Power PCI ASIC specifications**

### **BAE SYSTEMS**

| Specification           | IS                                                                                                     |

|-------------------------|--------------------------------------------------------------------------------------------------------|

| Clock Speed             | 33 MHz                                                                                                 |

| Process Technology      | 0.50 um Leff CMOS, 5 levels of metal                                                                   |

| Die Size                | 12.7 mm. by 12.7 mm.                                                                                   |

| Cells / Gates / Latches | 926K / 700K / 26K                                                                                      |

| PCI Peak Bandwidth      | 130 MB/s write 90 MB/s read                                                                            |

| Signal I/O              | 456 (+ <i>test</i> )                                                                                   |

| Power Supply            | 3.3 V + / - 10% core and I/O                                                                           |

| Power Dissipation       | 1.5 W                                                                                                  |

| Temperature Range       | -55°C to +125°C                                                                                        |

| Packaging               | 32.5 mm. By 32.5 mm. By 6.22 mm.<br>624 pin Column Grid Array (CGA)<br>with flip-chip C4 mount         |

| Radiation Hardness      | Total Ionizing Dose: >1Mrad (Si)<br>SEU: < 1E-10 upsets / bit-day (W.C.<br>90% GEO)<br>Latchup: Immune |

| Mass                    | 14.5 grams                                                                                             |

## The Power PCI has been integrated on a 3U CompactPCI single board computer

Cleared for Public Domain Release © 2001 BAE SYSTEMS

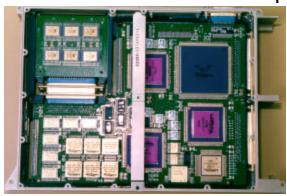

## Conduction Cooled CompactPCI® 3U Format RAD750<sup>™</sup> Processor Board

BAE SYSTEMS

| Specifications                       |                                                                                                                          |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Form Factor                          | CompactPCI 3U (100 mm x 160 mm.)<br>Weight: 549 grams                                                                    |

| Processor                            | RAD750 <sup>™</sup> 240 Dhrystone 2.1 MIPS @ 133 MHz.                                                                    |

| Radiation Hardness                   | Total Ionizing Dose: > 100 Krad (Si)<br>SEU: < 1E-5 upsets/day (W.C. 90% GEO)<br>Latchup: Immune                         |

| Performance (estimated)              | 5.8 SPECint95 3.5 SPECfp95 @ 133 MHz.                                                                                    |

| PCI Backplane Bus                    | 32 bit, 33 MHz., PCI version 2.2<br>Peak Bandwidth: 130 MB/s write 90 MB/s read<br>Can be keyed for System or Agent Slot |

| Power Supply                         | 3.3 V + / - 10%<br>(2.5 V generated via on-board regulator)                                                              |

| Power Dissipation (typ)              | 10 W                                                                                                                     |

| Temperature Range                    | -55°C to +125°C                                                                                                          |

| Mean Time Between<br>Failures (MTBF) | Greater than 390K hours                                                                                                  |

### Currently available in flight, engineering and low cost commercial versions

## The RAD750<sup>™</sup> product line introduces a completely new era of both onboard processing capability and space standard products

Cleared for Public Domain Release © 2001 BAE SYSTEMS

## **RAD750<sup>™</sup> Software Development Environment BAE SYSTEMS**

### Software Development System

- Pentium personal computer

- Windows NT Operating System

- Ethernet connection to RAD750

- Corellis JTAG interface

- RAD750 or COTS PowerPC Board

### **Green Hill Multi and GNU Tools**

- Optimized C, C++, Ada compilers

- Source level debugger

- Mixed language integration

- Version control system

- Program builder

- Editor

## WindRiver VxWorks OS

- High performance multi-tasking kernal

- Networking capability

- Device independent I/O

- Dynamic load of user programs

- Highly configurable execution environment

- "Tornado" Software development and debug tools

### **BAE SYSTEMS Supplied Software**

### **Board Support Package (BSP)**

• VxWorks compatible

### I/O device drivers Start-Up ROM (SUROM)

- System "Reset handler"

- On-board diagnostics

- CPU and Power PCI self-test

- Memory test

- Bootstrap image load into RAM

- Test and initialize board hardware

- Fault recovery during restart

### A complete environment, based on our RAD6000<sup>™</sup> experience, eases RAD750<sup>™</sup> software development

Cleared for Public Domain Release © 2000 Lockheed Martin Corporation

## Hardened Processor Flight Heritage

| <u> 1995 - Novemi</u> | oer, 2      | 001         | <u> 2001 - 20</u>       | 03          |             | <u> 2004 - 2</u>   | 006         |             |

|-----------------------|-------------|-------------|-------------------------|-------------|-------------|--------------------|-------------|-------------|

| (Launched)            |             |             | (Under Contract)        |             |             | (Under Contract /  | Plan)       |             |

| <u>SATELLITE</u>      | <u>SATs</u> | <u>SBCs</u> | <u>SATELLITE</u>        | <u>SATs</u> | <u>SBCs</u> | SATELLITE          | <u>SATs</u> | <u>SBCs</u> |

| Agila / APSTAR-2R     | 2           | 4           | ChinaSat 8              | 1           | 2           | Intelsat 903-905   | 3           | 12          |

| Cassini               | 1           | 7           | Globalstar (16 bit)     | 4           | 8           | KaStar 1,2         | 2           | 4           |

| EchoStar 5            | 1           | 2           | Intelsat 902            | 1           | 4           | Messenger          | 2           | 10          |

| Garuda 1 (ACeS)       | 1           | 2           | SS/L DBS-3              | 2           | 4           | Storage Unit       | 2           | 4           |

| Globalstar (16 bit)   | 52          | 104         | Sky 2A (MCI)            | 1           | 2           | Astrolink 1-4      | 4           | 8           |

| GOES L, M             | 2           | 4           | Telstar 8-9 (Skynet)    | <u>3</u>    | <u>6</u>    | Coriolis           | 1           | 1           |

| Intelsat 901          | 1           | 4           |                         |             |             | AEHF (Bus)         | 5           | 10          |

| NSTAR A,B             | 2           | 4           |                         |             |             | GENESIS            | 1           | 2           |

| SS/L DBS-2            | 1           | 2           |                         |             |             | MIRO               | 1           | 2           |

| PAS 6 - 8             | 3           | 6           |                         |             |             | MSL                | 1           | 2           |

| Sirius 3 - CD Radio   | 3           | 6           |                         |             |             | Muses-C            | 1           | 2           |

| Sky 1A (MCI)          | 1           | 2           |                         |             |             | SIRTF              | 1           | 4           |

| Telstar 5-7 (Skynet)  | 3           | 6           |                         |             |             | Solstice/VCL       | 2           | 3           |

| TEMPO 2               | 1           | <u>2</u>    |                         |             |             | SWIFT              | 1           | 4           |

| 16 Bit Computers      | 74          | 155         | <u>16 Bit Computers</u> | 12          | 26          | Solar X-Ray        | 1           | 2           |

| Deep Space 1          | 1           | 1           | ETS-8                   | 1           | 4           | TES                | 1           | 2           |

| FAISat                | 1           | 1           | Globalstar (32 bit)     | 4           | 8           | TRIANA             | 1           | 3           |

| Fuse                  | 1           | 1           | Gravity Probe B         | 1           | 9           | DRP                | 1           | 4           |

| Globalstar (32 bit)   | 52          | 104         | HESSI                   | 1           | 1           | X-2000             | 5           | 20          |

| Mars Odyssey          | 1           | 2           | HIRDLs                  | 1           | 2           | AEHF (Payload)     | 5           | 30          |

| MightySat 1           | 1           | 1           | MightySat 2             | 1           | 1           | Athena             | 1           | 1           |

| Orbiter/Lander -X     | 3           | 7           | C/NOFS                  | 1           | 1           | Classified         | 12          | 16          |

| Mars Pathfinder       | 1           | 1           |                         |             |             | CloudSat           | 1           | 2           |

| LMA (STEX, Stardust)  | 2           | 4           |                         |             |             | Deep Impact        | 1           | 2           |

| TSX-5                 | 1           | 1           |                         |             |             | Discovery          | 4           | 5           |

| RAD6000 Computers     | 64          | 123         | RAD6000 Computers       | 10          | 26          | Mars 03 Micro Miss | 1           | 2           |

|                       |             |             |                         |             |             | Secchi             | 1           | 4           |

|                       |             |             |                         |             |             | SBIRS Low          | 24          | 100         |

| In Space Today:       | 86          | Satellit    | es 278 Computer         | s           |             |                    |             |             |

|                       | 40.0        |             |                         |             |             |                    |             |             |

| Hours on Orbit:       | 16 B        | $\pi - 3.7$ | Million RAD6000 - 2.4   | Million     |             |                    |             |             |

|                       |             |             |                         |             |             | 16 Bit RA          | D6000       | RA          |

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

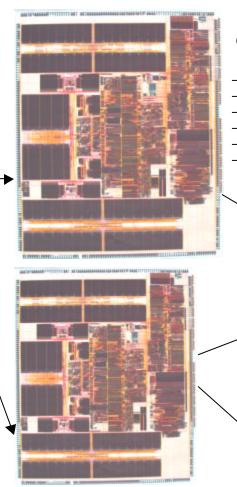

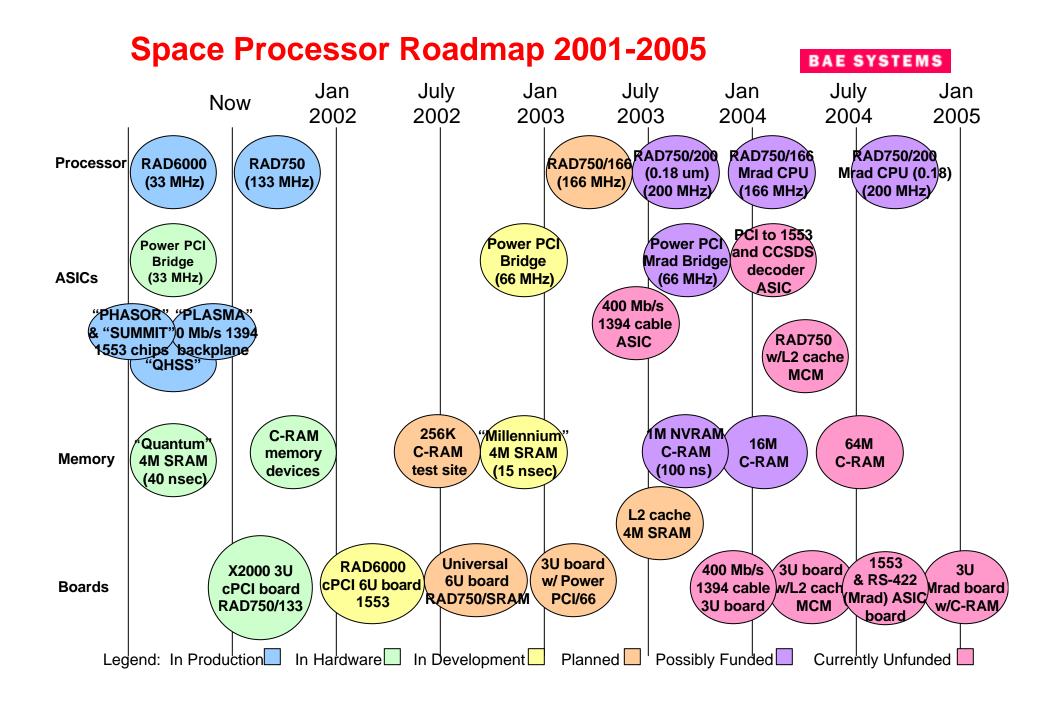

## RAD750 Forward Plan Options (2002-2006)

2002 RAD750<sup>™</sup> (pass 2) 0.25 μm Bulk CMOS (Comm'l Foundry) (Budgeted in '02)

- 130 sq mm

- 10.4 M transistors

- 166 MHz

- 300 MIPS

- 200 Krad (Si) Total Dose

- 1E-11 error/ bit-day SEU

2003 RAD750<sup>™</sup> 0.18 μm Bulk CMOS (Comm'l Foundry-w/ add'l product support)

- est. 90 sq mm

- 10.4 M transistors

- est .200 MHz

- 366 MIPS

- 200 Krad (Si) Total Dose

- 1E-11 error/ bit-day SEU

2004

#### BAE SYSTEMS

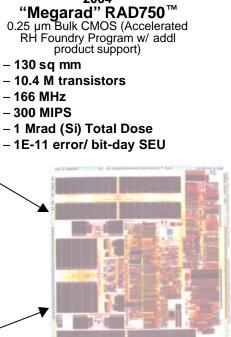

#### 2005 "Megarad" RAD750™

0.18 µm Bulk CMOS (Accelerated RH Foundry Program w/ prod spt)

- est. 90 sq mm

- 10.4 M transistors

- est. 200 MHz

- 366 MIPS

- 1 Mrad (Si) Total Dose

- 1E-11 error/ bit-day SEU

2006 "Megarad" RAD750<sup>™</sup> 0.18 μm Fully Depleted SOI/ SOS CMOS (Accelerated RH Foundry Program w/ process & product support)

- est. 90 sq mm

- 10.4 M transistors

- est. 250 MHz

- 457 MIPS

- 1 Mrad (Si) Total Dose

- 1E-11 error/ bit-day SEU

- The Environment

- Effect of Technology Migration

- Mitigation Schemes and Penalties

- Radiation Hardened Processors for Space

- Space Processor Roadmap

- Conclusion

## What it all Means

- Space microelectronics have to operate in a severe environment

- Users are driven to high performance electronics to address new and expanded applications:

- Available COTS are very sensitive to space radiation

- Variation in the radiation environment with orbit and over time is a major consideration in processor selection

- Mitigation techniques have significant impact on weight, power and performance.

- Technology scaling results in dramatically increased exposure to Single Event Effects in more modern semiconductor components

- Radiation Hardened Processors offer the best solution

- Capitalize on massive commercial investment in hardware and software

- Enhanced for the various environmental issues

- Offer the best power/performance/mass/volume alternative

### BAE SYSTEMS