## The CDF Silicon Vertex Trigger

Beauty 2005

Mauro Dell'Orso

Istituto Nazionale di Fisica Nucleare

Pisa – Italy

#### **Outline**

- CDF and the Silicon Vertex Trigger (SVT)

- Motivations

- Design

- Performance

- Upgrade

- Conclusions

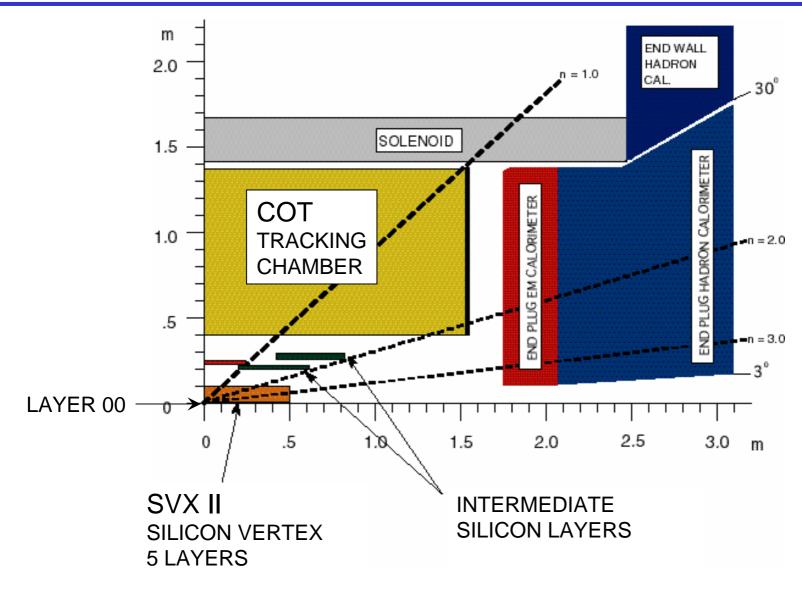

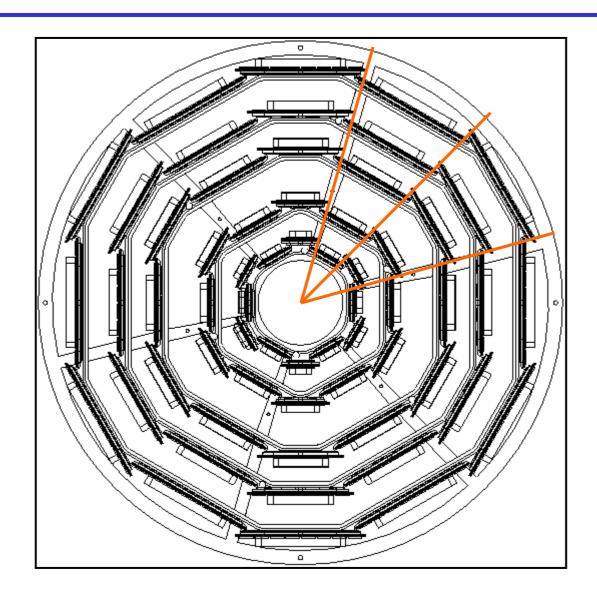

#### **CDF r-z view**

## **SVX II**

## Why and how?

- Trigger on B hadronic decays

- B physics studies, eg. CP violation in B decays, Bs mixing

- new particle searches, eg. Higgs, Supersymmetry

- A b-trigger is particularly important at hadron colliders

- large B production cross section for B physics

- high energy available to produce new particles decaying to b quarks

- overwhelming QCD background O(10<sup>3</sup>)

- need to improve S/B at trigger level

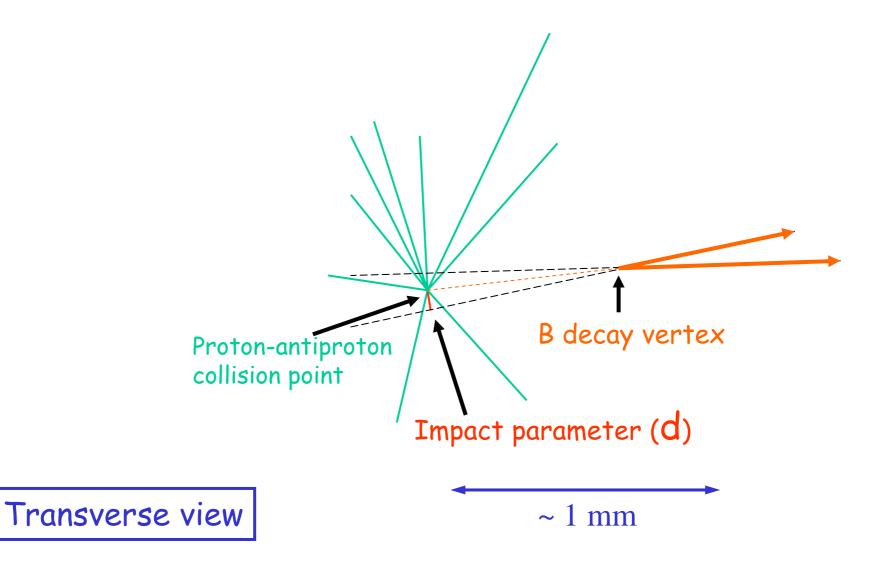

Detect large impact parameter tracks from B decays using the fact that τ(B)≈1.5 ps

Technical challenge!

primary vertex

## **Exploit lifetime to select b,c**

## **SVT: Input & Output**

#### Inputs:

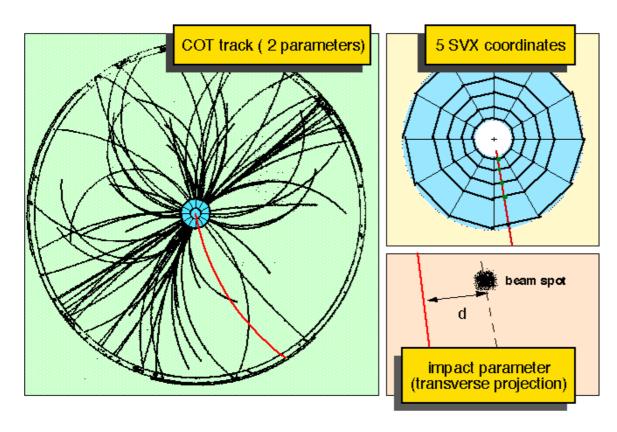

- L1 tracks from XFT  $(\phi, p_T)$

- digitized pulse heights from SVX II

#### **Functionalities:**

- hit cluster finding

- pattern recognition

- track fitting

#### **Outputs:**

reconstructed tracks(d, φ, p<sub>T</sub>)

## **SVT Design Constraints**

8

- 45 kHz input rate

- •O(10<sup>3</sup>) SVX strips/event

- •2-D low-res COT tracks

- •Latency O(10) μsec

- No Dead Time

- •Resolution ≈offline

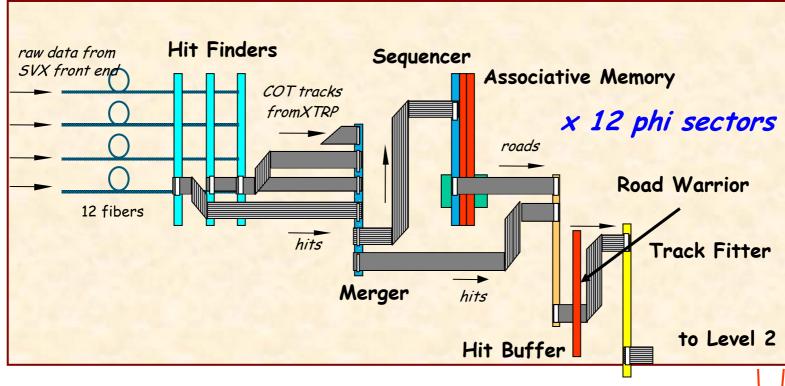

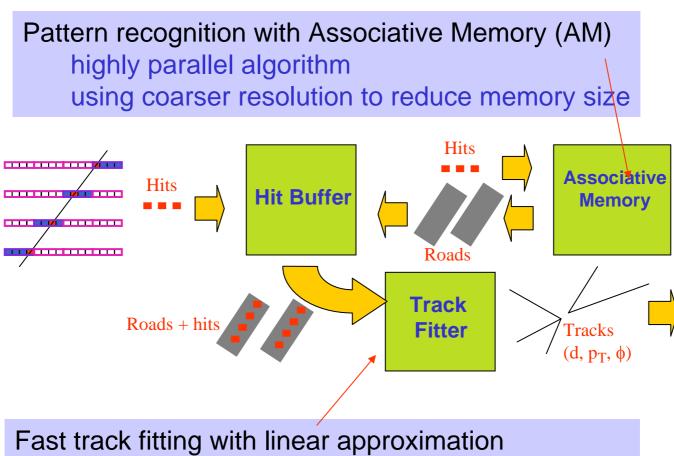

## Tracking in 2 steps

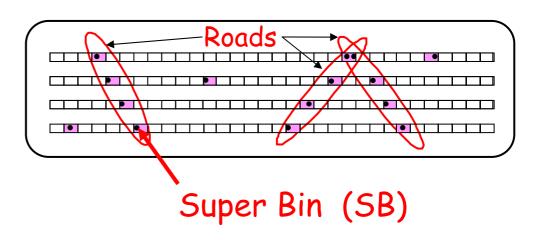

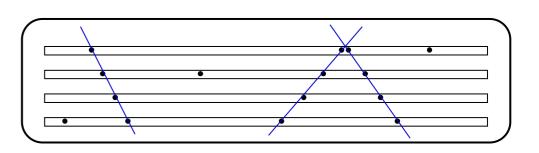

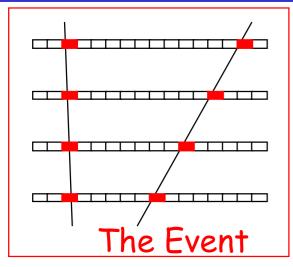

Find low resolution track candidates called "roads".

Solve most of the pattern recognition

2. Then fit tracks inside roads.

Thanks to 1st step it is much easier

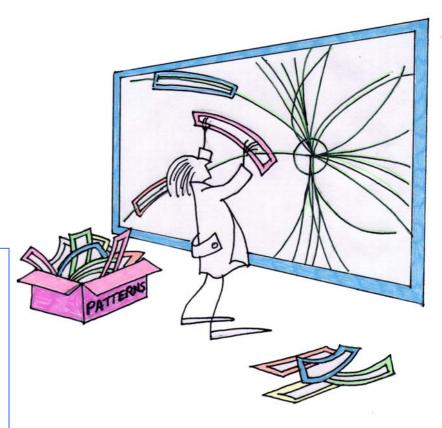

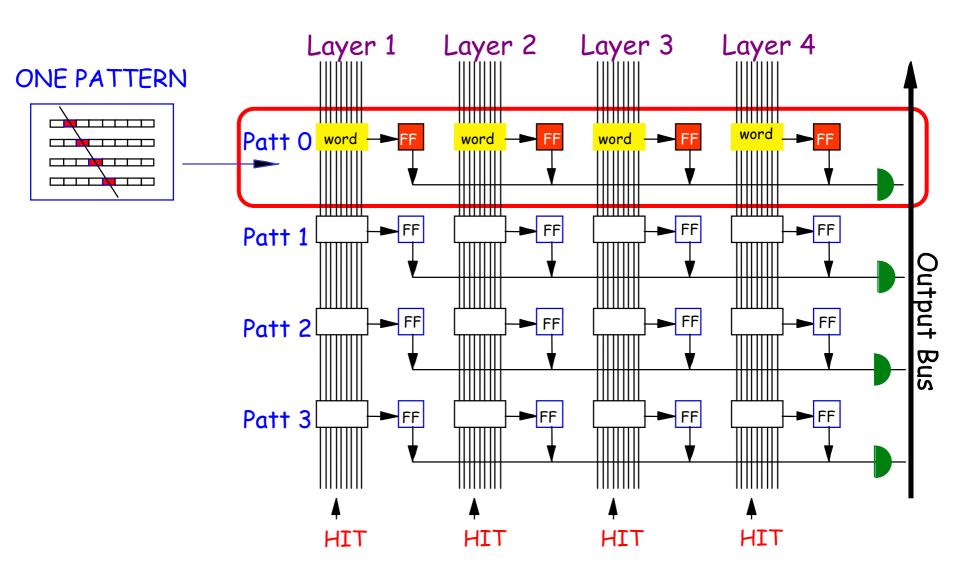

## Pattern matching

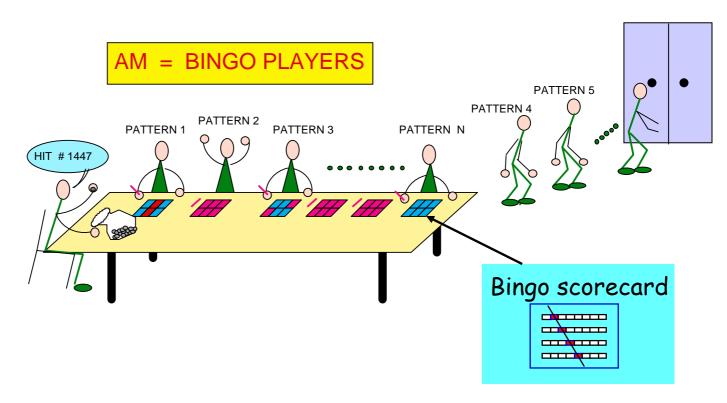

### **AM: Associative Memory**

- Dedicated device: maximum parallelism

- Each pattern with private comparator

- Track search during detector readout

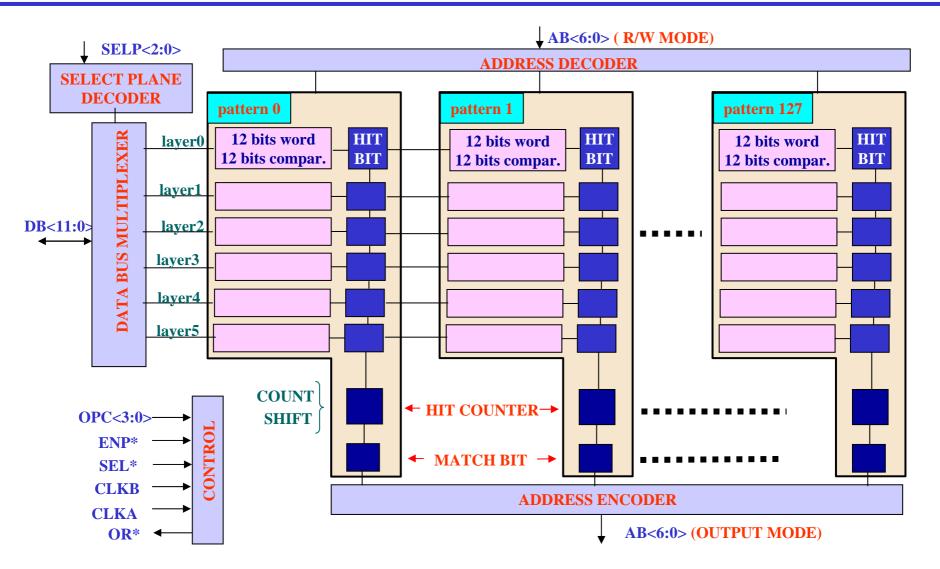

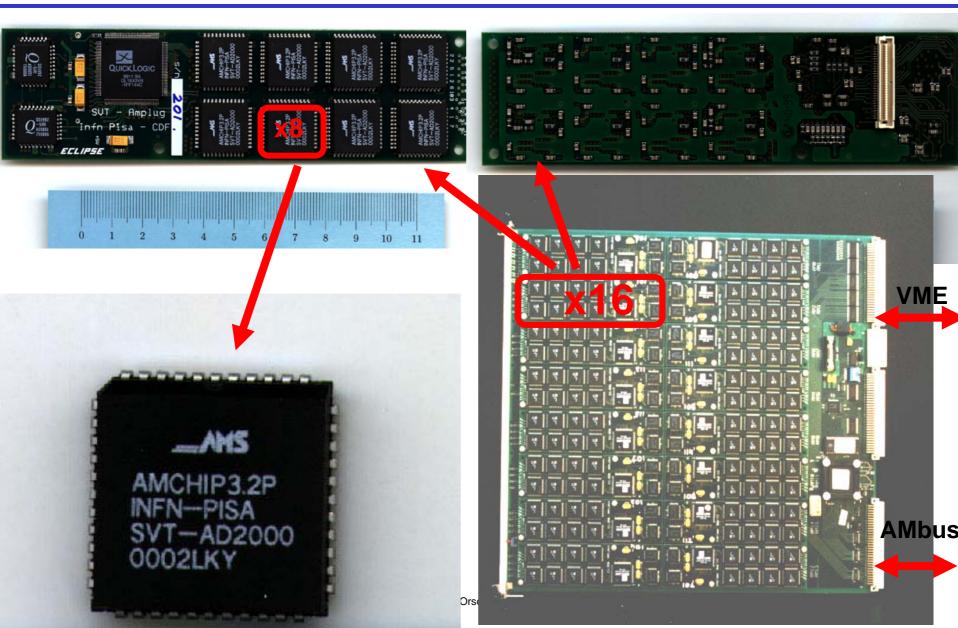

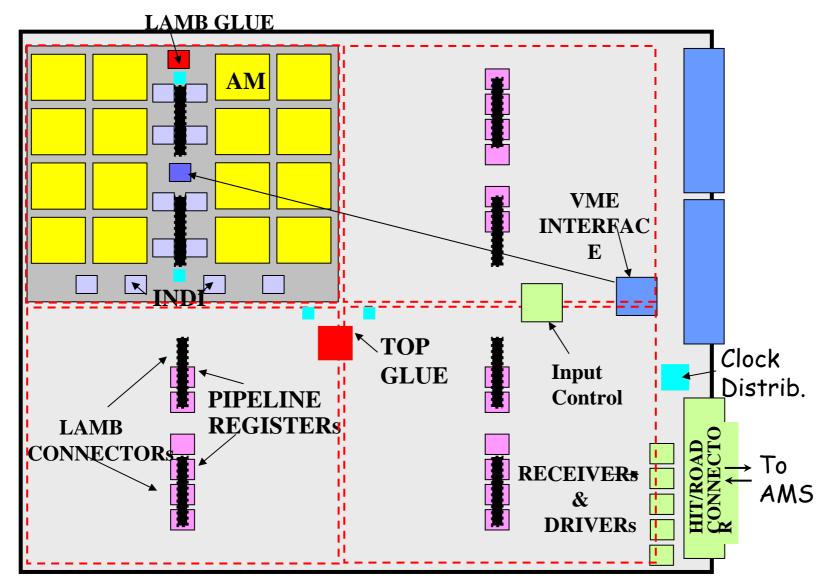

## AM chip & system

- Undoable with standard electronics (90's)

- ⇒ Full custom VLSI chip 0.7μm (INFN-Pisa)

- 128 patterns, 6x12bit words each

- Working up to 40 MHz

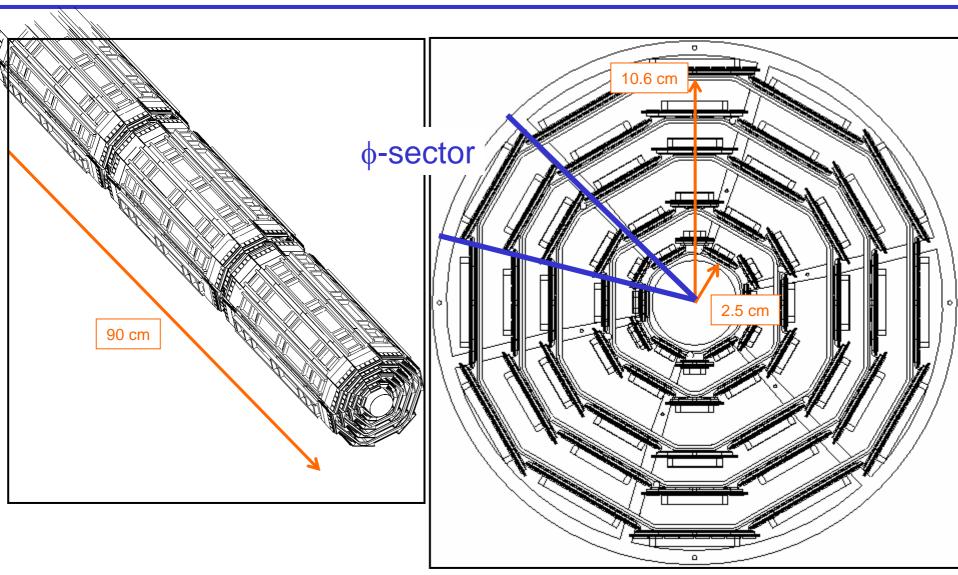

- Limit to 2-D

- 6 layers: 5 SVX + 1 COT

- ~250 micron bins  $\Rightarrow$  32k roads / 30°  $\phi$  sector

- >95% coverage for P<sub>t</sub> > 2 GeV

#### **AM** chip internal structure

## AM chip working principle

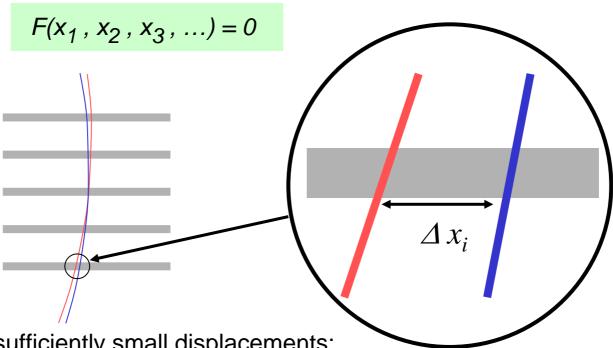

## **Track Fitting**

15

- Track confined to a road: fitting becomes easy

- Linear expansion in the hit positions x<sub>i</sub>:

- Chi2 = Sum<sub>k</sub> (  $(c_{ik} x_i)^2$ )

- $d = d_0 + a_i x_i$ ; phi = phi<sub>0</sub> + b<sub>i</sub> x<sub>i</sub>; Pt = ...

- Fit reduces to a few scalar products: fast evaluation

- (DSP, FPGA ...)

- Constants from detector geometry

- Calculate in advance

- Correction of mechanical alignments via linear algorithm

- fast and stable

- A tough problem made easy!

#### From non-linear to linear constraints

Non-linear geometrical constraint for a circle:

But for sufficiently small displacements:

$$F(x_1\,,\,x_2\,,\,x_3\,,\,\ldots)\sim a_0+\,a_1 \Delta x_1 + a_2 \Delta x_2 + a_3 \Delta x_3 + \ldots \,=0$$

with constant a;

(first order expansion of *F*)

#### **Constraint surface**

6 coordinates:  $x_1$ ,  $x_2$ ,  $x_3$ ,  $x_4$ ,  $x_5$  ( $P_T$ ),  $x_6$  ( $\phi$ )

3 parameters to fit:  $P_T$ ,  $\phi$ , d

3 constraints

#### tangent plane:

$$\sum_{1}^{6} a_i x_i = b$$

#### track parameters:

$$d\approx c_0+\sum_1^6 c_i\,x_i$$

хЗ 3 dimensional surface in 6 dimensional space

Linear approximation is so good that a single set of constants is sufficient for a whole detector wedge (  $30^{\circ}$  in  $\varphi$  )

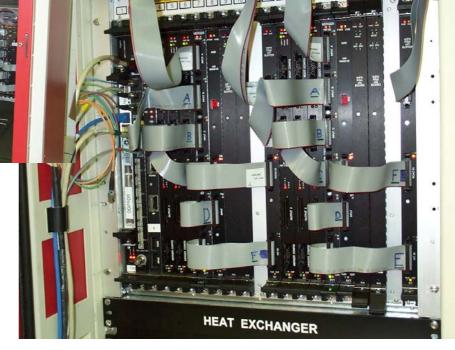

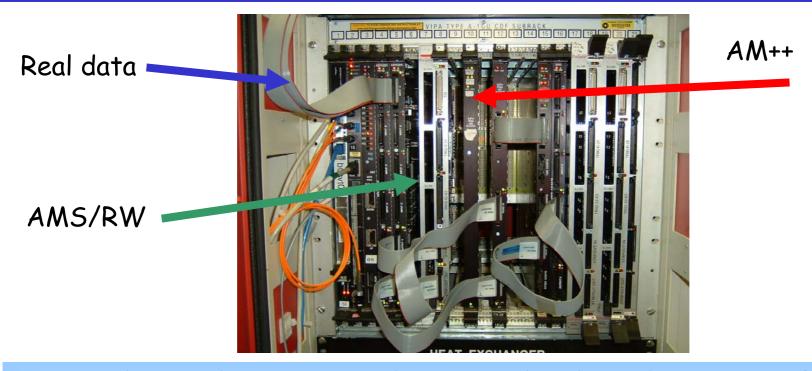

## SVT crates in CDF counting room

#### The Device

#### **AM Board**

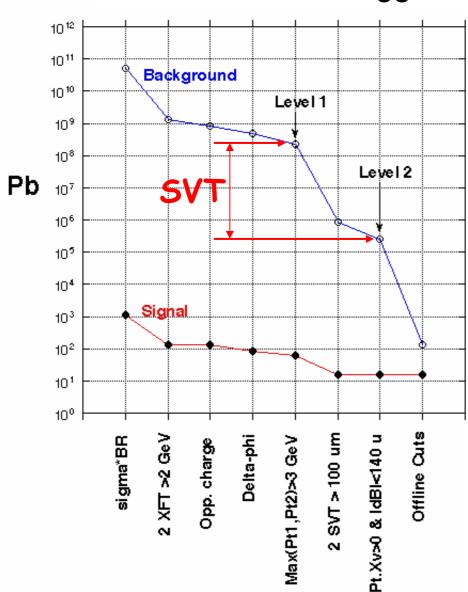

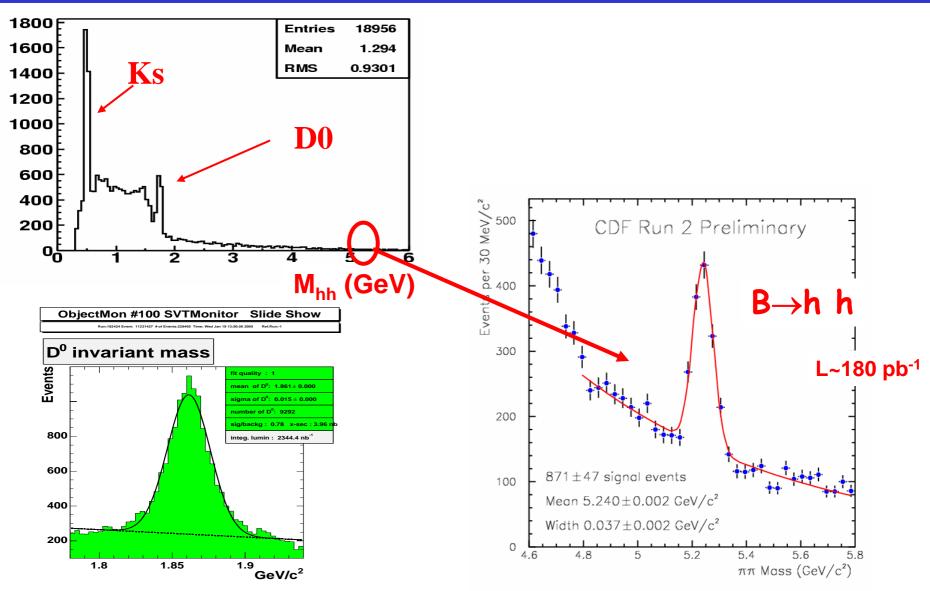

#### **Hadronic B decays with SVT**

#### @ 3 x 10<sup>31</sup> cm<sup>-2</sup> s<sup>-1</sup>

#### Two paths

- · L1:

- Two XFT tracks

- •P+ > 2 GeV; P+1 + P+2 > 5.5 GeV

- · L2:

- $\cdot d_0 > 100 \mu m$  for both tracks

- ·Validation of L1 cuts with ∆\$>20°

- ·Lxy > 200 μm

- •d<sub>0</sub>(B)<140 μm

Two body decays

#### · L1:

- Two XFT tracks

- •P+ > 2 GeV; P+1 + P+2 > 5.5 GeV

- · L2:

- $\cdot d_0 > 120 \mu m$  for both tracks

- ·Validation of L1 cuts with ∆\$>2°

- •Lxy > 200 μm

- d<sub>0</sub>(B) 140 um

Many body decays

#### $B^0 \rightarrow had + had Trigger$

# The SVT advantage: 3 orders of magnitude

0.00

0.05

Impact parameter (cm)

0.10

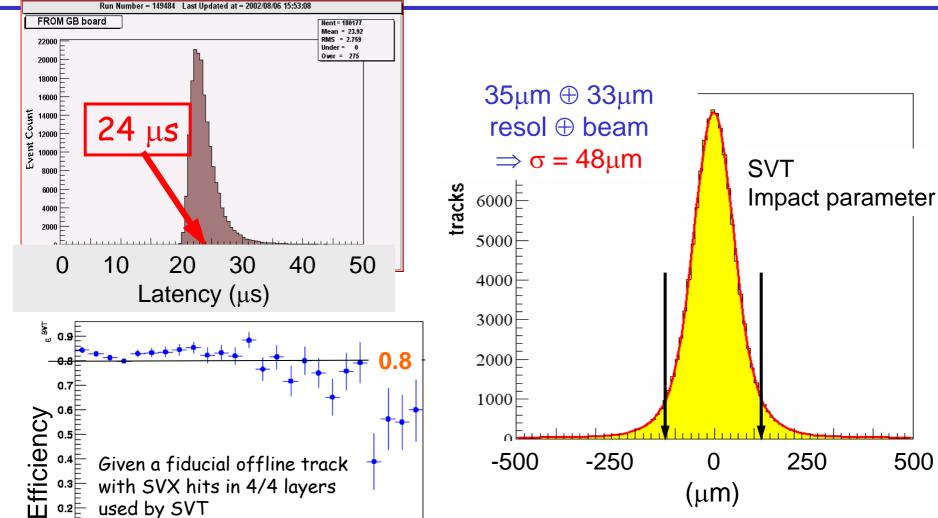

#### Performance @ 5x10<sup>31</sup>

0.15

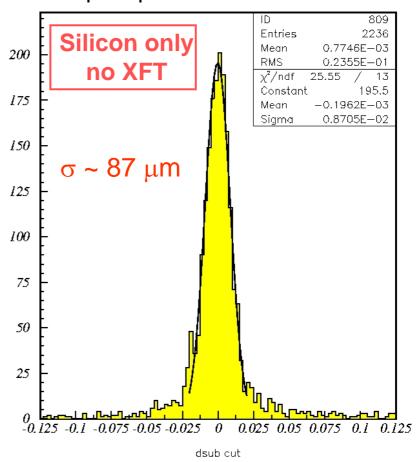

## **SVX** only

24

- Good tracks from just 4 closely spaced silicon layers

- I.p. as expected due to the lack of curvature information

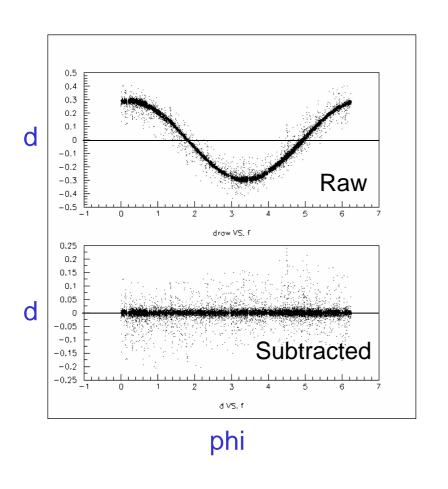

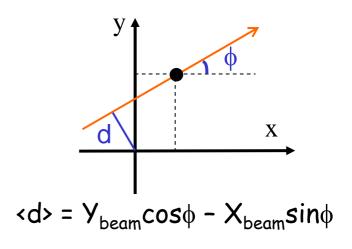

#### impact parameter distribution

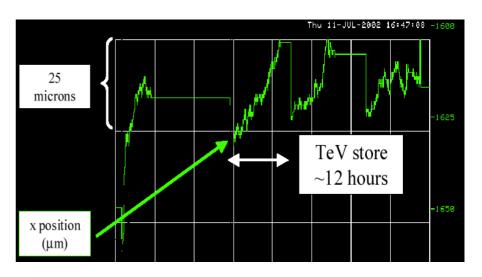

#### Online beamline fit & correction

#### **Hadron-hadron mass distribution**

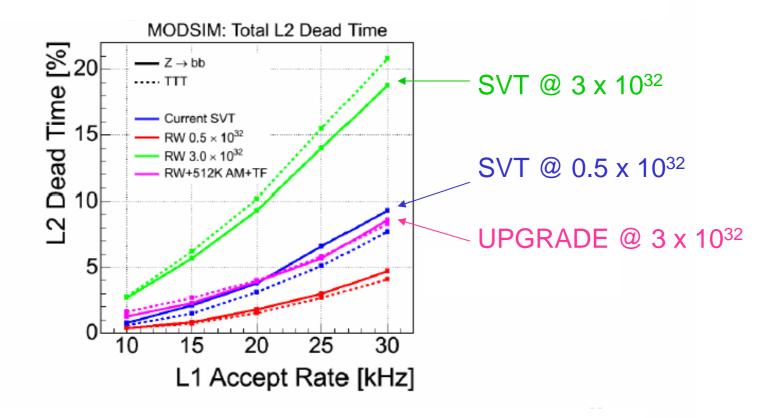

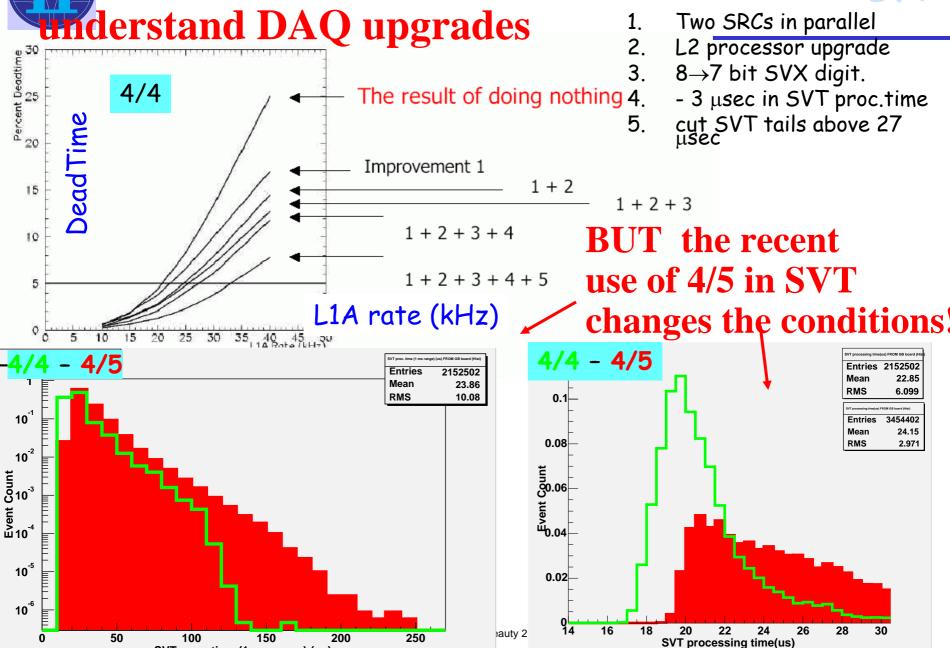

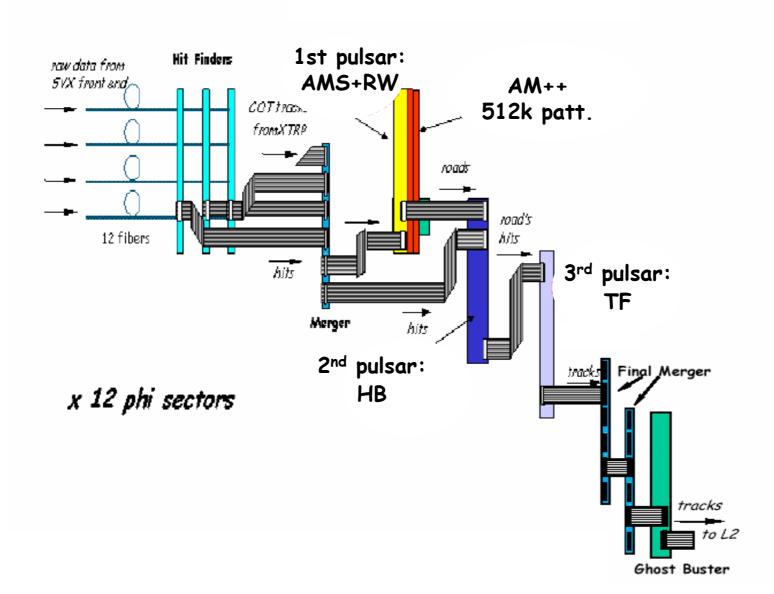

## **Upgrading SVT**

Reduce SVT processing time:  $c_1+c_2*N(Hit)+c_3*N(Comb.)$

- 1. More patterns  $\rightarrow$  thinner roads

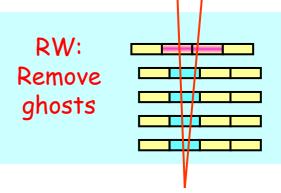

- 2. Move Road Warrior before the HB

- 3. New TF++, HB++, AMS++, AM++ @ > 40MHz

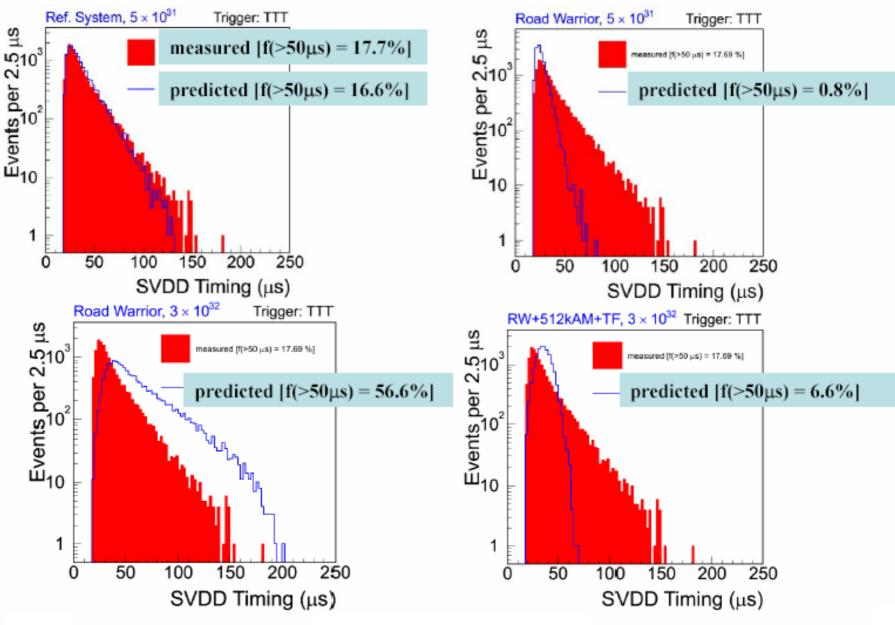

## **Dead Time vs. L1 Accept Rate**

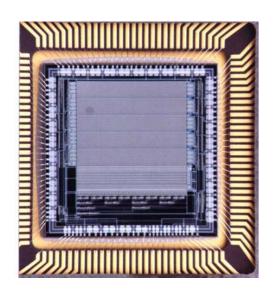

## New AM chip

Standard Cell UMC 0.18 μm

10x10 mm die - 5000 patterns

6 input hit buses

tested up to 40 MHz, simulated up to 50 MHz

- 116 prototype chips on September 2004

MPW run low yield 37%

- 3000 production chips on April 2005

good yield 70%

private masks → better process parameter tuning

for dense memory

## LAMB++

#### What next?

#### **SUMMARY**

- The design and construction of SVT was a significant step forward in the technology of fast track finding

- We use a massively parallel/pipelined architecture combined with some innovative techniques such as the associative memory and linearized track fitting

- Performance of SVT is as expected

- CDF is triggering on impact parameter and collecting data leading to significant physics results

- B-physics, and not only, at hadron colliders substantially benefits of on-line tracking with off-line quality

# **BACKUP SLIDES**

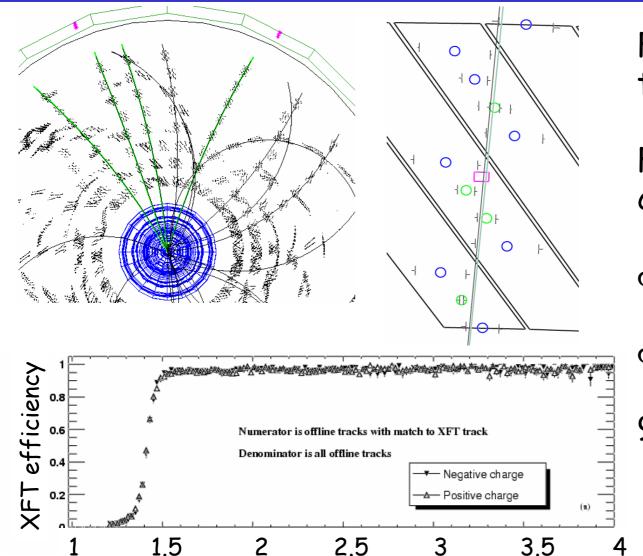

#### Level 1 drift chamber trigger (XFT)

Finds  $p_T$ >1.5 GeV tracks in 1.9  $\mu$ s

For every bunch crossing (132 ns)!

$\sigma(1/p_T) = 1.7\%/GeV$

$\sigma(\phi_0)$  = 5 mrad

96% efficiency

offline transverse momentum (GeV)

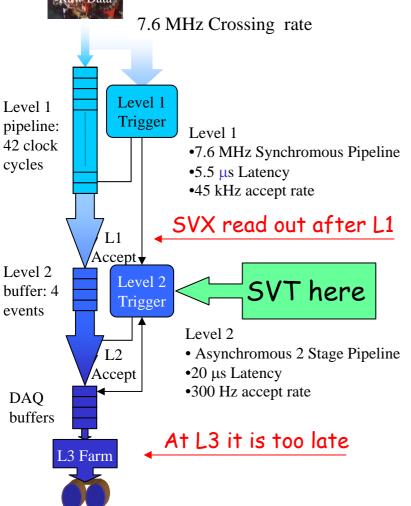

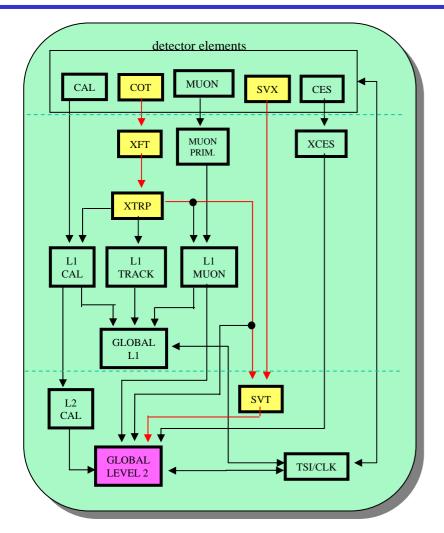

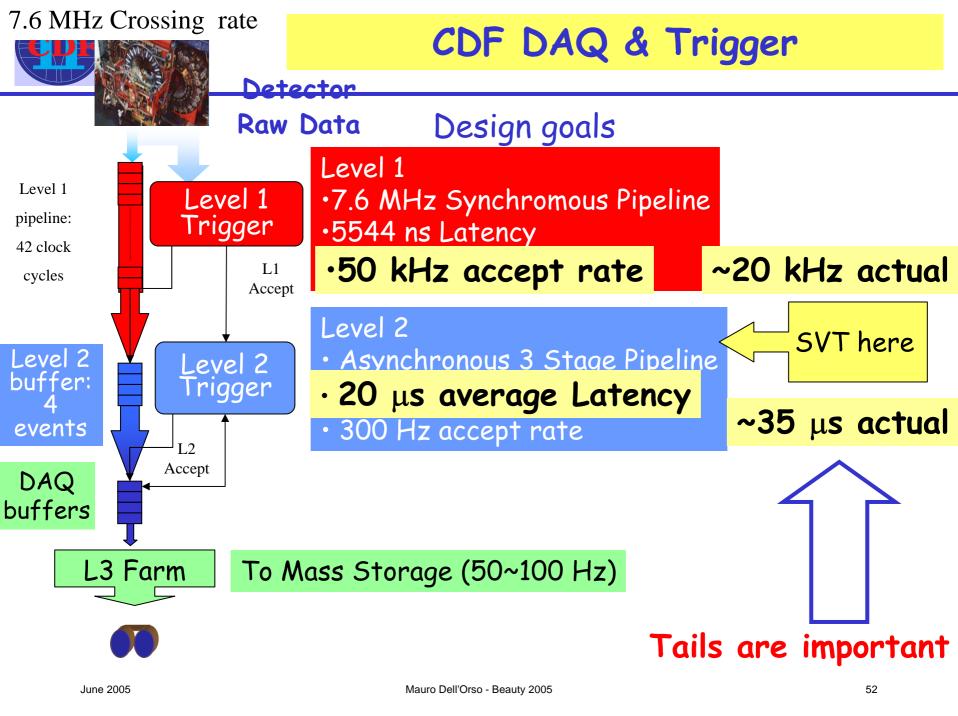

#### **CDF** Run II trigger architecture

- Tracking system

- central outer tracking (COT)

- silicon tracking (SVX II & ISL)

- three-level trigger

- L1: 5.5 μs pipeline

- XFT: L1 2D COT track

- L2: ~20 μs processing time

- two stages of 10 μs

- SVT at stage 1 of L2

- SVX II readout

- hit cluster finding

- pattern recognition

- track fitting

#### 2005 Trigger Performance & Limitations SVT

| Level | Input rate | Output<br>rate           | Potential limitations Current limitation               | Future upgrades                                   | 2006<br>Output<br>rate          |

|-------|------------|--------------------------|--------------------------------------------------------|---------------------------------------------------|---------------------------------|

| 1     | ~1MHz      | 25kHz<br>(spec<br>45kHz) | Silicon readout SVT processing time L2 processing time | •XFT upgrade •SVT upgrade •L2 Pulsar DONE         | 25kHz<br>(higher at<br>low lum) |

| 2     | 25kHz      | 400Hz<br>(spec<br>300Hz) | •Readout (non Si) •Event builder •L3 processing        | •TDC modification •Event builder •Faster L3 nodes | 1kHz                            |

| 3     | 380Hz      | 85Hz<br>(spec<br>75Hz)   | •CSL/data logging                                      | •Parallel logger 45 MB/s •CSL upgrade >60MB/s     | 100Hz                           |

Rates are "peak rates that we can achieve with good livetime."

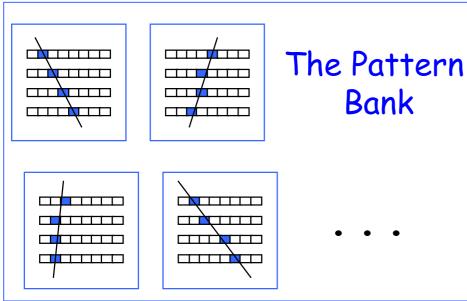

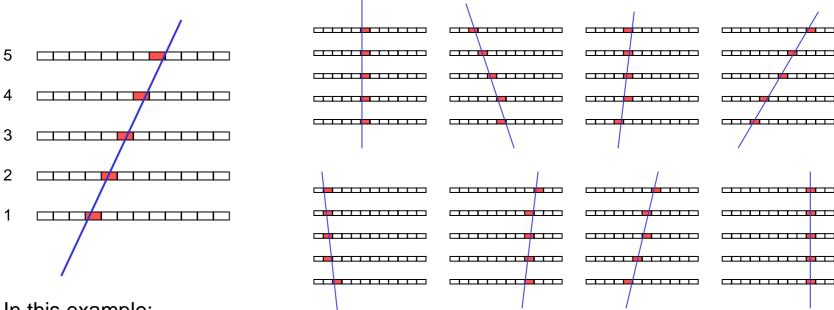

# **Building the "Pattern Bank"**

Instead of looking for hit combinations such that  $f(x_1,x_2,x_3,...) = 0$

- 1. Build a database with all patterns corresponding to "good" tracks

- 2. Compare hits in each event with all patterns to find track candidates

In this example:

Straight lines, 5 layers, 12 bins/layer

Total number of patterns  $\sim (12)^{2*}(5-1) = 576$

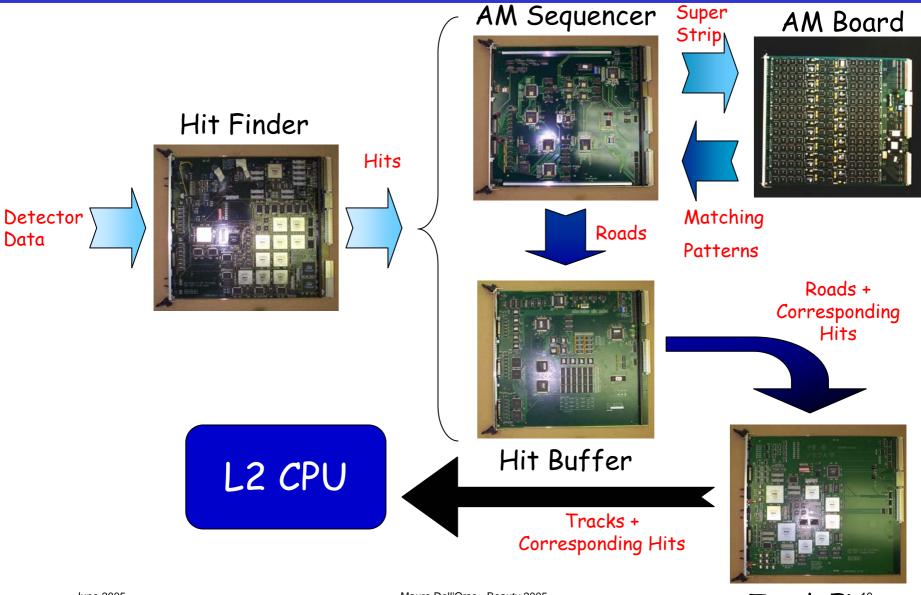

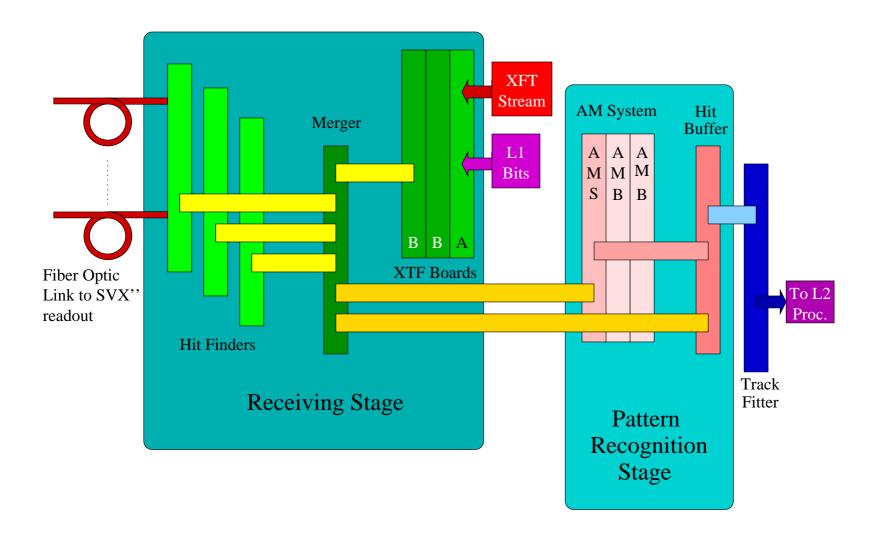

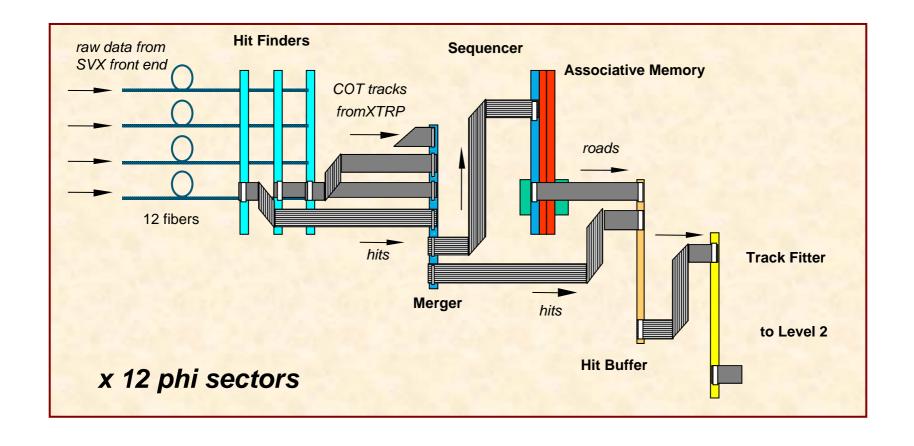

#### **SVT** basic architecture

Pattern recognition and track fitting done separately and pipelined

using full resolution of the silicon vertex detector

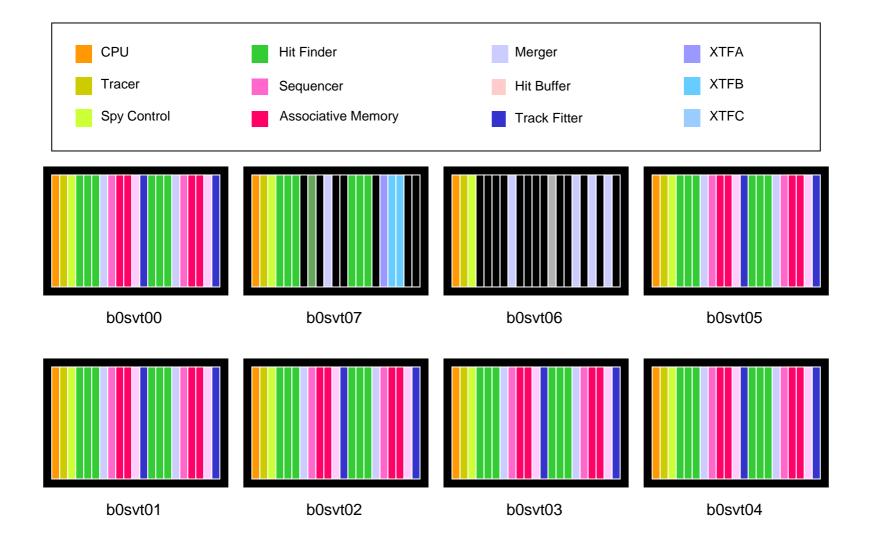

# **SVT Wedges**

# **An SVT Slice**

# **SVT** system architecture

# **SVT:** board count

| • | Hit Finders          | 42  |          |                       |

|---|----------------------|-----|----------|-----------------------|

| • | Mergers              | 16  |          |                       |

| • | Sequencers           | 12  |          | INFN                  |

| • | <b>AMboards</b>      | 24  |          |                       |

| • | Hit Buffers          | 12  |          | INFN & Geneva         |

| • | <b>Track Fitters</b> | 12  |          | University of Chicago |

| • | <b>Spy Controls</b>  | 8   |          |                       |

| • | XTFA                 | 1   |          |                       |

| • | XTFB                 | 2   |          |                       |

| • | XTFC                 | 6   |          |                       |

| • | Ghostbuster          | 1   | _        |                       |

|   | TOTAL                | 136 | + spares |                       |

# **SVT:** board and crate layout

## SVT data volume requires parallelism

Reduces gigabytes/second to megabytes/second

Peak (avg): 20 (0.5) 6B/s ---- 100 (1.5) MB/s

# **Expectations for runll**

#### Rates within bandwidth @ $0.7 \times 10^{32}$

- Level 1: 20 kHz (bw 50 kHz)

- Level 2: 39 Hz (bw 300 Hz)

- Level 3: negligible

#### Expected yields in run II (2 fb<sup>-1</sup>)

|                                          | <u> </u> |                                           |

|------------------------------------------|----------|-------------------------------------------|

| Mode                                     | Events   |                                           |

| $ m B_d  ightarrow \pi^+ \pi^-$          | 15,200   | angle γ at few degrees level              |

| $B_s \rightarrow D_s \pi$                | 10,600   |                                           |

| $B_{ m s}  ightarrow D_{ m s} \pi\pi\pi$ | 12,800   | $5\sigma$ sensitivity up to $x_s \sim 40$ |

| $B_s \rightarrow D_s^* \pi$              | 9,400    |                                           |

| $\mathbf{D}^*\pi$                        | 300,000  |                                           |

| $\mathbf{Z} \rightarrow \text{b-bbar}$   | 32,000   |                                           |

N.B.: yields without SVT  $\Rightarrow$  O(1) event!

# **Promise is promise**

What we promised.... From SVT TDR ('96) using offline silicon hits and offline CTC tracks

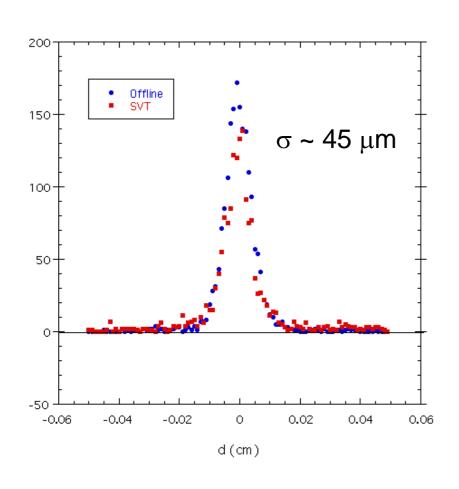

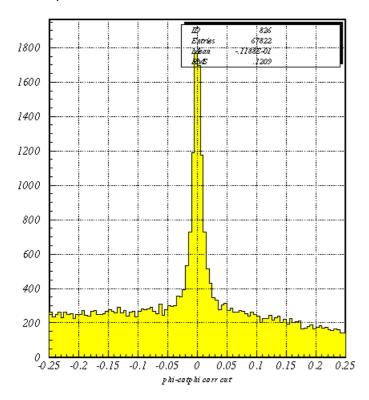

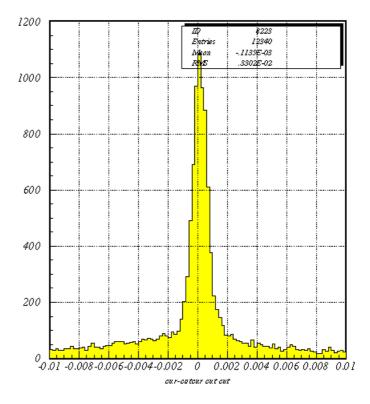

# **SVT performance**Not just impact parameter

#### Loop on all SVT-COT track pairs and compare parameters

φ: **SVT** - **COT**

#### Curvature: SVT - COT

#### Level 1 @Lum=40x10<sup>30</sup> cm<sup>-2</sup> sec<sup>-1</sup>

#### Two Major Components

Calorimeter Triggers: Jets, electrons, photons, etc. ~4-5 kHz

In SVT: L1\_JET10\_&\_ΣET90 (Higgs multijet)

L1\_TWO\_TRK2\_&\_TWO\_CJET5 (Z→bb)

~2 kHz L1\_MET15\_&\_TWO\_TRK2 (Higgs  $Z \rightarrow vv$ )

L1\_TWO\_TRK10\_DPHI20 (Di TAU exotic) L1 EM8 (Gamma + bjet) L1 CEM4 PT4 (B electron)

L1 CMUP6 PT4 (B muon)

Hadronic B Decays: Two XFT tracks

~11-12 kHz

- Using three classes of B triggers

- Scenario A

- p<sub>T</sub>>2, p<sub>T,1</sub>+p<sub>T,2</sub>>5.5, opp. charge, Δφ<135°; DPS</li>

- Scenario C

- $p_T>2.5$ ,  $p_{T,1}+p_{T,2}>6.5$ , opp. charge,  $\Delta \phi < 135^\circ$ ; PS by 2

- Low PT

- p<sub>T</sub>>2, Δφ<90°; Heavy DPS, saturate bandwidth</li>

- Not considered for long-term

# Physics Prospects: All-Hadronic B decay Trigger

#### **Impact parameter from the SVT**

**Trigger on secondary vertices (B hadrons)**

**Trigger Strategy**

$B_d^0 \rightarrow \pi\pi$  (CP Violation)

$B_s^0 \rightarrow D_s n\pi \quad (B_s mixing)$

$Z^0 \rightarrow b\bar{b}$  (b-jet calibration / top mass)

$H \rightarrow b\bar{b}$

#### **Level 1: 2D COT tracks (XFT)**

- Two stiff tracks  $(P_t > 2.0 \text{ GeV/c})$

- Remove back-to-back pairs (  $\delta \phi < 135$  )

- Opposite charge

#### Level 2: SVT tracks

- Two tracks with large impact parameter

- Vertex tracks require positive decay length

#### **Level 3:** full event reconstruction

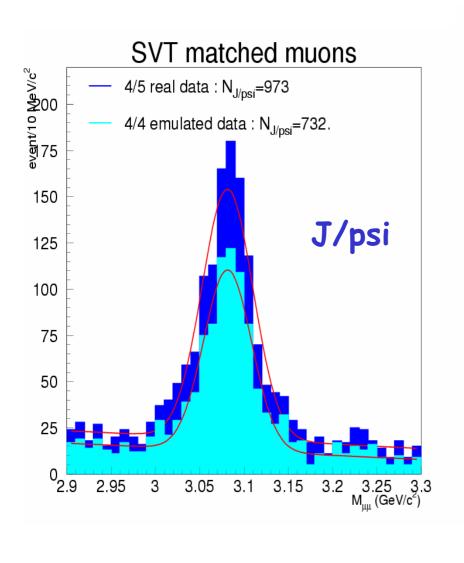

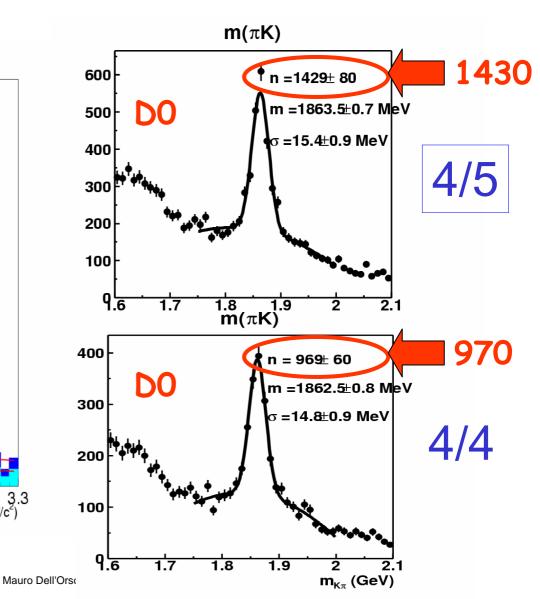

# WHY 4/5? Signal Yields with 4/5

# rate deadtime model (ModSim) to

SVT proc. time (1 ms range) (us)

# Extrapolate to high $\mathcal{L}$ with & without upgrades

# Upgrading SVT

# 512 Kpattern / phi sector

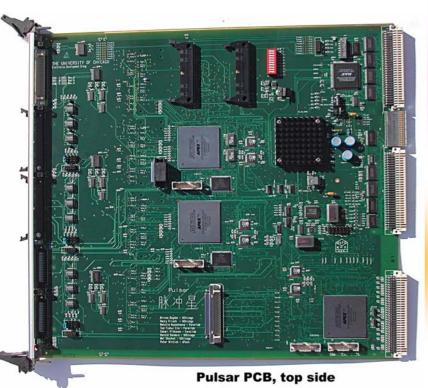

### Pulsar in SVT++

Large memory cannot be handled by old SVT boards.

The new ones are developed using Pulsar

- ·Fast enough to handle the new amount of data

- ·SVT interface built in

- Developers can concentrate on firmware (= board functionalities)

#### Sequencer + RW

RW remove redundant roads as soon as they are returned by AM sensitively reducing the amount of data handled by the Hit Buffer

#### Hit Buffer and Track Fitter

- They need to handle larger amount of roads and hits

- •Fully exploit the fast logic of the Pulsar

# Upgrade is on schedule

- ·AM++ and RW with 32k patterns have been already used in test runs for data tacking

- Plan to install AM++ with 32k pattern in July

- ·Studies of 128k patterns coverage and efficiency are underway

- ·Plan to install TF++ as soon as it will be ready (August) then move to 128k

- •HB++ expected to be installed during fall with 512k pattern memory

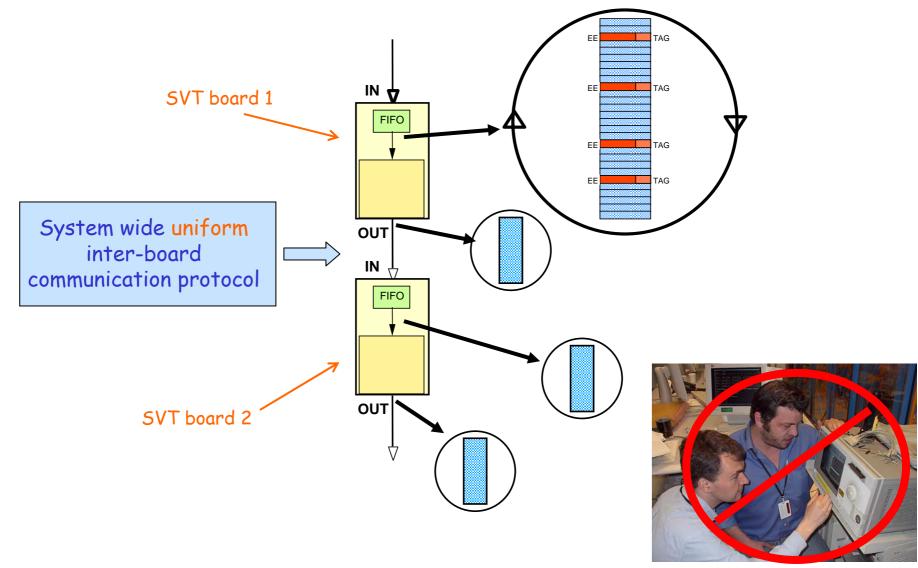

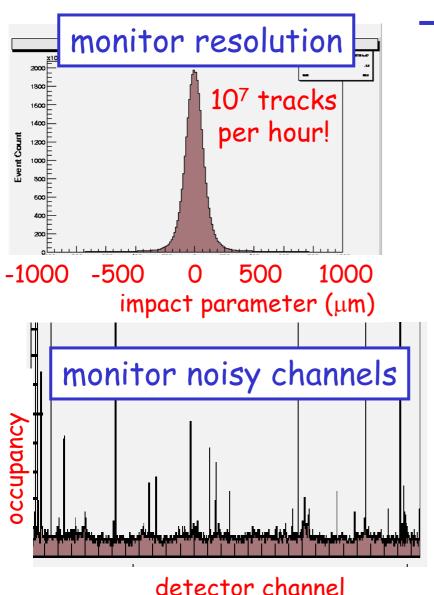

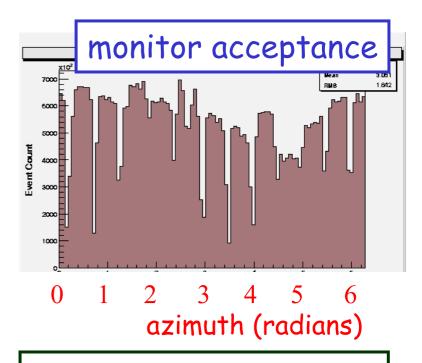

# Circular buffers monitor every data link: like a built-in logic analyzer

#### On-crate monitoring of circular buffers

Sample hits, roads, tracks at high rate

Check boards against emulation software

Fit for beam position ...

#### Performance:

- Paraliei/pipelined architecture

- Custom VLSI pattern recognition

- Linear track fit in fast FPGAs

- Reliability:

- Easy to sink/source test data (many boards can self-test)

- Modular design; universal, well-tested data link & fan-in/out

- Extensive on-crate monitoring during beam running

- Detailed CAD simulation before prototyping

- See poster by Mircea Bogdan

- Flexibility:

- System can operate with some (or all) inputs disabled

- Building-block design: can add/replace processing steps

- Modern FPGAs permit unforeseen algorithm changes

- Key: design system for easy testing/commissioning

### Doing silicon tracking quickly

- Three key features of SVT allow us to do in tens of microseconds what typically takes software hundreds of milliseconds:

- Parallel/pipelined architecture

- Custom VLSI pattern recognition

- Linear track fit in fast FPGAs

61