### Reconfigurable, High Density, Gigahertz Speed Low Power Radiation Hardened FPGA Technology

Rajit Manohar<sup>1</sup>, Clinton W. Kelly<sup>1</sup>, IV, John Lofton Holt<sup>1</sup>, Chris Liu<sup>1</sup>, Dan Elftmann<sup>1</sup> Leonard Rockett<sup>2</sup>, Dinu Patel<sup>2</sup>, Steven Danziger<sup>2</sup>, S. Ramaswamy<sup>2</sup> Ken Label<sup>3</sup>, Melanie Berg<sup>3</sup>

<sup>1</sup>Achronix Semiconductor Corporation, 95 Brown Road, Suite 120, Ithaca, NY, 14850, USA <sup>2</sup>BAE SYSTEMS, 9300 Wellington Road, Manassas, VA, 20110, USA <sup>3</sup>National Aeronautical and Space Agency (NASA/GSFC), Greenbelt, MD, 20771, USA

27-29 November 2007

# **BAE/Achronix RHFPGA Program**

- Background

- Introduction

- Achronix Company

- Achronix FPGA Overview

- BAE/Achronix Radiation Hardened Test Chip Data

- BAE/Achronix RHFPGA Program Overview

- Product Features

- Product Development Strategy

- Summary

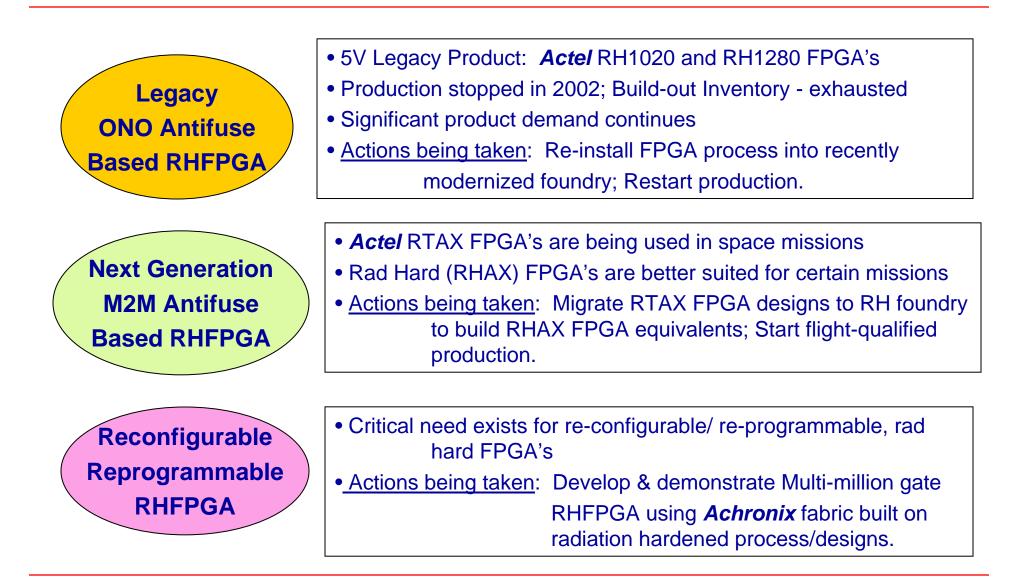

### **RHFPGA** Roadmap

- Program History

- Investigated Achronix Base Technology Starting in 2006

- Test chips fabricated & successfully tested for SEU in 2007

- BAE/Achronix Joint Development Program started under government funding in 2007

- Program Goal

- Develop a SRAM based Multimillion Gate Reconfigurable Radiation Hardened FPGA based on Achronix architecture using BAE's Radiation Hardened Process Technology

## Introduction

### **BAE SYSTEMS**

Achronix Company Overview

- Well funded, privately held fabless semiconductor company

- Founded in New York in 2004

- Headquarters moved to San Jose in 2006, retained New York

R&D lab

- Working 90nm and 180nm prototype silicon

- Series of Patents protect key IP

- Partnerships with Major Fabs, IP and EDA vendors

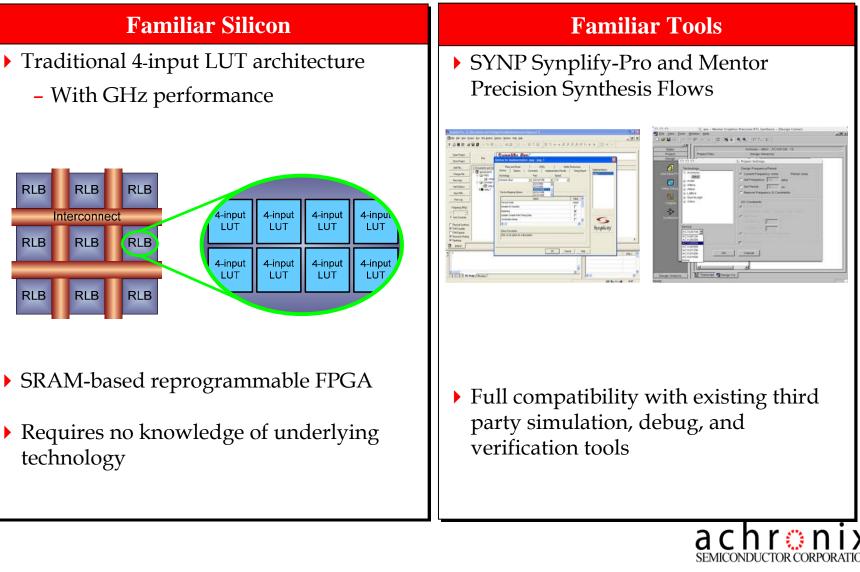

# Achronix Commercial FPGAs

- Standard SRAM-based FPGA fabric

- Embedded multipliers and memory blocks

- Pipelined implementation for high frequency operation ( > 1 GHz)

- Pipelining is transparent to designers

- Designers write standard VHDL/Verilog

- Industry-standard I/Os

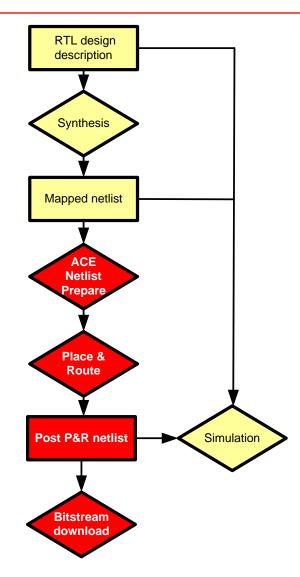

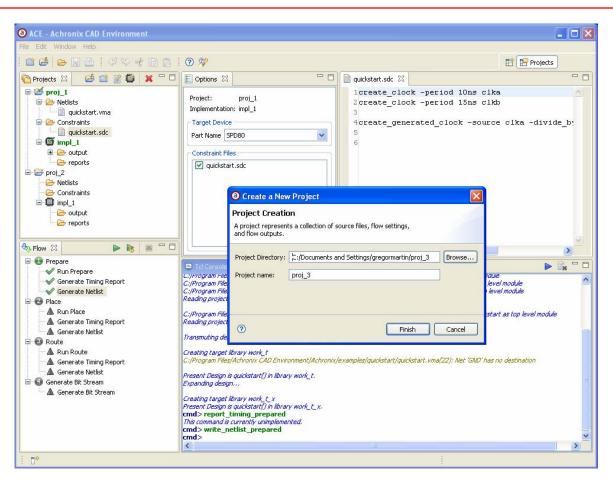

# **Achronix FPGA Architecture**

### **Familiar Silicon & Familiar Tools**

### **Achronix CAD Environment (ACE)**

# **Achronix FPGA History**

- 180 nm prototype (Sep 2005)

- <u>674 MHz</u>

- -World's fastest CMOS FPGA by 2x

- 90 nm prototype (Apr 2006)

- -<u>1.93 GHz</u>

- -World's fastest CMOS FPGA by 5x

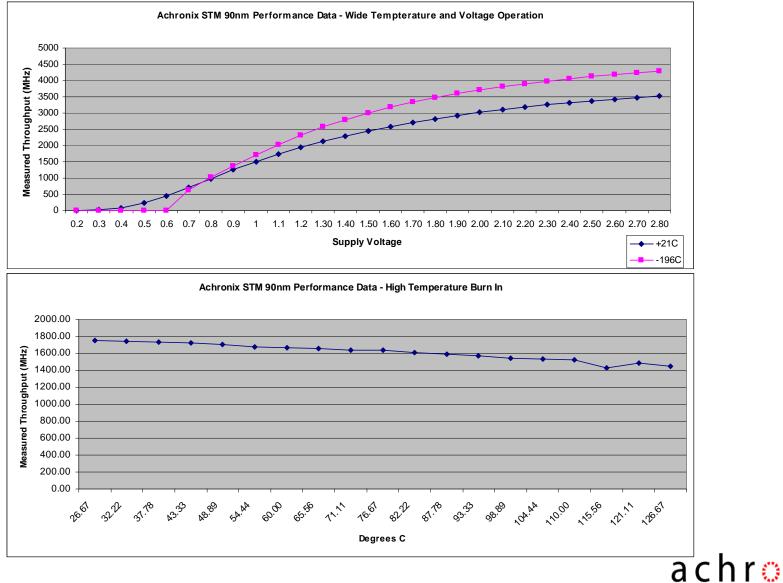

### Achronix 90nm FPGA Summary **BAE SYSTEMS**

SEMICONDUCTOR CORPORATION

# **SEU Mitigation**

### **BAE SYSTEMS**

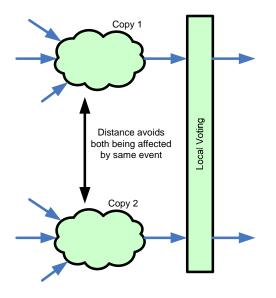

### Achronix patented Redundancy Voting Circuits (RVC) SEU mitigation

- Redundancy Voting Circuits (RVC)

- Two copies of all circuits implemented

- Copies are non-adjacent avoiding the risk of a single upset affecting both

- Every stage (combinatorial and state) has local voting mechanism

- Local voting waits until both copies agree

- no SEU, no delay

- If SEU on either, circuit resolves to the correct value after event energy dissipates

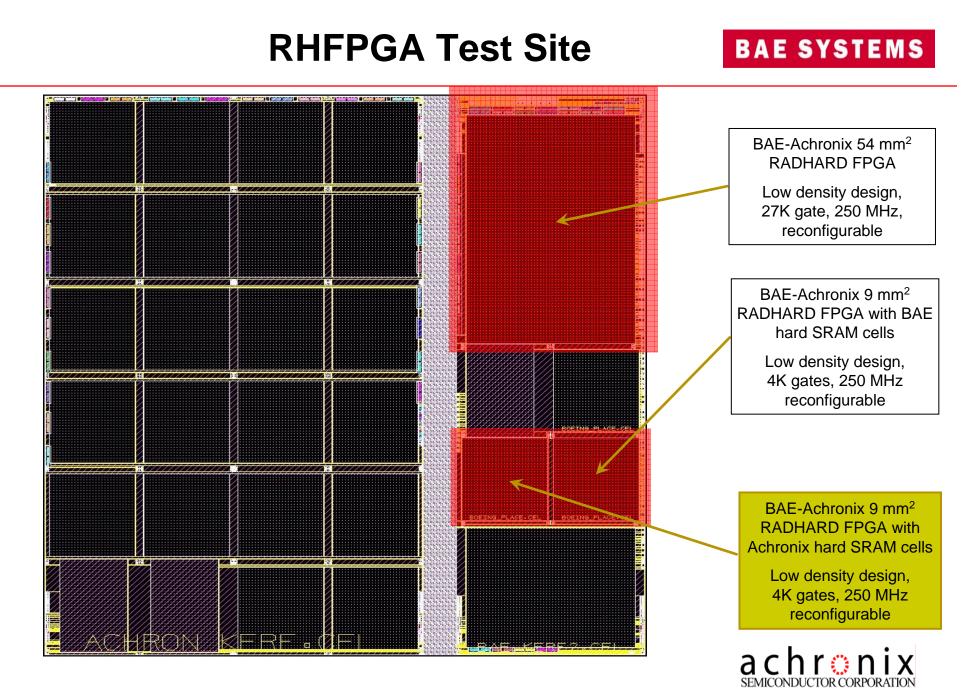

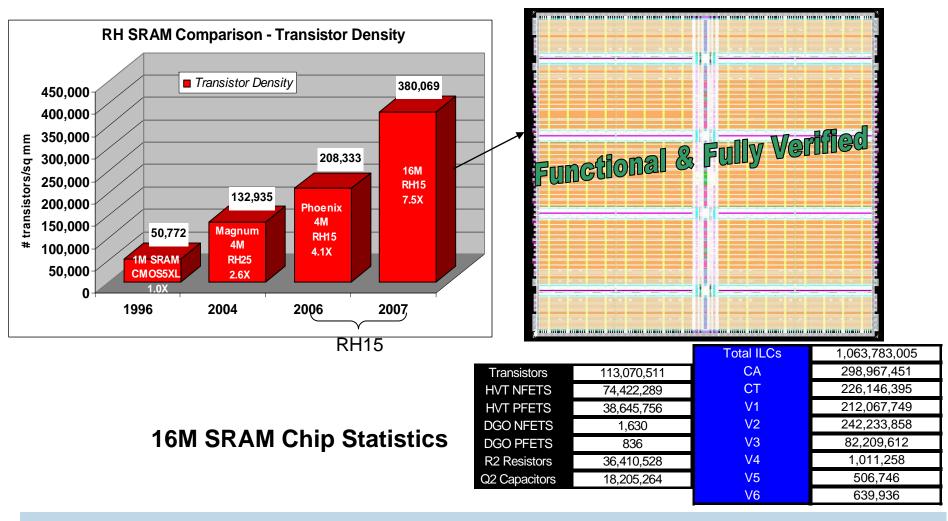

### **BAE/Achronix RHFPGA Test Chip**

# BAE-Achronix 3x3 RADHARD Testsite BAE SYSTEMS

# BAE RADHARD FPGA Test Site Result

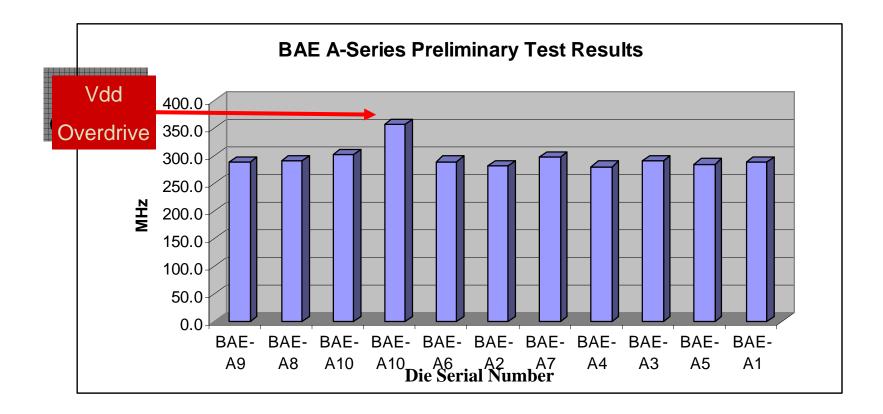

Design SPICE results predicted 275 MHZ – We averaged 289.3 MHz

# Test Site Performance and Power Summary

### **Radiation Test Overview**

- The Test Chip contained a 4x4 array of FPGA Tiles implemented with RVC

- One dedicated tile had an 8 bit counter (implemented in RVC) on output acknowledge to observe the functioning of the various FPGA configurations at a reasonable frequency with standard I/O

- Five different FPGA patterns were utilized during testing running at different frequencies (37 MHz to 290MHz)

- Testing completed at Texas A&M Cyclotron with Argon (0°), Krypton(0° and 45°), and Xenon (45°) did not cause any of the 5 patterns to lock-up or fail

- No observed SET or SEU events in SEE testing up to an effective LET threshold of 58 MeV-cm<sup>2</sup>/mg

- This testing validates that the Achronix Redundancy Voting Circuits (RVC) are achieving the intended goals

### **BAE/Achronix RHFPGA Product**

### **RHFPGA Product Approach**

#### **BAE SYSTEMS**

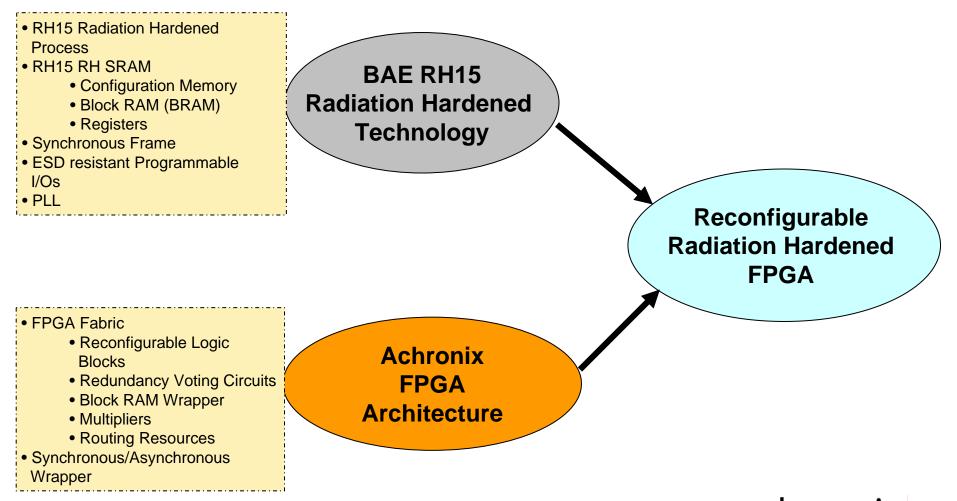

### **RH15 Density Capabilities**

> 113 Million Transistors; > 1 Billion Inter-Level Connects; 176 meters of Resistor 16M SRAM is the highest density part built in Manassas

### **RH15 Performance Capabilities**

### **RHFPGA Features**

- Reconfigurable Radiation Hardened FPGA for military, aerospace and industrial applications

- Leverages standard RTL: Eliminates need for TMR design & tools

- ▶ High Performance FPGA (Up to 350 MHz)

- Total Dose Hardness through 1x10<sup>6</sup> rad(Si)

- Single Event Error Rate of < 1x10<sup>-11</sup> upsets/bit day

- Operating Temperature

- -55°C to 125°C (Ambient)

- Extendable to Extreme Temperatures

- Independently Configurable IO (PCI Compatible)

- Low Voltage TTL/CMOS

- LVDS

- SSTL, HSTL

- Existing FPGA EDA Tool Support (Synplicity & Mentor)

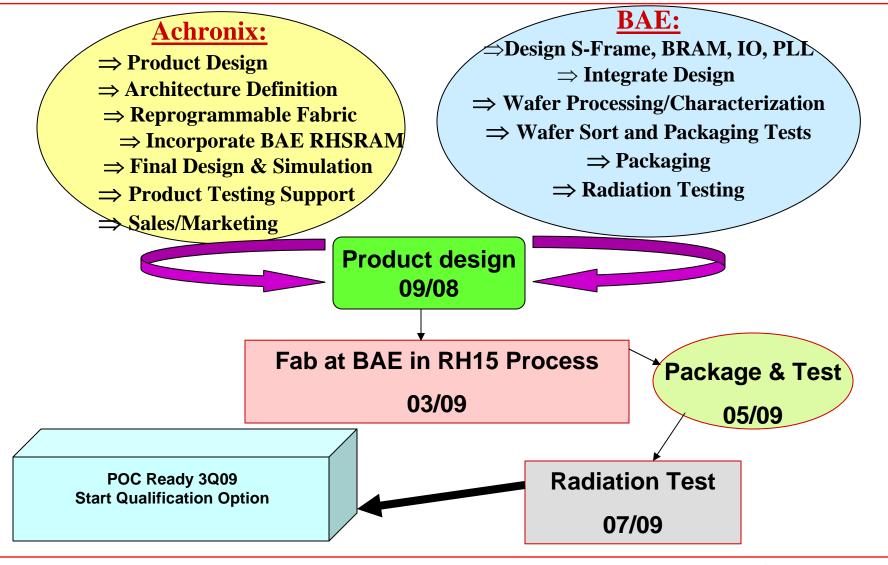

### **RHFPGA Product Development Strategy BAE SYSTEMS**

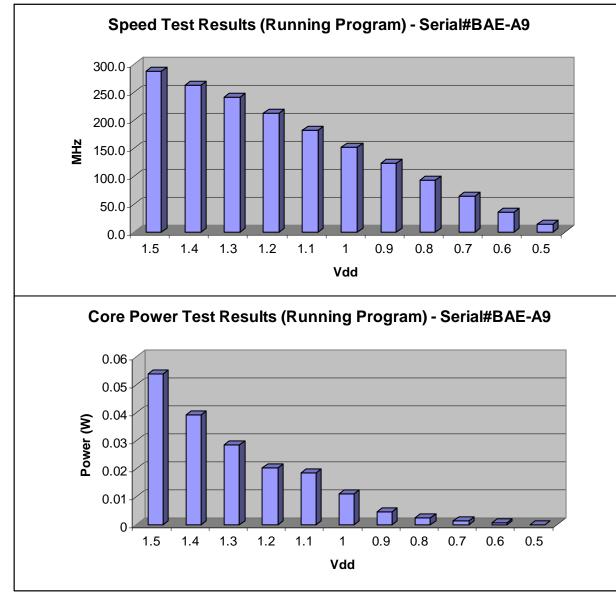

- Implement design using BAE Systems Radiation Hardened Process Technology Features

- On-chip memory structures

- Replace Standard SRAM with BAE Systems RADHARD SRAM

- Circuit methodology

- Use Achronix Redundancy Voting Circuit (RVC) and self-correction capability to actively correct upsets and transients

- Space apart critical nodes to reduce double-error probability

# ACX RHFPGA Program Overview

# RH15 CMOS Technology Features BAE SYSTEMS

| Key Features                        |                       |  |  |  |

|-------------------------------------|-----------------------|--|--|--|

| Features:                           | RH15                  |  |  |  |

| Isolation                           | STI                   |  |  |  |

| Thin Oxide / DGO Devices            | 26 Å / 70 Å           |  |  |  |

| Vdd Options                         | 1.5 V / 1.8 V / 3.3 V |  |  |  |

| Metal Levels                        | 7                     |  |  |  |

| Capacitors                          | Yes                   |  |  |  |

| Resistors                           | Yes                   |  |  |  |

| C4 / Wirebond                       | Y/Y                   |  |  |  |

| Radiation Hardness Assurance Levels |                       |  |  |  |

| Environment                         |                       |  |  |  |

| Total Dose (rad(Si))                | 1M                    |  |  |  |

| SEU (errors/bit-day)                | 1E-11                 |  |  |  |

| SEL (MeV-cm2/mg)                    | 120                   |  |  |  |

| Neutron Fluence (n/cm2)             | 1E13                  |  |  |  |

| Prompt Dose Upset (rad(Si)/s)       | 1E9                   |  |  |  |

| Prompt Dose Survival (rad(Si)/s)    | 1E12                  |  |  |  |

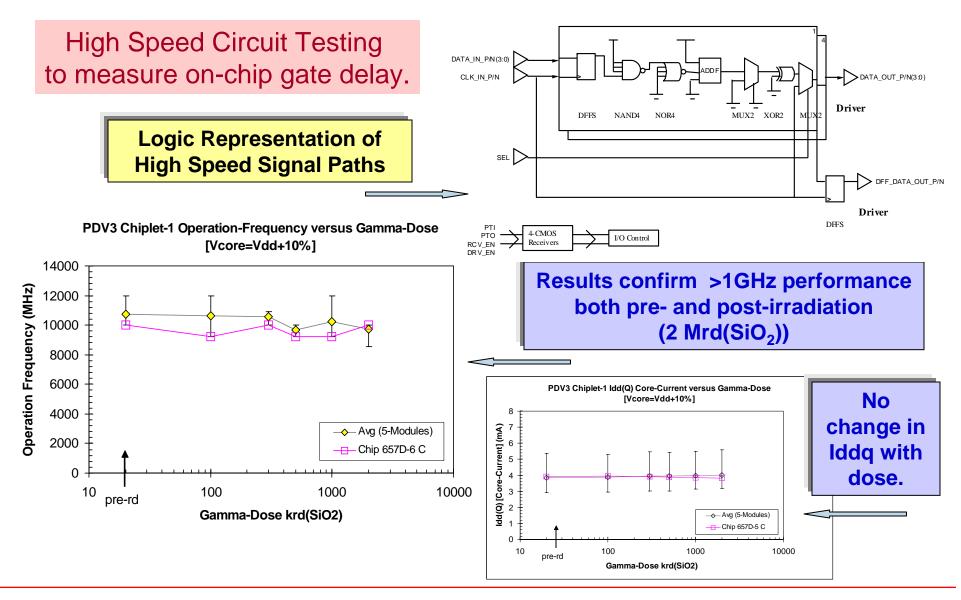

### **RH15 Performance Parameters Test Results BAE SYSTEMS**

| Parameter                                        | Goal                 | Threshold            | Test Results                    | Status   | Comments                  |  |

|--------------------------------------------------|----------------------|----------------------|---------------------------------|----------|---------------------------|--|

| Operating Voltage                                | 1.5, 1.8 and<br>2.5V | 1.5, 1.8 and<br>2.5V | 1.5, 1.8 and 2.5V               | Complete | Goal level achieved.      |  |

| Operating Temp                                   |                      |                      |                                 |          |                           |  |

| Full Performance                                 | 0 - 80C              | 0 - 80C              | 0 - 80C                         | Complete |                           |  |

| Functionality                                    | -55 - 125C           | -55 - 125C           | -55 - 125C                      | Complete | Goal level achieved.      |  |

| Operating Speed<br>Worst Case and Post Radiation | 1GHz                 | 500Mhz               | > 3GHz                          | Complete | Goal level achieved.      |  |

| Total Ionizing Dose (rd(Si))                     | = 1M                 | = 500K               | > 2M                            | Complete | Goal level achieved.      |  |

| Single Event                                     |                      |                      |                                 |          |                           |  |

| • Upset (errors/bit-day)                         | <1E-11               | <1E-10               | 3.4E-11 S-ASIC,<br><<1E-12 SRAM | Complete | Goal level achieved.      |  |

| • Latchup (MeV-cm2/mg)                           | >120                 | >100                 | >127                            | Complete | Goal level achieved.      |  |

| Neutron Radiation (n/cm2)                        | >1E13                | >1E12                | >1E13                           | Complete | Goal level achieved.      |  |

| Dose Rate (rd(Si)/s)                             |                      |                      |                                 |          |                           |  |

| • Upset                                          | >1E10                | >1E9                 | 2.2E9                           | Complete | Threshold level achieved. |  |

| • Survivability                                  | 1E12                 | 1E12                 | 1E12                            | Complete | Goal level achieved.      |  |

#### **RH15 KPP testing and verification successfully completed**

achronix SEMICONDUCTOR CORPORATION

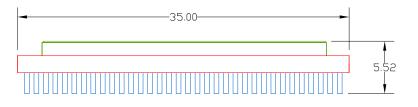

# **RHFPGA Package**

- Ceramic Column Grid Array

- Flip Chip Ceramic Column Grid Substrate (CCGA)

- Hermetic Seam Weld Sealing

- Substrate: 35 x 35mm

- 34 x 34 Column Array

- 1.0mm pitch

- 1144 Total I/O

- 840 signal

- 304 Vdd and Gnd

- Die site accommodates up to 20 mm Die

#### **RHFPGA Package Plans:**

- Package Modeling 10/08 12/08

- Update Substrate Design & Verification 12/08 2/09

- Package Availability 4/09

#### Package to be Modified to Accommodate Programmable I/O Features

# Summary

### **BAE SYSTEMS**

#### Test Site

- Electrical performance matches simulation (289 MHz)

- Preliminary SEU Radiation testing performed by NASA

- > Data shows no SEU observed up to LET of 58 at 0° & 45° angles of incidence

- RHFPGA Program

- Technical Goals of the Program Established

- > Build a multimillion reconfigurable RHFPGA using:

- Achronix patented architecture

- BAE's RADHARD process technology

- Preliminary Product Requirements defined

- Program Plan in place

- Design Activity underway

- Defined Design Approach Methodology

- > Defined Specification details for BRAM, S-Frame, I/O, PLL.