## Chamber electronics Status, Plans, Needs

Sten Hansen and <u>Wu, Jinyuan</u> Fermilab, PPD/EED Dec. 2006

#### High-Speed Differential Interfaces

"Cyclone II devices can transmit and receive data through LVDS signals at a data rate of up to 640 Mbps and 805 Mbps, respectively. For the LVDS transmitter and receiver, the Cyclone II device's input and output pins support serialization and deserialization through internal logic."

#### ~6000 Channels

#### ~7000 Channels

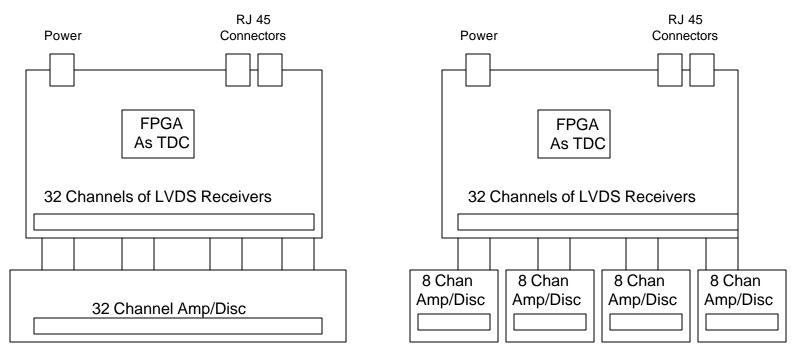

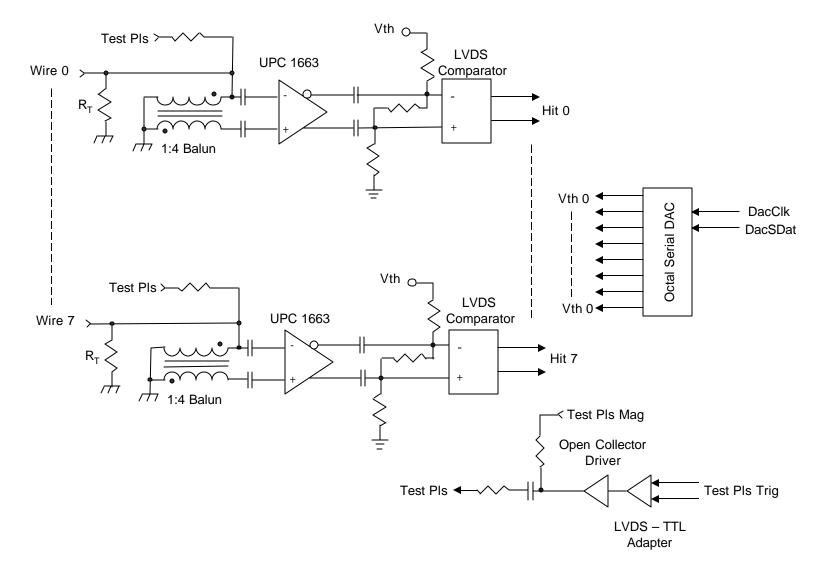

#### 8 Channel Amp/Disc - One per 8 channel Card, Four per 32 channel Card

#### **TDC Card Arrangement**

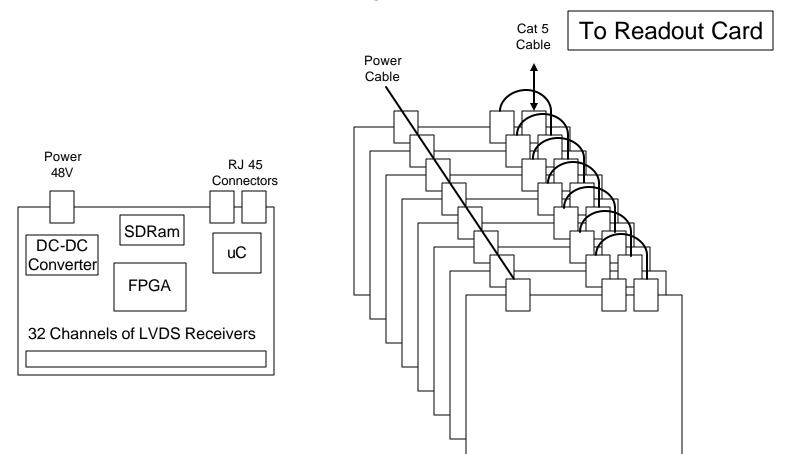

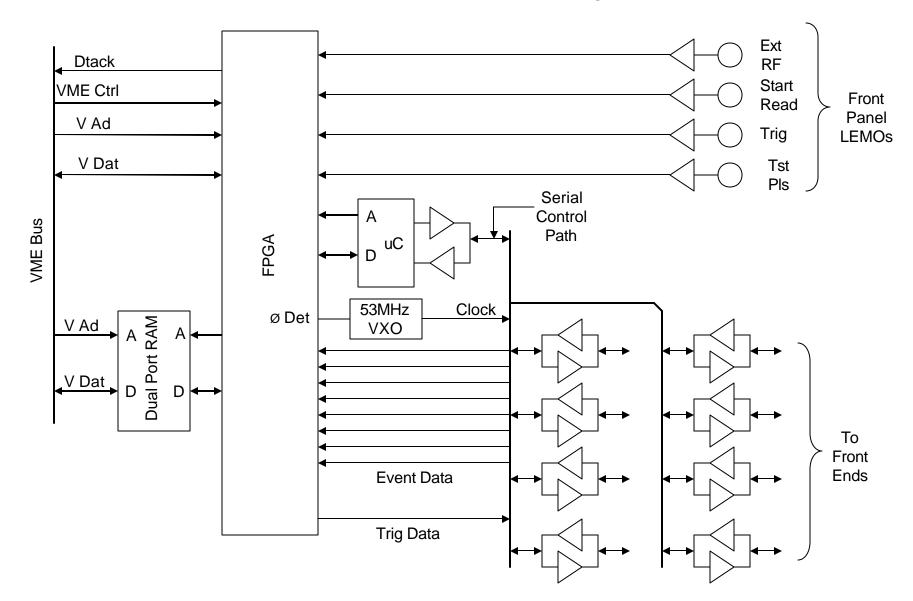

907 TPC/TDC Readout Card Block Diagram

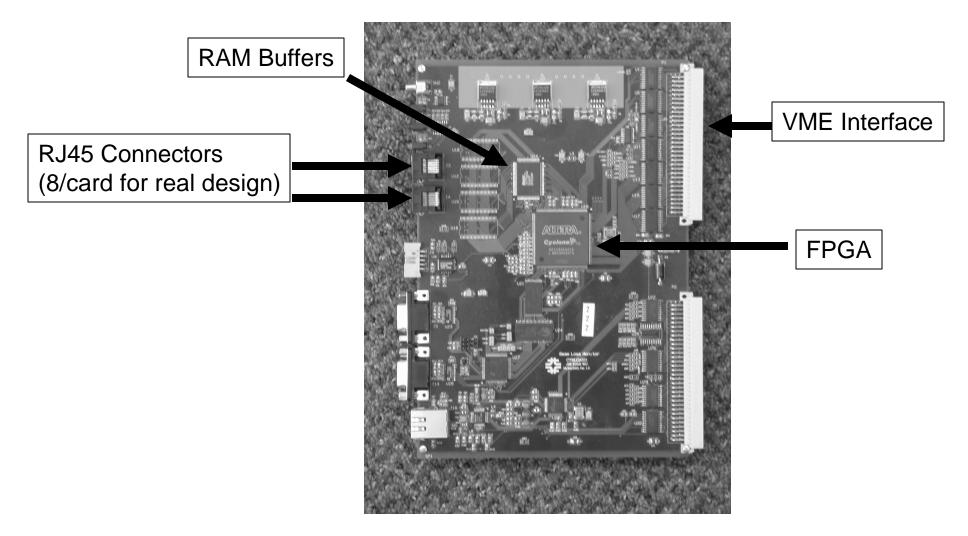

## **Appearance of Readout Card**

Shown here is Fermilab Beam Loss Monitor (BLM) Control Card

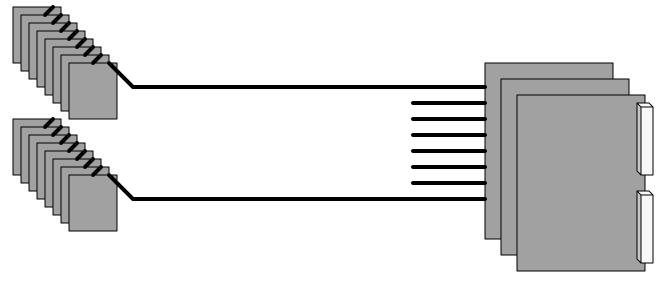

## **TDC-Readout System**

**TDC Cards**

**Readout Cards**

### TDC Using FPGA (LSB 1ns+-)

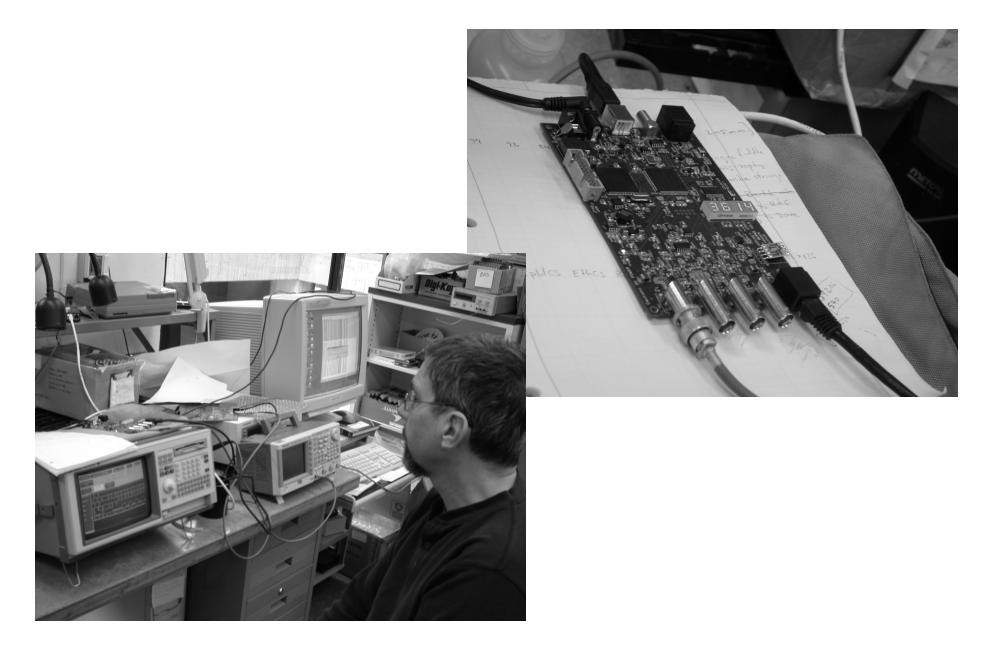

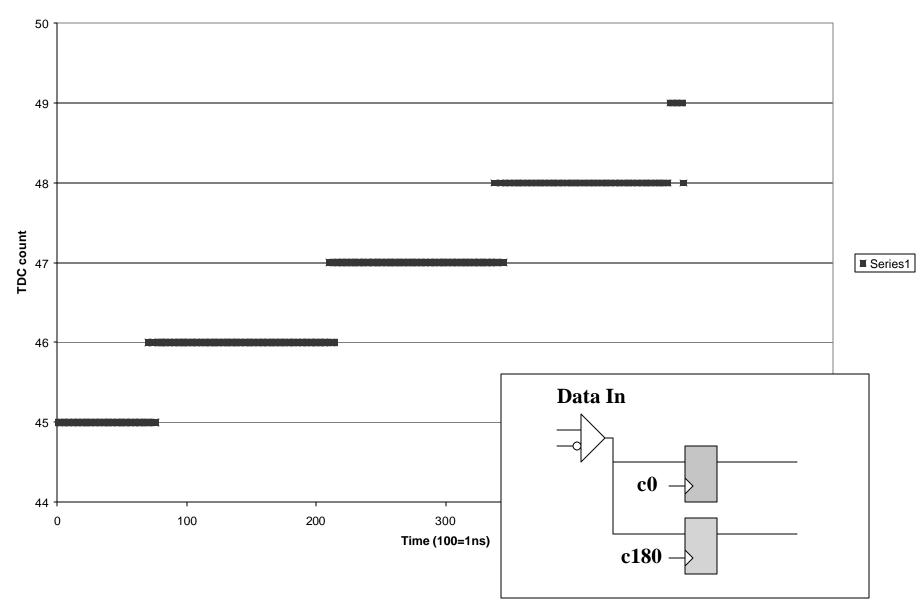

#### **DDR TDC Test Stand**

### DDR TDC (1.2ns/bin)

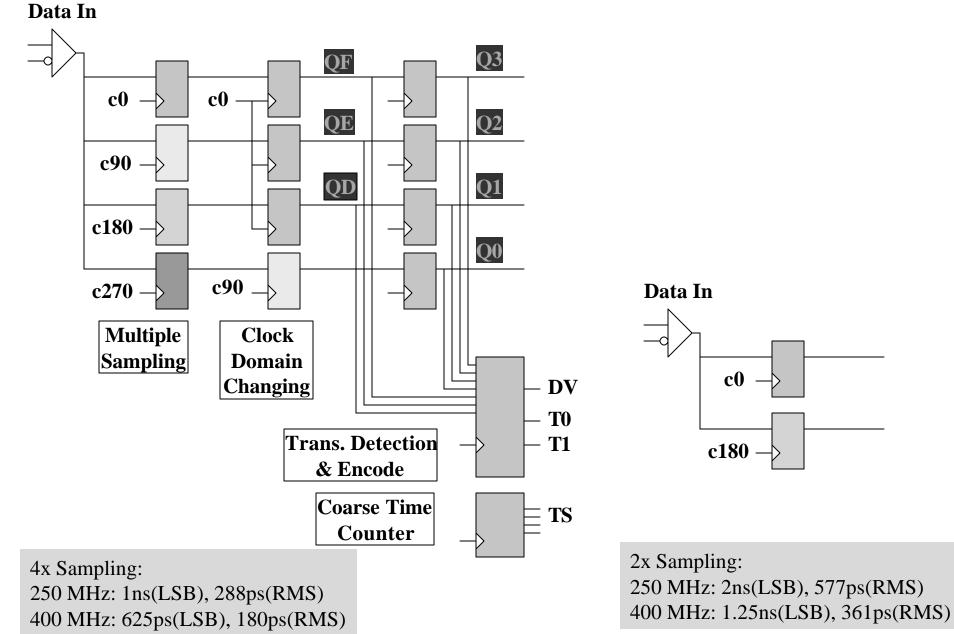

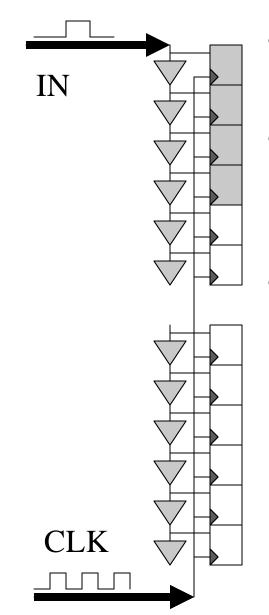

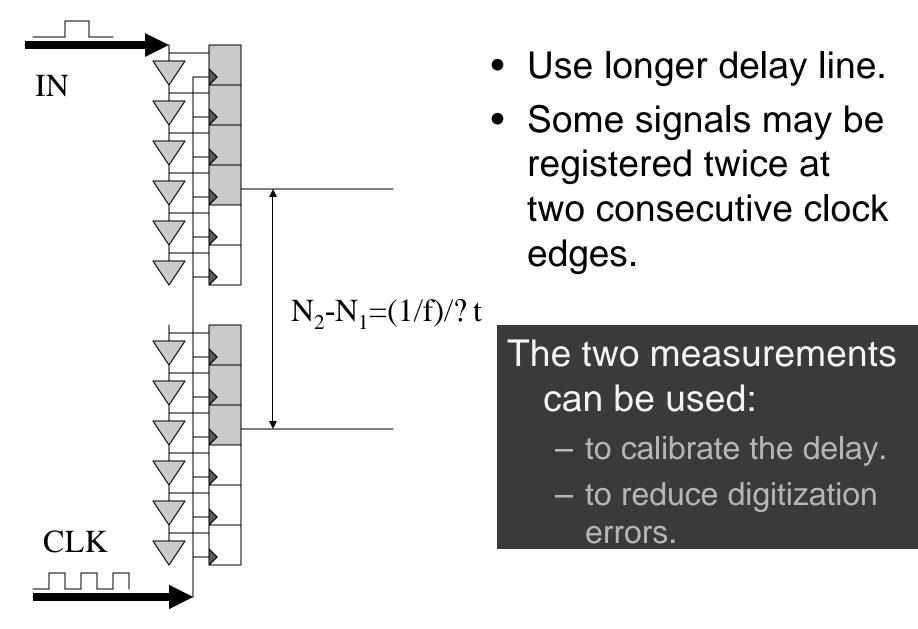

## FPGA TDC With LSB < 0.5ns

- Low cost chip family can be used. (e.g. EP1K10QC208-2 \$15.25) ∠

- Fine TDC precision can be implemented in slow devices (e.g., 0.4 ns (120ps RMS) in a 200 MHz chip).

This is a 2002 work. To be studied for 2006 devices.

### **Delay Chain Digital Compensation**

## Some Words About FPGA TDC

- Many TDC jobs can be done with FPGA purely based on digital process.

- FPGA TDC can be built near the amplifier & discriminator. Timing signals need not to travel in long cable.

- Absolute time is digitized continuously. The timing resolution is factor of sqrt(2) better than in "start-stop" scheme.

- Higher precision (LSB<0.5ns) TDC is possible.</li>

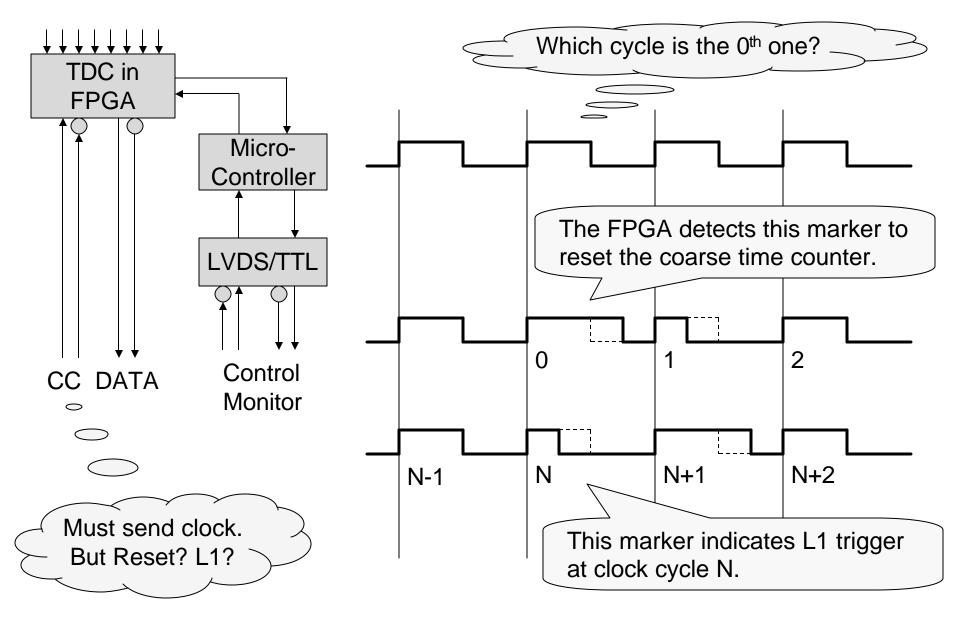

### Clock, Reset and L1 Trigger

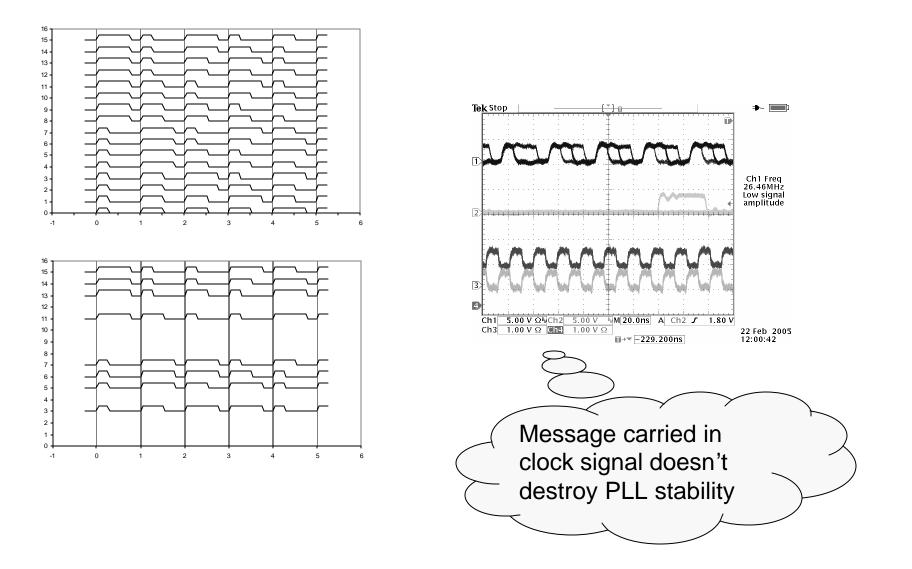

#### C5: Clock-Command Combined Carrier Coding

Message can be sent along with clock

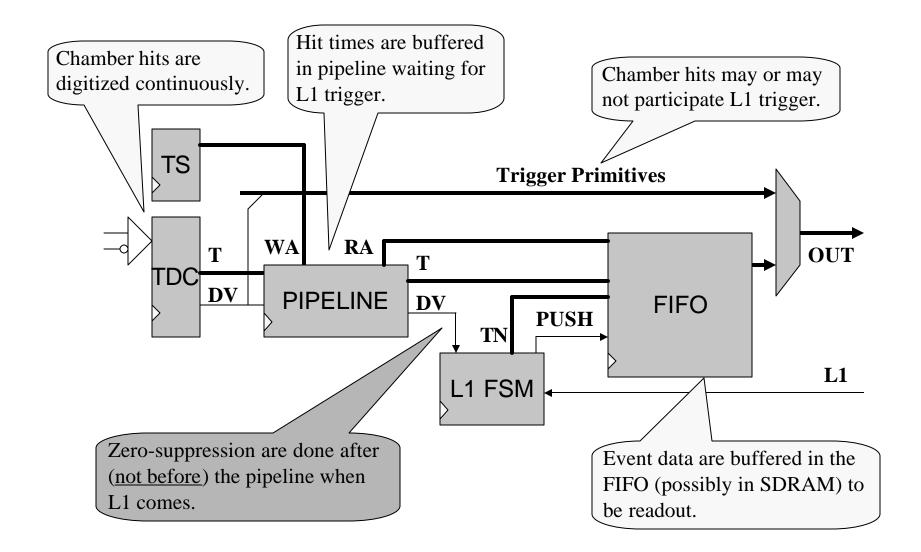

## TDC, Pipeline, Zero-Suppression etc.

# Summary

- TDC near front-end using FPGA is chosen as basic scheme.

- Appearances of front-end, TDC and readout cards are conceptually known.

- Clock, reset and L1 distribution, zerosuppression scheme and other details are to be determined. But there are sets of standard approaches to choose from.

# Beyond

- The TDC-readout system has excessive capabilities. Don't hastate to ask more if you need.

- TDC: Arrival time + pulse width.

- Chamber info in trigger.