# IPnexus<sup>®</sup> CPC5505

2.16-Compliant, High-Performance, Low-Power, Single Board Computer

User's and System Integrator's Guide

#### **Revision History**

| Revision Date | Revision History                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| 06/18/04      | Initial Production Release                                                                                      |

| 10/14/04      | Corrected board height                                                                                          |

| 04/06/05      | Clarified Ethernet topic. Added serial port default baud rate. Corrected "J21-J24 PTMC Interface Pinout" table. |

| 05/26/05      | Added PTMC Installation topic. Updated graphics.                                                                |

| 08/02/05      | Added Sensors topic. Added BIOS POST error codes. Updated for 1.8GHz processor.                                 |

| 10/14/05      | Added BMC Command Line Interface topic.                                                                         |

| 12/22/05      | Detailed which PCBs require Kapton washers between a PTMC card and the PCB.                                     |

#### **Copyright Notice**

© 2004-2005 by Performance Technologies, Inc. 1050 Southwood Drive San Luis Obispo, CA 93401

The IPnexus and Performance Technologies logos are trademarks of Performance Technologies, Inc.

CompactPCI® is a registered trademark of the PCI Industrial Computer Manufacturers Group. All other brands or names are trademarks of their respective holders.

All rights reserved. This document is the sole property of Performance Technologies, Inc.

#### **Errors and Omissions**

Although diligent efforts are made to supply accurate technical information to the user, occasionally errors and omissions occur in manuals of this type. Refer to the Performance Technologies, Inc. Web site to obtain manual revisions or current customer information: http://www.pt.com.

Performance Technologies, Inc., reserves its right to change product specifications without notice.

#### Symbols and Conventions in this Manual

The following symbols appear in this document:

**Caution:** There is risk of equipment damage. Follow the instructions.

Warning: Hazardous voltages are present. To reduce the risk of electrical shock and danger to personal health, follow the instructions.

#### Electrostatic Discharge

Caution: Electronic components on printed circuit boards are extremely sensitive to static electricity. Ordinary amounts of static electricity generated by your clothing or work environment can damage the electronic equipment. It is recommended that antistatic ground straps and anti-static mats are used when installing the board in a system to help prevent damage due to electrostatic discharge.

# **Table of Contents**

| Tables                                     | 8  |

|--------------------------------------------|----|

| Figures                                    | 9  |

| 1 Introduction                             |    |

| 1.1 Product Definition                     |    |

| 1.2 CPC5505 Features                       |    |

| 1.3 CPC5505 Functional Blocks              | 13 |

| Intel Pentium M Processor                  | 13 |

| Chipset                                    |    |

| CompactPCI Bus Interface                   |    |

| Intelligent Platform Management Controller |    |

| Sensors                                    |    |

| Memory                                     |    |

| Flash/BIOS Recovery                        |    |

| PTMC Interface                             | 17 |

| Drone Mode                                 |    |

| Power Ramp Circuitry                       |    |

| Reset                                      |    |

| Two-Stage Watchdog Timer                   |    |

| DMA                                        |    |

| Interrupts                                 |    |

| Enhanced IDE Controller                    |    |

| Universal Serial Bus (USB)                 |    |

| Counter/Timers                             |    |

| Floppy Controller                          |    |

| Real-Time Clock, CMOS RAM and Battery      |    |

| Speaker Interface                          |    |

| Serial I/O                                 |    |

| Keyboard/Mouse Controller                  |    |

| Video Interfaces                           |    |

| Ethernet Interfaces                        |    |

| LED Indicators                             |    |

| Rear-Panel I/O                             |    |

| 1.4 Software                               |    |

| BIOS                                       |    |

| Operating Systems                          | 25 |

| IPMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Hot Swap                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26                                                                                                                                           |

| 2 Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                           |

| 2.1 Unpacking                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                                                           |

| 2.2 CPC5505 System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                                                                                                                                           |

| Backplane Connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                                                                                           |

| Electrical and Environmental Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                                                           |

| 2.3 Memory Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                                                                           |

| Installing Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                                           |

| 2.4 I/O Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                                                           |

| Analog Video Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| 2.5 Video BIOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| 2.6 Connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

| 2.7 Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                              |

| 2.8 BIOS Configuration Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Console Redirection                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                           |

| 2.9 Installing an IDE Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                                                                           |

| 2.10 Installing a PTMC Device                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| 2.11 Installing the Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40                                                                                                                                           |

| 0.40 Drogramming the LEDC                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| 2.12 Programming the LEDS                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| 3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| 3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>42</b><br>42                                                                                                                              |

| 3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>42</b><br>42<br>44                                                                                                                        |

| 3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>42</b><br>42<br>44<br>44                                                                                                                  |

| 3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>42</b><br>42<br>44<br>44<br>44                                                                                                            |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)                                                                                                                                                                                                                                                                                                                                                            | <b>42</b><br>42<br>44<br>44<br>44<br>44<br>44                                                                                                |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select)                                                                                                                                                                                                                                                                                                                            | <b>42</b><br>42<br>44<br>44<br>44<br>44<br>44<br>44                                                                                          |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select)<br>SW2-3 (Video Select)                                                                                                                                                                                                                                                                                                    | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>44<br>45<br>45                                                                                    |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select)<br>SW2-3 (Video Select)<br>SW2-4 (PCI-X Enable)                                                                                                                                                                                                                                                                            | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45                                                                              |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select)<br>SW2-3 (Video Select)<br>SW2-4 (PCI-X Enable)<br>SW3-1 (Flash Write Protect/Write Enable)                                                                                                                                                                                                                                | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45                                                                  |

| 3 Configuration<br>3.1 Switch Options and Locations.<br>3.2 Switch Descriptions.<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select).<br>SW2-3 (Video Select).<br>SW2-4 (PCI-X Enable)<br>SW3-1 (Flash Write Protect/Write Enable).<br>SW3-2 (Boot Source)                                                                                                                                                                                                    | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>45                                                      |

| 3 Configuration<br>3.1 Switch Options and Locations.<br>3.2 Switch Descriptions.<br>SW1 (CPU Reset).<br>SW2-1 (Clear RTC CMOS).<br>SW2-2 (Ethernet Port Select).<br>SW2-3 (Video Select).<br>SW2-4 (PCI-X Enable).<br>SW3-1 (Flash Write Protect/Write Enable).<br>SW3-2 (Boot Source).<br>SW3-3 (Drone Reset Control).                                                                                                                                                                | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>45                                                      |

| 3 Configuration<br>3.1 Switch Options and Locations.<br>3.2 Switch Descriptions.<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS).<br>SW2-2 (Ethernet Port Select).<br>SW2-3 (Video Select)<br>SW2-3 (Video Select)<br>SW2-4 (PCI-X Enable).<br>SW3-1 (Flash Write Protect/Write Enable).<br>SW3-2 (Boot Source)<br>SW3-3 (Drone Reset Control)<br>SW3-4 (BMC CPU Power Override)                                                                                                          | <b>42</b><br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>46<br>46<br>46<br>46                                    |

| 3 Configuration<br>3.1 Switch Options and Locations.<br>3.2 Switch Descriptions.<br>SW1 (CPU Reset).<br>SW2-1 (Clear RTC CMOS).<br>SW2-2 (Ethernet Port Select).<br>SW2-3 (Video Select)<br>SW2-4 (PCI-X Enable).<br>SW3-1 (Flash Write Protect/Write Enable).<br>SW3-2 (Boot Source).<br>SW3-2 (Boot Source).<br>SW3-3 (Drone Reset Control).<br>SW3-4 (BMC CPU Power Override).<br>SW4-1 (Console Redirection).                                                                      | <b>42</b><br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>46<br>46<br>46<br>46<br>46<br>46<br>47                        |

| 3 Configuration<br>3.1 Switch Options and Locations.<br>3.2 Switch Descriptions.<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select).<br>SW2-3 (Video Select).<br>SW2-4 (PCI-X Enable).<br>SW3-1 (Flash Write Protect/Write Enable).<br>SW3-2 (Boot Source)<br>SW3-2 (Boot Source)<br>SW3-3 (Drone Reset Control)<br>SW3-4 (BMC CPU Power Override)<br>SW4-1 (Console Redirection)<br>SW4-2, SW4-3, SW4-4 (User Defined)                                      | 42<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>45                                                             |

| 3 Configuration<br>3.1 Switch Options and Locations<br>3.2 Switch Descriptions<br>SW1 (CPU Reset)<br>SW2-1 (Clear RTC CMOS)<br>SW2-2 (Ethernet Port Select)<br>SW2-3 (Video Select)<br>SW2-3 (Video Select)<br>SW2-4 (PCI-X Enable)<br>SW3-1 (Flash Write Protect/Write Enable)<br>SW3-2 (Boot Source)<br>SW3-2 (Boot Source)<br>SW3-3 (Drone Reset Control)<br>SW3-4 (BMC CPU Power Override)<br>SW4-1 (Console Redirection)<br>SW4-2, SW4-3, SW4-4 (User Defined)<br>4 IDE Interface | 42<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45<br>45<br>45<br>45<br>45<br>46<br>46<br>46<br>46<br>46<br>46<br>46<br>46<br>46<br>46<br>48 |

| Secondary IDE Channel                        |    |

|----------------------------------------------|----|

| 4.3 I/O Mapping                              | 49 |

| 5 Watchdog Timer                             | 50 |

| 5.1 Overview                                 | 50 |

| Power-Up Initialization                      | 51 |

| Time-Out Values                              | 51 |

| 5.2 Using the Watchdog in an Application     | 51 |

| Watchdog Reset                               | 51 |

| Watchdog NMI                                 | 52 |

| 6 BIOS Recovery                              | 55 |

| 6.1 BIOS Recovery Module                     | 55 |

| Forcing a Boot from the BIOS Recovery Module | 56 |

| Flash Utility Program                        | 56 |

| 7 System Monitoring and Alarms               | 57 |

| 7.1 Overview                                 |    |

| 7.2 BMC Command Line Interface               | 57 |

| Login                                        | 57 |

| NULL and Operator Account Commands           |    |

| Administrator Account Commands               | 58 |

| OEM Account Commands                         | 59 |

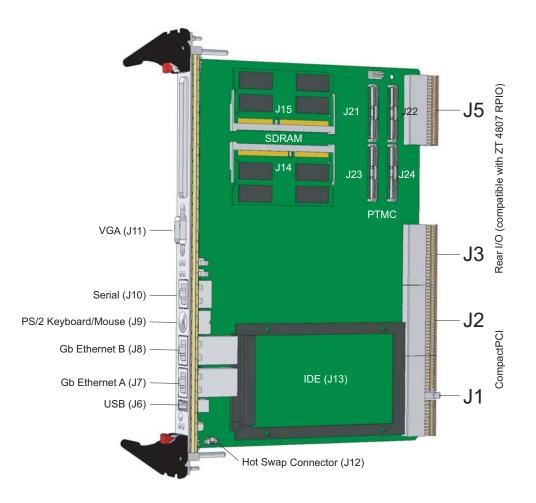

| 8 Connectors                                 | 60 |

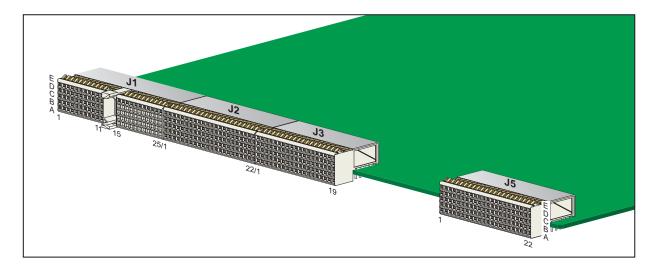

| 8.1 Backplane Connectors                     | 62 |

| J1 (CompactPCI Bus Connector)                | 62 |

| J2 (CompactPCI Bus Connector)                | 63 |

| J3 (Rear-Panel Gigabit Ethernet Connector)   | 64 |

| J5 (Rear-Panel User I/O Connector)           | 65 |

| 8.2 Front Panel Connectors                   | 66 |

| J6 (USB Connectors)                          | 66 |

| J7, J8 (Ethernet Connectors)                 | 66 |

| J9 (Keyboard/Mouse Connector)                | 67 |

| J10 (COM1 Serial Port)                       | 67 |

| J11 (Video Interface)                        | 68 |

| 8.3 Internal Connectors                      |    |

| J12 (Hot Swap Ejector Switch Connector)      |    |

| J13 (EIDE Interface)                         | 69 |

| J14, J15 (DDR SO-DIMM Connectors)            | 69 |

| J21-J24 (PTMC Interface)                     |    |

| 9 Specifications                                | 72 |

|-------------------------------------------------|----|

| 9.1 Electrical and Environmental Specifications | 72 |

| CPC5505 Absolute Maximum Ratings                | 72 |

| DC Operating Characteristics                    | 73 |

| Battery Backup Characteristics                  | 73 |

| 9.2 CPC5505 Reliability                         | 74 |

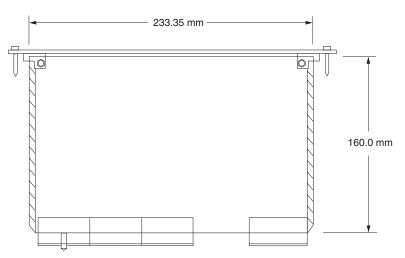

| 9.3 Mechanical Specifications                   | 74 |

| Board Dimensions and Weight                     | 74 |

| CPC5505 Connectors                              | 75 |

| 10 System Registers                             | 76 |

| 10.1 System Register Definitions                | 76 |

| Flash Control (78h)                             | 77 |

| Watchdog (79h)                                  |    |

| BIOS POST Codes (80h)                           |    |

| ENUM, WD NMI Status, ENET Routing (E1h)         | 82 |

| Board ID (E2h)                                  | 83 |

| Switch Monitors (E3h)                           |    |

| Video/LED Control (E5h)                         |    |

| HCINDEX - Host Control Index (E6h)              |    |

| HCDATA - Host Control Function Data (E7h)       |    |

| INT- Interrupt Status and Mask Register (E8h)   | 87 |

| 11 Reset                                        |    |

| 11.1 Reset Types and Sources                    |    |

| Backend Power Down Sources                      |    |

| General Reset Sources                           |    |

| NMI Sources                                     |    |

| 12 Thermal Considerations                       |    |

| 12.1 Thermal Requirements                       |    |

| 12.2 Temperature Monitoring                     |    |

| 13 Agency Approvals                             |    |

| 13.1 UL 60950 Certification                     |    |

| 13.2 CE Certification                           |    |

| 13.3 FCC Regulatory Information                 |    |

| 14 Data Sheet and Device Driver Reference       |    |

| 14.1 Chipset                                    |    |

| 14.2 CompactPCI                                 |    |

| 14.3 Ethernet                                   |    |

|                                                 |    |

| <br>In Case of Difficulty                             | ~ 7 |

|-------------------------------------------------------|-----|

| 14.7 User Documentation                               | 96  |

| 14.6 I/O Controller                                   | 95  |

| 14.5 Pentium M Processor                              | 95  |

| 14.4 Intelligent Platform Management Interface (IPMI) | 95  |

# Tables

| Table 1. CPC5505 Sensors                                 | 16 |

|----------------------------------------------------------|----|

| Table 2. Shared Video RAM                                | 32 |

| Table 3. CPC5505 Switch Cross-Reference                  |    |

| Table 4. Connector Assignments                           | 60 |

| Table 5. J1 CompactPCI Bus Connector Pinout              | 62 |

| Table 6. J2 CompactPCI Bus Connector Pinout              | 63 |

| Table 7. J3 Rear-Panel Gigabit Ethernet Connector Pinout |    |

| Table 8. J5 Rear-Panel User I/O Connector Pinout         | 65 |

| Table 9. J6 USB Connector Pinout                         |    |

| Table 10. J7 Ethernet Connectors Pinout                  |    |

| Table 11. J9 Keyboard and Mouse Connector Pinout         | 67 |

| Table 12. J10 COM1 Serial Port Pinout                    | 67 |

| Table 13. J11 Video Interface Pinout                     | 68 |

| Table 14. J12 Hot Swap Ejector Switch Connector Pinout   | 68 |

| Table 15. J13 EIDE Interface Pinout                      | 69 |

| Table 16. J21-J24 PTMC Interface Pinout                  | 70 |

| Table 17. Power Consumption                              | 73 |

| Table 18. System Event Log BIOS POST Error Codes         | 81 |

# Figures

| Figure 1. CPC5505 Faceplate                     | 12 |

|-------------------------------------------------|----|

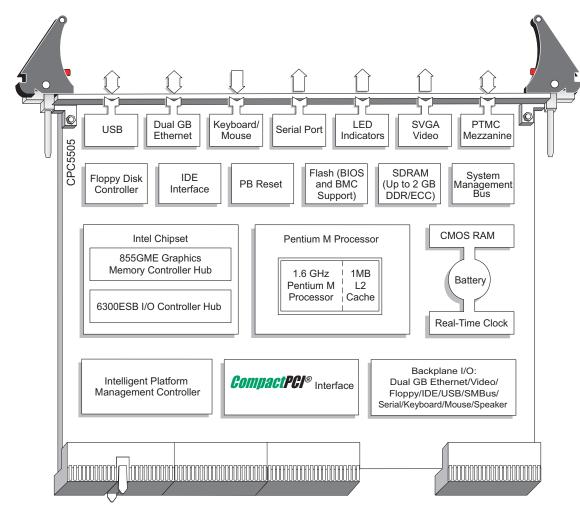

| Figure 2. CPC5505 Functional Block Diagram      | 13 |

| Figure 3. Ethernet BIOS Setup                   | 23 |

| Figure 4. Memory Module Orientation             | 29 |

| Figure 5. Memory Address Map Example            | 30 |

| Figure 6. I/O Address Map                       | 31 |

| Figure 7. Setup Screen Layout                   |    |

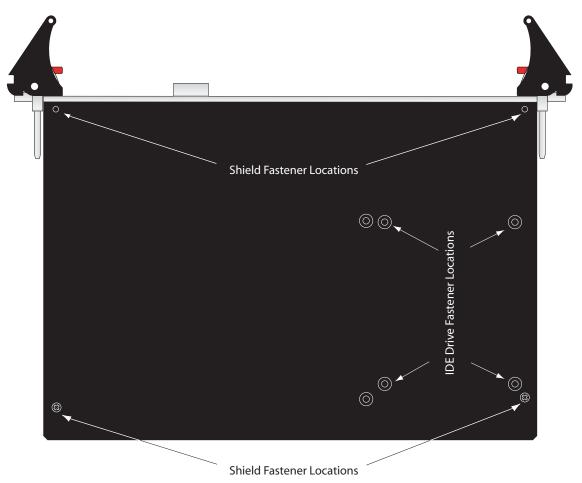

| Figure 8. Solder-Side Shield                    | 35 |

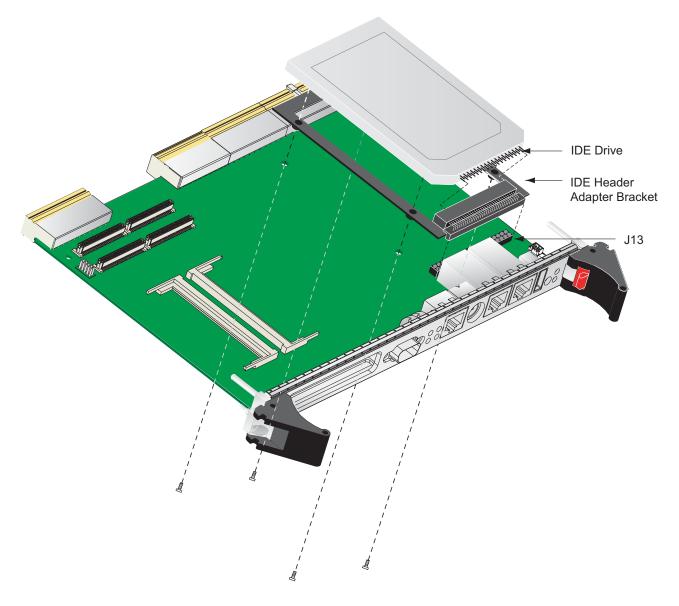

| Figure 9. IDE Drive Replacement                 | 36 |

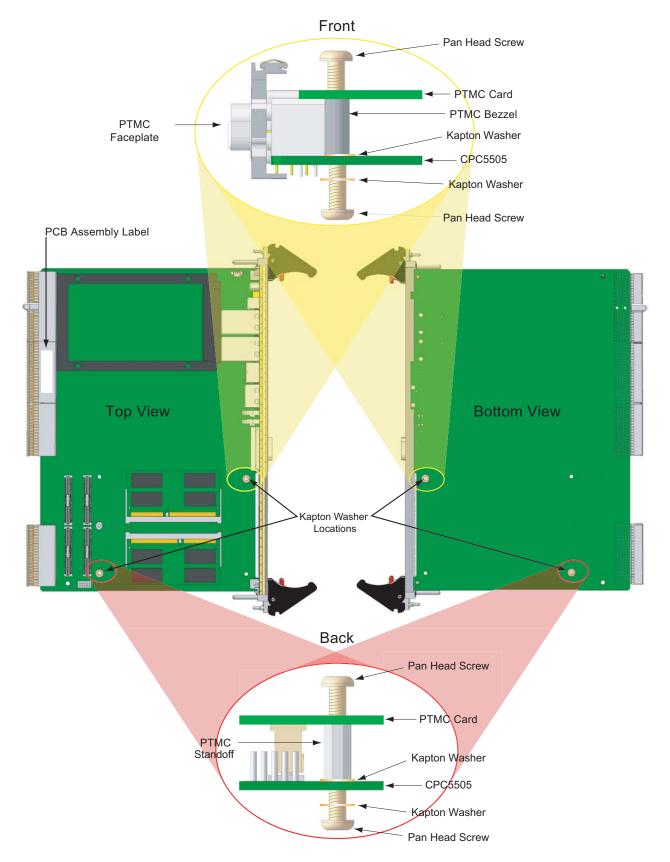

| Figure 10. PTMC Card Installation               | 38 |

| Figure 11. Kapton Washer Locations              | 39 |

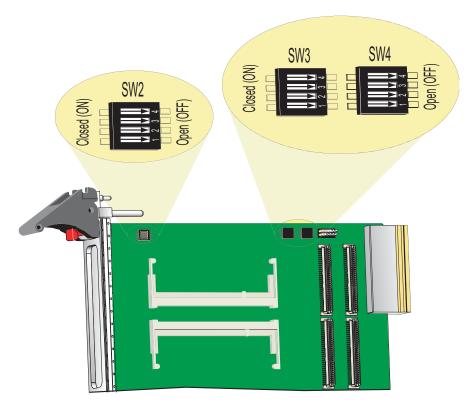

| Figure 12. Factory Default Switch Configuration | 43 |

| Figure 13. Customer Switch Configuration        | 43 |

| Figure 14. Watchdog Timer Architecture          | 50 |

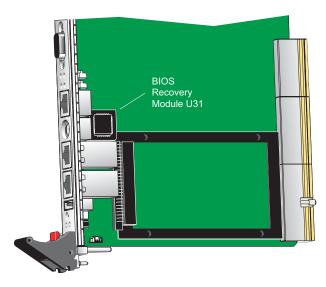

| Figure 15. BIOS Recovery Socket Location        | 55 |

| Figure 16. Connector Locations                  | 61 |

| Figure 17. Backplane Connectors Pin Locations   | 61 |

| Figure 18. CPC5505 Board Dimensions             | 74 |

Section

# Introduction

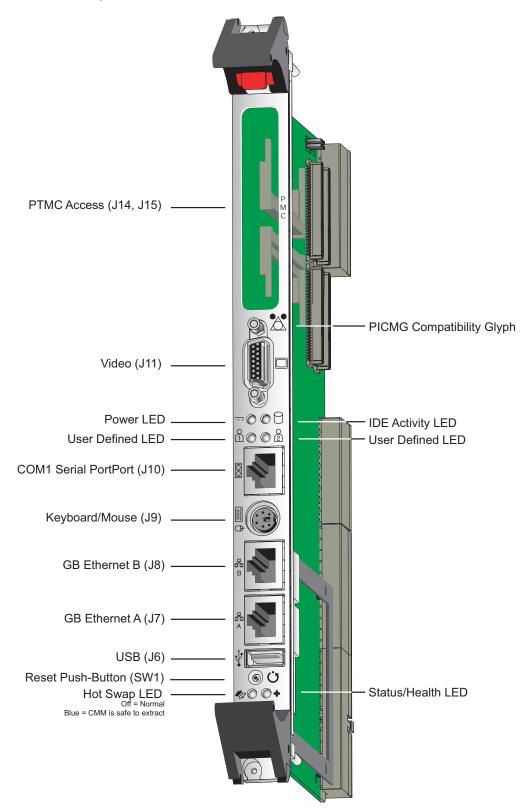

This section provides a brief introduction to the IPnexus® CPC5505 System Master Processor Board. It includes a product definition, a list of product features, a "CPC5505 Faceplate" figure, a functional block diagram, and a description of each block. Unpacking, initial board configuration, and other setup information are provided in Section 2, "Getting Started."

# **1.1 Product Definition**

The CPC5505 is an Intel<sup>®</sup> Pentium<sup>®</sup> M-based single board computer designed for carriergrade telecom and Internet applications. The board incorporates the Intel 855GME chipset supporting a 400MHz processor bus and 2GB single channel 333MHz DDR SDRAM with ECC. The CPC5505 is fully compliant with PICMG 2.16 (Packet Switching Backplane) and also provides a 32-bit/33MHz Compact PCI bus.

The CPC5505's Pentium M Processor provides optimum performance in uniprocessing or multiprocessing systems. The board occupies one CompactPCI slot (4HP) and comes with a Pentium M Processor installed. Additionally, the CPC5505 supports hosting hot swap peripherals in a powered system.

The on-board Intelligent Platform Management Controller (IPMC or BMC) monitors, controls, and performs remote diagnostics for many on- and off-board functions through five IPMI (Intelligent Platform Management Interface) compliant system management bus interfaces.

Support for an optional PTMC card is provided on the faceplate to add base board functionality such as IPSec accelerators, network processors, and additional Ethernet connectivity.

# 1.2 CPC5505 Features

- Single Slot 6U CompactPCI System Master Single Board computer

- CompactPCI Specification, PICMG 2.0, R 2.1 compliant

- CompactPCI Hot Swap Specification, PICMG 2.1, R 2.0 compliant

- CompactPCI Packet Switched Backplane Specification, PICMG 2.16, R 1.0 compliant

- CompactPCI System Management Specification, PICMG 2.9, R 1.0 compliant

- IPMI v1.5 specification compliant

- Designed for NEBs level-3 and ETSI installations

- 1.8 GHz Intel Pentium M Processor (400 MHz FSB)

- Integrated 1 MB L2 cache

- 32-bit/33 MHz Compact PCI bus

- 64-bit/66 MHz PTMC interface

- SMBus

- Intel ICH and 855GME GMCH Chipset

- Intel 855GME Graphics Memory Controller Hub (GMCH-M) North Bridge

- Intel 6300ESB I/O Controller Hub (ICH) South Bridge

- Dual 10/100/1000 Mb/s Ethernet links through backplane J3 (PICMG 2.16), faceplate J7/J8.

- Supports up to 2 GB of DDR SDRAM with ECC at 2.7 GB/s peak bandwidth.

- Performance Technologies' Embedded BIOS (AMI core) stored in local flash memory

- VxWorks, Windows® 2000/XP and Linux Operating Systems.

- Two IPMB interfaces on backplane J1 and J2 (PICMG 2.9).

- Standard AT® peripherals include:

- Real-time clock/CMOS RAM (146818)

- Two IDE interfaces. On board ATA/100 hard drive. Rear Panel ATA/33 support

- Two 16C550 RS-232 serial ports

- Video Interface

- Floppy disk controller

- Speaker interface (rear panel only)

- Three USB ports

- PC/AT keyboard/mouse controller

- Supports 2.5" low-profile, board-mounted, EIDE hard drive

- Dual-stage watchdog timer

- Push-button Reset switch

- LEDs:

- Status (Green/Amber)

- Two User (Green/Amber/Off)

- Local IDE Disk Activity (Green/Off)

- Hot Swap (Blue/Off)

- Power/Reset (Green/Amber/Off)

- Ethernet A and B:

- +10/100/1000 (Off/Green/Amber)

- Link (Green)

- Activity (Flashing Green)

#### Figure 1. CPC5505 Faceplate

# 1.3 CPC5505 Functional Blocks

Below is a functional block diagram of the CPC5505. The following topics provide overviews of the functional blocks.

# **Intel Pentium M Processor**

The CPC5702 incorporates a 1.8GHz core frequency Pentium M processor in a 479-pin FCBGA package.

The Intel Pentium M processor is a high performance, low power, 32-bit CISC processor. It is manufactured on Intel's advanced 0.13 micron process technology with copper interconnect. The processor maintains support for MMX<sup>™</sup> technology and Internet streaming SIMD instructions. It also provides full compatibility with IA-32 software. The on-die separated 32 KB Level 1 instruction and data caches and the 1MB Level 2 cache with advanced transfer cache architecture enable significant performance improvement over other mobile processors.

The 400MHz processor system bus uses Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four times per bus clock. Along with the 4X data bus, the address bus can deliver addresses two times per bus clock. The processor features Enhanced Intel SpeedStep technology, which enables real-time dynamic switching between multiple voltage and frequency points instead of two points supported on previous versions of Intel SpeedStep technology. For the applications that require constant computing power, SpeedStep can be disabled by setting the CPU to "Maximum Performance" in the BIOS configuration.

The "Pentium M Processor" topic in Section 14 contains a link to the data sheet for this device.

# Chipset

The CPC5505 incorporates the Intel 855GME Graphics Memory Controller Hub (GMCH-M) as the North Bridge and the Intel 6300ESB I/O Controller Hub as the South Bridge Chip.

#### Intel 855GME Graphics Memory Controller Hub (GMCH-M) North Bridge

The Intel 855GME GMCH provides bus-control signals, address paths, and data paths for transfers between the processor's host bus, the Hub Link 1.5 bus, Video and main memory. The North Bridge features:

- Processor/Host Bus Support

- Memory System

- System Interrupts

- Video Stream Decoder

- Video Overlay

- Analog display support

- Internal Graphics Features

- Hub Interface to Intel 6300ESB I/O ControllerPower Management

The "Chipset" topic in Section 14 contains a link to more information for this device.

#### Intel 6300ESB I/O Controller Hub South Bridge

The Intel 6300ESB I/O Controller Hub (ICH) is a multifunctional PCI device implementing the PCI-to-ISA bridge, PCI IDE functionality, USB host/hub functionality, and enhanced power management. The ICH South Bridge features:

- 8-Bit Hub Interface

- PCI-X BUS I/F

- PCI BUS I/F

- Integrated IDE controller

- USB

- Power Management Logic

- External Glue Integration

- Firmware Hub(FWH) I/F supports BIOS Memory size up to 8 MB

- Enhanced DMA Controller

- Real- Time Clock

- Interrupt Controller

- Multimedia Timers based on 82C54

- Watch dog timer

- SMBus

- Integrated 16550 compatible UART

- Port 60/64 Emulation

- GPIO

The "Chipset" topic in Section 14 contains a link to more information for this device.

## **CompactPCI Bus Interface**

The CPC5505 processor board uses the Intel 6300ESB I/O Controller Hub to support a 32-bit, 33 MHz CompactPCI interface at backplane connectors J1/J2.

Performance Technologies designed the CPC5505 to be used as a System Master or a stand-alone processor board in a CompactPCI system. The board occupies one CompactPCI slot (4HP) with Pentium M processor installed. Its CompactPCI bus design allows it to supports a maximum of seven CompactPCI peripheral cards.

The CPC5505 backplane is compliant with the CompactPCI Specification, PICMG 2.0, Version 2.1. When used in a hot swap compliant backplane and in accordance with the *CompactPCI Hot Swap Specification, PICMG 2.1, Version 2.0*, the CPC5505 supports hosting hot swap peripherals in a powered system. The CPC5505 can also function in a standard (non-hot swap) CompactPCI system. The CPC5505 is also compliant with the *CompactPCI System Management Specification, PICMG 2.9 Version 1.0, PICMG 2.15 R1.0 configuration 7 (PT7CC)*, and with the *CompactPCI Packet Switching Backplane Specification, PICMG 2.16, Version 1.0.*

Section 14, "Data Sheet Reference," contains links to the PICMG Web site, where these CompactPCI Specifications may be obtained.

For more information on Hot Swap implementation, refer to the *Performance Technologies Hot Swap Kit Software Manual*.

## Intelligent Platform Management Controller

The CPC5505 includes an Intelligent Platform Management Controller (IPMC or BMC) based on the Qlogic Zircon UL. The BMC subsystem monitors, controls, and performs remote diagnostics for many on- and off-board functions through IPMI (Intelligent Platform Management Interface) compliant system management bus interfaces.

The BMC monitors system sensors for system management events, such as overtemperature, out-of-range voltages, fan failures, etc., and logs any occurrences in its non-volatile System Event Log (SEL). The BMC also provides the interface to the sensors and SEL so system management software can poll and retrieve the present status of the system.

The CPC5505 is compliant with standard Intelligent Platform Management Interface v1.5 Specification functionality. See the Intelligent Platform Management Interface in Section14 for information about this specification.

### Sensors

Several sensors on board the CPC5505 collect status data and relay the information to the Intelligent Platform Management Controller. The following table describes each onboard sensor.

| Sensor Number (dec) | Sensor Name    | Sensor Description                                                    |

|---------------------|----------------|-----------------------------------------------------------------------|

| 80                  | Temp - CPU     | Processor core temperature                                            |

| 81                  | Temp - DIMM1   | Board solder side temperature behind DIMM1                            |

| 82                  | Temp - DIMM2   | Board solder side temperature behind DIMM2                            |

| 96                  | IPMB_PWR3      | 3.3V derived from IPMB_PWR for IPMC core                              |

| 97                  | IPMB_PWR       | 5V standby IPMB (standby) power after conditioning                    |

| 98                  | VIO            | Backplane I/O voltage after power control                             |

| 99                  | VCC2_5         | 2.5V regulated power for DDR memory                                   |

| 100                 | VCC1_5         | 1.5V regulated power for Southbridge                                  |

| 101                 | VGME_CORE      | 1.35V regulated power for Northbridge                                 |

| 102                 | VREF1_25       | 1.25V reference voltage for DDR memory                                |

| 103                 | VTT1_25        | 1.25V termination voltage for DDR memory                              |

| 104                 | VCCP           | 1.05V termination voltage for CPU frontside bus                       |

| 105                 | VBAT_MON       | Battery voltage                                                       |

| 106                 | VCC            | 5V backplane voltage after power control                              |

| 107                 | VCC3           | 3.3V backplane voltage after power control                            |

| 108                 | P12V           | +12V backplane voltage after power control                            |

| 109                 | N12V           | -12V backplane voltage after power control                            |

| 110                 | VCCCORE        | CPU core voltage                                                      |

| 112                 | FRNT PNL EJECT | Ejector handle switch status:<br>Open: asserted<br>Closed: deasserted |

#### Table 1. CPC5505 Sensors

### Memory

The CPC5505 includes two 200-pin, right angle, Small Outline Dual Inline Memory Module (SODIMM) socket populated with up to 2GB DDR SDRAM with ECC at 2.7Gbyte/s peak bandwidth.

## Flash/BIOS Recovery

The CPC5505 incorporates 16 MB of on-board, programmable, BIOS Flash memory. The BIOS resides in the first megabyte of flash. The FLASH.EXE utility allows you to install an operating system image or any executable image into the remaining 15MB of flash. See the *Performance Technologies Embedded BIOS Software Manual* for more information. The User Documentation topic in Section 14 provides a link to this document.

A second flash device is used as a BIOS recovery module. The CPC5505 can be configured to use either device for boot control. When booting from the BIOS recovery module, the BIOS update utility can access the onboard flash device by manipulating the system registers. The onboard flash is write protected on power up and reset. See Section 6, "BIOS Recovery," for more information.

# **PTMC** Interface

The CPC5505 is also a PMC carrier card that supports the following specifications:

- Complies with PICMG 2.15 R1.0 configuration 7 (PT7CC).

- Dual channel Ethernet links (MDI) compatible with PICMG 2.15 ECN 2.15-1.0-001 (Ethernet MDI Links on PTMC, configurations 5 and 6).

- Complies with IEEE1386.1 PCI Mezzanine Card (PMC).

- Complies with VITA 39: PCI-X for PMC (66MHz).

The PCI Telecom Mezzanine Card (PTMC) interface is compatible with the PICMG 2.15 PT7CC specification. The PTMC provides a way to add modules such as IPSec accelerators and network processors to increase base board functionality.

The CPC5505 PTMC site provides an industry standard interface for a high performance, dual channel, gigabit Ethernet PMC mezzanine card. High performance is achieved by means of a 64-bit wide, 66MHz interface that is capable of PCI or PCI-X signaling. Dual channel Ethernet links (MDI<sup>1</sup>) are routed on PTMC interface connector J24 per PICMG 2.15 configurations 5 and 6. The Ethernet links can be routed to CPC5505 rear-panel gigabit Ethernet connector J3 for connection to the CompactPCI backplane per PICMG 2.16.

PCI/PCI-X signaling is supported for 3.3V VIO. Contact the factory if 5V mezzanine support is required.

The CPC5505 is backward compatible with all standard 32-bit and 64-bit PMC cards. However, these cards do not respect the PTENB# signal. We advise caution when installing a standard PMC card with P4 (rear I/O) signaling. Please check the pinout carefully. PTMC modules interfacing to the CPC5505 must advertise their PTID (PCI Telecom Identifier) as "configuration 7" before they are enabled (PTENB# asserted). PTMC modules supporting configurations 1,2,3,4,5,6 will not have their PTMC interface enabled by PTENB#.

Please contact the factory if I<sup>2</sup>C bus connectivity to the PTMC site is desired. It is not enabled in the default configuration.

The mezzanine interface is at J21-J24 on the CPC5505. See Section 8, "Connectors," for more information.

# **Drone Mode**

Typically, the CPC5505 operates as the System Master from the system slot. The CPC5505 can also operate in Drone Mode from a peripheral slot. In Drone Mode, the CPU board receives power from the system but it cannot communicate on the CompactPCI bus. Onboard logic uses SYSEN# to qualify the CPC5505's location when inserted in a peripheral slot, thereby isolating the board from the CompactPCI bus.

The CPC5505 can be hot swapped when operating in Drone Mode (in peripheral slots, the board is operating in isolation from the backplane).

**Caution:** The CPC5505 is not intended to be hot swapped in the system slot. Hot swapping the CPU board in the system slot may damage other boards in the system.

# **Power Ramp Circuitry**

The CPC5505 features a hot swap controller with power ramp circuitry that enables the board's voltages to ramp in a controlled fashion. The power ramp circuitry eliminates any large voltage or current spikes caused by removing or inserting hot swappable boards while the system is still under power. This controlled ramping is a requirement of the *CompactPCI Hot Swap Specification*, *PICMG 2.1*, *Version 2.0*.

The CPC5505's hot swap controller unconditionally resets the board when it detects that the 3.3V, 5V, and 12V supplies are below an acceptable operating limit. These limits are defined as 4.75V (5V supply), 3.15V (3.3V supply), and 10.0V (+12V supply).

Fault current sensing is also provided. If a board fault (short circuit) or over-current condition is detected, the hot swap controller automatically removes power from the CPC5505 components.

## Reset

The CPC5505 provides the following reset types:

- Push-button reset

- Backplane reset input

• Watchdog timer reset

See Section 11, "Reset," for more information.

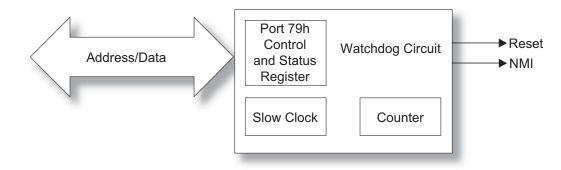

# Two-Stage Watchdog Timer

The watchdog timer optionally monitors system operation and is programmable for one of eight different timeout periods (from 0.25s to 256s). It is a two-stage watchdog, meaning that it can be enabled to produce a Non-Maskable Interrupt (NMI) before it generates a system reset. Failure to strobe the watchdog timer within the programmed time period may result in an NMI, a system reset, or both. A register bit is set if the watchdog timer caused the reset event. This watchdog timer register is not cleared on reset. It is cleared on power-up, enabling system software to take appropriate action on reboot.

See Section 5, "Watchdog Timer," for more information.

## DMA

An enhanced, 8237-style DMA controller is provided on the CPC5505 for use by on-board peripherals. DMA channel 2 is assigned to the optional floppy drive.

The CPC5505's DMA controllers reside in the Intel 6300ESB I/O Controller Hub. The "Chipset" topic in Section 14 provides a link to the data sheet for this device.

### Interrupts

Two enhanced, 8259-style interrupt controllers implemented in the Intel 6300ESB ICH, provide the CPC5505 with a total of 15 interrupt inputs. Interrupt controller features include support for:

- Level-triggered and edge-triggered inputs

- Individual input masking

- Fixed and rotating priorities

Interrupt sources include:

- Counter/timers

Floppy disk

- Real-time clock

- Serial I/O DMA channels

- On-board PCI devices

- System timer

IDE interface

- Keyboard/Mouse

Enhanced capabilities include the ability to configure each interrupt level for active high-going edge or active low-level inputs.

The CPC5505's interrupt controller resides in the Intel 855GME Chipset. The "Chipset" topic in Section 14 provides a link to the data sheet for this device.

## **Enhanced IDE Controller**

The CPC5505 features an IDE controller that supports onboard and optional external IDE drives. ATA/100 is supported on the primary IDE channel, allowing up to 100 MBps throughput. ATA/33 is supported on the secondary IDE channel, allowing up to 33 MBps throughput.

Primary channel IDE signals are available through internal connector J13. Secondary channel IDE signals are available through rear-panel I/O connector J5. See Section 4, "IDE Interface," for more about the CPC5505's IDE support.

The CPC5505's IDE controller resides in the 6300ESB ICH Chipset. The "Chipset" topic in Section 14 provides a link to the data sheet for this device. Connector locations and pinouts are documented in Section 8, "Connectors."

# **Universal Serial Bus (USB)**

The Universal Serial Bus (USB) provides a common interface to slower-speed peripherals such as keyboard, serial ports, and mouse ports. The CPC5505 supports booting from a USB CD-ROM or floppy device.

The CPC5505 supports three USB ports. One v2.0 USB port (Port 0) is available at faceplate connector J6. Two v1.1 USB ports (Port 1 and Port 2) are directed through RPIO connector J5.

The CPC5505's USB resides in the 6300ESB ICH Chipset. The "Chipset" topic in Section 14 provides a link to the data sheet for this device. Connector locations and pinouts are documented in Section 8, "Connectors."

# **Counter/Timers**

Three counter/timers as defined for the PC/AT® are included on the CPC5505. Operating modes supported by the counter/timers include:

Interrupt on count

• Frequency divider

Software triggered

Square wave generatorHardware triggered

One shot

The CPC5505's 8254-compatible counter/timer resides in the ICH Southbridge. The "Chipset" topic in Section 14 provides a link to the data sheet for this device.

# Floppy Controller

The CPC5505 includes a standard floppy disk controller. The floppy disk controller supports an optional external floppy drive that is compatible with an 82077 diskette drive controller and supports PC-AT and PS/2 modes. Floppy signals are available through RPIO connector J5.

The CPC5505's floppy disk controller resides in the National Semiconductor PC87417 I/O controller. The "I/O Controller" topic in Section 14 provides a link to the data sheet for this device. Connector locations and pinouts are documented in Section 8, "Connectors."

**NOTE:** Floppy disks are magnetically recorded media. Avoid placing floppy disk drives near magnetic sources such as power supplies.

## **Real-Time Clock, CMOS RAM and Battery**

The real-time clock performs timekeeping functions and includes 256 bytes of battery- backed CMOS RAM in two banks that are reserved for BIOS use. Timekeeping features include a time-of-day clock and a multi-century calendar with alarm features and century rollover. The clock is accurate to  $\pm$  13 minutes/year at 25 °C. The time, date, and CMOS values can be specified or returned to their defaults by using the BIOS Setup program. See the "BIOS Configuration Overview" topic in Section 2 for more information.

**NOTE:** The recommended method of accessing the date in systems with IPnexus processor boards is indirectly from the real time clock via the BIOS. The BIOS on IPnexus processor boards contains a century checking and maintenance feature. This feature checks the two least significant digits of the year stored in the real time clock during each BIOS request (INT 1Ah) to read the date and, if less than 80 (1980 is the first year supported by the PC), updates the century byte to 20. This feature enables operating systems and applications using the BIOS date/time services to reliably manipulate the year as a four-digit value.

A coin-cell battery located on the CPC5505 processor board powers the real-time clock and CMOS memory. When the CPC5505 is not powered externally, the battery has an estimated life of six years. When the CPC5505 is powered up, the 3.3 V backplane current from the power supply extends the life of the battery.

The CPC5505's real-time clock resides in the National Semiconductor PC87417 I/O controller. The "I/O Controller" topic in Section 14 provides a link to more information for this device.

## **Speaker Interface**

For external speaker interfacing, the CPC5505 supports an external AT-compatible speaker through the RPIO connector J5. Connector locations and pinouts are documented in Section 8, "Connectors."

## Serial I/O

The CPC5505 provides two 16C550, PC-compatible serial ports. COM1 is available at the faceplate via 8-pin RJ-45 connector J10 and is also routed to connect to the IPMI Controller Emergency Management Serial Port (EMP). COM1 and COM2 are also available to an RTM via RPIO connector J5.

Both ports are compatible with RS-232 signaling levels and support data transfers at speeds up to 115.2 Kbits/sec with BIOS support. The baud rate defaults to 9600 and is set in the BIOS Setup utility.

The CPC5505's serial controller resides in the National Semiconductor PC87417 I/O controller. The "I/O Controller" topic in Section 14 provides a link to more information for this device. Connector locations and pinouts are documented in Section 8, "Connectors."

### Keyboard/Mouse Controller

The CPC5505 includes an on-board PC/AT keyboard/mouse controller. Keyboard and mouse signals are available at the faceplate via J9. A "Y" interface cable is required to use both interfaces at once. The keyboard and mouse signals are also available through the RPIO connector J5.

The CPC5505's keyboard/mouse controller resides in the National Semiconductor PC87417 I/O controller. The "I/O Controller" topic in Section 14 provides a link to more information for this device. Connector locations and pinouts are documented in Section 8, "Connectors."

## **Video Interfaces**

The CPC5505 provides on-board video using the 855GME Graphics Memory Controller Hub (GMCH-M). GMCH-M provides support for progressive scan analog monitor pixel resolution up to 1600x1200 at 85-Hz refresh and up to 2048x1536 at 75-Hz refresh.

VGA-compatible video signals are available at the CPC5505 faceplate via connector J11 and also at rear-panel I/O connector J5.

The "Chipset" topic in Section 14 contains a link to the data sheet for the GMCH-M. Connector locations and pinouts are documented in Section 8, "Connectors."

## **Ethernet Interfaces**

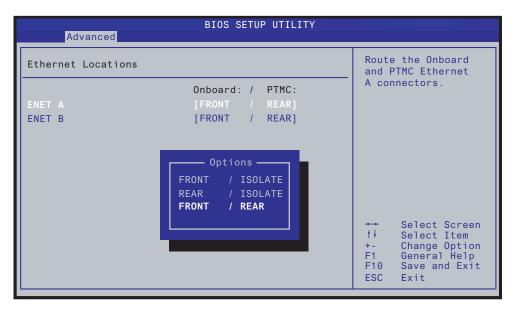

The CPC5505 provides two onboard 10/100/1000Base-T Ethernet channels (ENET A and ENET B) through the Intel 82546 Gigabit Ethernet PCI Controller. Both Ethernet channels can be directed through the BIOS Setup utility to faceplate RJ-45 connectors J7 and J8, which have LEDs to indicate the status of each channel. Alternatively, both Ethernet channels can be routed to RPIO connector J3. See the "Ethernet BIOS Setup" figure below.

The CPC5505 PTMC site also provides an interface for a dual channel gigabit Ethernet PMC mezzanine card. The BIOS Setup utility allows these Ethernet signals to be either isolated or routed to CPC5505 RPIO connector J3. See the "PTMC Interface" topic for more information.

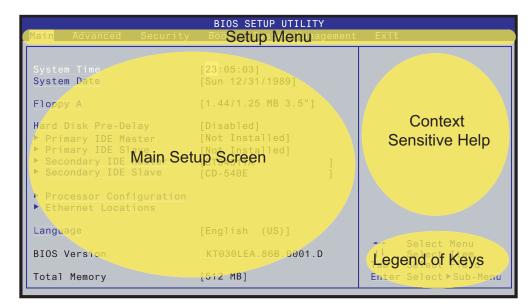

#### Figure 3. Ethernet BIOS Setup

The "Ethernet" topic in Section 14 contains links to the data sheets for the Intel 82546 Gigabit Ethernet device used onboard the CPC5505. Connector locations and pinouts are documented in Section 8, "Connectors."

# **LED Indicators**

The LEDs located on the faceplate are defined below. See the topic "Programming the LEDs" in Section 2 for software code used to program the user-defined LEDs.

#### Power/Reset

- Green = out of reset, power enabled

- Amber = active reset, power enabled

- Off = Power disabled

#### IDE disk activity (primary or secondary)

- Green = active

- Off = inactive

#### User-defined LEDs—one may be defined as clock throttle

- Green = user defined

- Amber = user defined

- Off = user defined

#### Ethernet A, Ethernet B RJ-45 LEDs, one per channel

- Flashing green = activity

- Green = Link

- Off = 10 Mbps

- Green = 100 Mbps

- Amber = 1000 Mbps

#### Hot Swap

- Blue = safe to extract board

- Off = not safe to extract board

#### Status/Health

- Green = healthy

- Amber = needs service

# **Rear-Panel I/O**

The CPC5505 transitions the following I/O signals through CompactPCI connector J5 to an RPIO board such as the IPnexus ZT 4807e Rear-Panel Transition Board:

- Floppy

- Two serial ports (COM1 and COM2)

- Keyboard

- EIDE (ATA-2) secondary channel

- PS/2 mouse

Ethernet LED

- Video

Local CPU SMBus

- NMI / PBRST / RPIO\_PRESENT / PWRGD signals

In addition, the CPC5505 transitions Ethernet A and B through CompactPCI connector J3.

See Section 8, "Connectors," for more information on the connectors present on the CPC5505.

# 1.4 Software

# BIOS

The Performance Technologies Embedded BIOS (AMI core) is loaded in flash on board the CPC5505. The BIOS is user-configurable to boot an operating system from one of the following locations:

- Local flash memory

- Hard drive

- CD-ROM/DVD-ROM drive

- Floppy drive

- Network source

# **Operating Systems**

The CPC5505 is compatible with all major PC operating systems. Performance Technologies provides additional operating system support when the CPC5505 is purchased in conjunction with an IPnexus development system. This support may include additional drivers for Performance Technologies products such as peripherals and flash drives. Software device drivers for the CPC5505 can be found on the Performance Technologies Web site.

- USB channels 1 and 2

- RPIO Eject

- Power/Ground

- Speaker

The following operating systems are supported:

- Microsoft<sup>®</sup> Windows<sup>®</sup> 2000

- Industry standard version of Linux<sup>®</sup>

- Comprehensive board support package (BSP) for VxWorks<sup>®</sup>. The CompactPCI VxWorks-5.4 BSP streamlines the implementation of VxWorks on the CPC5505. The VxWorks development system must be purchased directly from WindRiver.

Refer to the Performance Technologies Web site for a complete list of compatible operating systems.

## IPMI

For more information about how to program software to interact with the IPMI firmware, refer to the *Intelligent Platform Management Interface v1.5 Specification* and the *Intelligent Platform Management Interface Implementer's Guide*.

## **Hot Swap**

Hot swap refers to the dynamic insertion and removal of devices in a computer system without halting the system.

When used in a hot swap compliant backplane and in accordance with the *CompactPCI Hot Swap Specification, PICMG 2.1, Version 2.0*, the CPC5505 supports hosting hot swap peripherals in a powered system. Section 14, "Data Sheet Reference," contains a link to the CompactPCI Hot Swap Specification.

The Performance Technologies Hot Swap Kit provides software that collaborates with the operating system to provide hot swap support for CompactPCI. Operating systems supported include Windows 2000, VxWorks, and Linux. For more information about the Hot Swap Kit, refer to the *Performance Technologies Hot Swap Kit Software Manual*.

# Section

# **Getting Started**

This section summarizes the information you need to make the CPC5505 operational. Please read it before attempting to use the board.

# 2.1 Unpacking

Check the shipping carton for damage. If the shipping carton and contents are damaged, notify the carrier and Performance Technologies for an insurance settlement. Retain the shipping carton and packing material for inspection by the carrier. Obtain authorization before returning any product to Performance Technologies. Refer to Section 15 for assistance information.

**Warning:** Like all equipment that uses MOS devices, the CPC5505 must be protected from static discharge. Never remove any of the socketed parts except at a static-free workstation. Use the anti-static bag shipped with your order when handling the board.

# 2.2 CPC5505 System Requirements

The following CPC5505 system requirements are briefly described below:

- Backplane connectivity

- Electrical and environmental requirements

## **Backplane Connectivity**

The CPC5505 can be installed as a System Master in the System Slot or as a stand-alone computer in a peripheral slot. Refer to the "Drone Mode" topic for more information on using the CPC5505 as a stand-alone computer.

The CPC5505 is designed for use in a CompactPCI Packet Switching Backplane (compliant with the CompactPCI Specification, PICMG 2.16, Version 1.0). This requires that the backplane provide a CompactPCI bus on connectors J1 and J2 and Ethernet pins on J3. To support optional rear-panel transition (RPIO) boards, the backplane's RPIO connector (J5) must be available and have through pins to the CPC5505's J5 connector.

The CPC5505 supports universal voltage: it operates in both 3.3V V(I/O) and 5V V(I/O) slots.

See Section 8, "Connectors," for complete connector locations, descriptions, and pinout tables.

## **Electrical and Environmental Requirements**

The CPC5505 with a 1.8 GHz processor loaded requires a maximum of +5 VDC +5%, -3% @ 2.9 A, +3.3 VDC +5%, -3% @ 9.5 A, and +12 VDC ± 5%, -3% @ 10 mA. Electrical specifications are presented in more detail in Section 9.

The CPC5505 is supplied with a heat sink that allows the processor to operate between 0° and approximately 50°C ambient with a minimum of 250 LFM (1.27 meters per second) of external airflow. It is the user's responsibility to ensure that the CPC5505 is installed in a chassis capable of supplying adequate airflow. The maximum power dissipation of the processor is 24W. External airflow **must** be provided at all times. See Section 9, "Specifications," and Section 12, "Thermal Considerations," for more details.

**Warning:** Operating the CPC5505 without adequate airflow will damage the processor.

The CPC5505 may contain materials that require regulation upon disposal. Please dispose of this product in accordance with local rules and regulations. For disposal or recycling information, please contact your local authorities or the Electronic Industries Alliance at http://www.eiae.org/.

# 2.3 Memory Configuration

The CPC5505 can *address* up to 4 GB of memory that is allocated between system memory and PCI devices. Two SO-DIMM sockets provide up to 2 GB of DDR system memory. The memory address space is divided between memory local to the board (system memory) and memory located on the two PCI buses. Any memory not reserved or occupied by a local memory device (DDR or flash) is available to the onboard PMC site or to devices on the CompactPCI bus.

The CPC5505 is optionally populated with PC2700 ECC DDR SDRAM located on two registered, 200-pin SDRAM DIMM sockets (J14, J15). The socket supports 256 MB, 512MB or 1 GB memory modules, giving a memory size range from a minimum of 256 MB to a maximum of 2 GB of 333 MHz DDR (PC2700) memory.

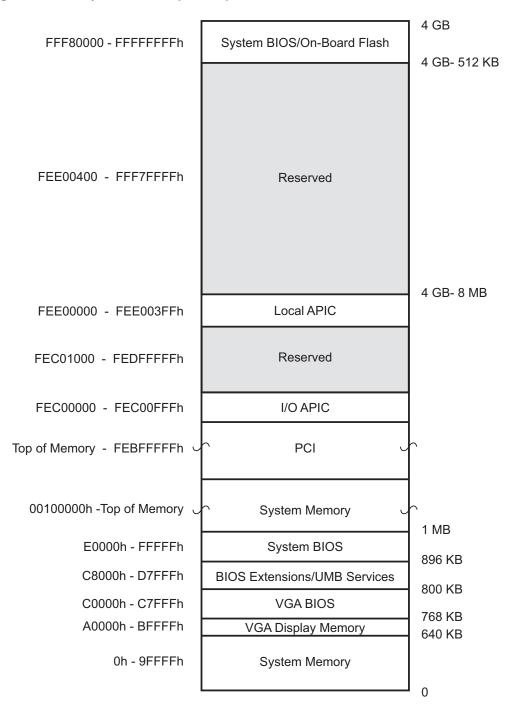

The "Memory Address Map Example" illustration shows an example of memory addressing for the CPC5505.

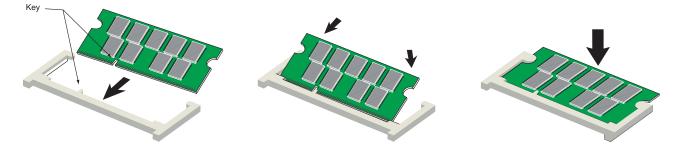

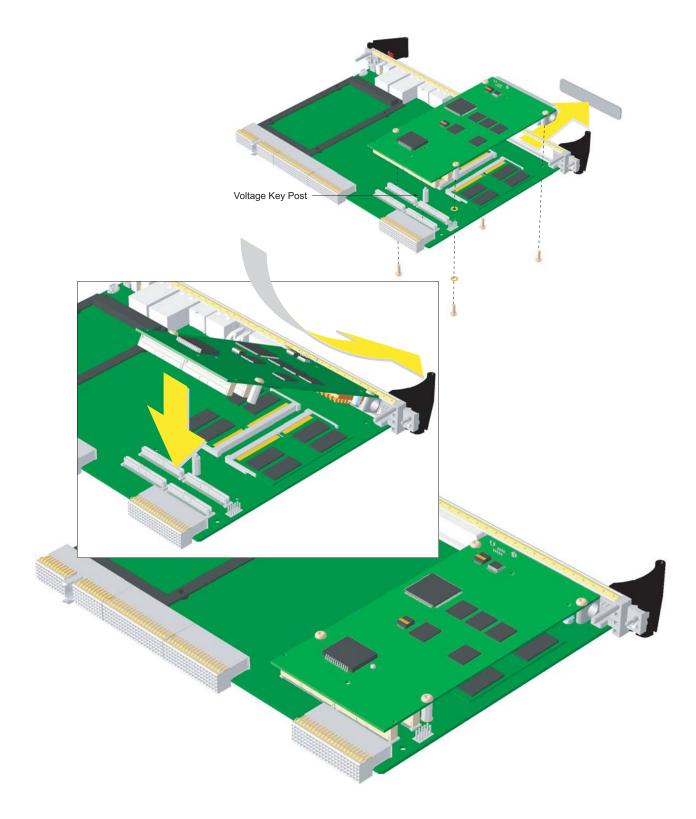

## **Installing Memory**

Performance Technologies recommends installing only memory validated for the CPC5505.

- 1. Locate DIMM sockets J14 and 15. See the Connector Locations figure in Section 8.

- 2. The DIMM sockets are reversed, mirror images of each other, with their registration keys both located toward the backplane connectors. One memory module is installed reversed from the other.

- 3. Insert the memory module so its registration notch aligns with the key in the desired memory socket and its edge connector slides into the socket connector.

- 4. Press the memory module down until the latches click into place and retain the module.

- 5. Once installed correctly, the memory module appears as it does at the right of the "Memory Module Orientation" figure.

Figure 4. Memory Module Orientation

# 2.4 I/O Configuration

The CPC5505 addresses up to 64 KB of I/O using a 16-bit I/O address. The address space is divided between I/O local to the board and I/O on the CompactPCI bus. Any I/O space not occupied by a local I/O device is available for the CompactPCI bus.

The CPC5505 is populated with many of the most commonly used I/O peripheral devices for industrial control and computing applications. The I/O address location for each of the peripherals is shown in the "I/O Address Map" illustration.

#### Figure 5. Memory Address Map Example

#### Figure 6. I/O Address Map

| -                                                    |                                           |  |

|------------------------------------------------------|-------------------------------------------|--|

| CF9h                                                 | Reset Generator                           |  |

| CA3h                                                 | IPMI Command Status                       |  |

| CA2h IPMI KCS Data                                   |                                           |  |

| 800h                                                 | SB Power Management Base<br>SIO GPIO Base |  |

| 5A0h<br>560h                                         | SIO GPIO Base<br>SIO XBus Base            |  |

| 560h                                                 | SIO PM Base                               |  |

| 540h                                                 | SIO SWC Base                              |  |

| 4D0 - 4D1h                                           | Interrupt Controller                      |  |

| 4D0 - 4D1h Interrupt Controller<br>480h SB GPIO Base |                                           |  |

| 400h                                                 | SB SMB Base                               |  |

| 3F6h Primary IDE Registers                           |                                           |  |

| 388 - 38Bh                                           | AdLib                                     |  |

| 376h                                                 | Secondary IDE Registers                   |  |

| 208 - 20Fh                                           | Gameport High                             |  |

| 200 - 207h                                           | Gameport Low                              |  |

| 1F0 - 1F7h                                           | Primary IDE Registers                     |  |

| 170h - 177h                                          | Secondary IDE Registers                   |  |

| F0h                                                  | Coprocessor                               |  |

| E9 – Efh                                             | Reserved                                  |  |

| E1-E8h                                               | CPC5505 System Registers                  |  |

| C0 – DFh                                             | On-board Slave DMA Controller             |  |

| B4 - BDh                                             | Interrupt Controller                      |  |

| B2 - B3h                                             | Power Management                          |  |

| A4 - B1h Interrupt Controller                        |                                           |  |

| A0 - A1h                                             | On-board Slave Interrupt Controller       |  |

| 93 – 9Fh DMA Controller                              |                                           |  |

| 92h                                                  | Fast Gate A20/Reset Control               |  |

| 81 - 8Fh                                             | On-board DMA Page Registers               |  |

| 78 - 80h                                             | CPC5505 System Registers                  |  |

| 70 - 77h                                             | NMI Enable/RTC Controller                 |  |

| 67h                                                  | NMI Controller                            |  |

| 66h                                                  | Reserved                                  |  |

| 65h<br>64h                                           | NMI Controller<br>PS/2 Keyboard/Mouse     |  |

| 63h                                                  | NMI Controller                            |  |

| 62h                                                  | Reserved                                  |  |

| 61h                                                  | NMI Status Register                       |  |

| 60h                                                  | PS/2 Keyboard/Mouse                       |  |

| 50 - 53h                                             | On-board Timer/Counters                   |  |

| 4Fh                                                  | SIO IO Data (Write Only)                  |  |

| 4Eh SIO IO Index (Write Only)                        |                                           |  |

| 40 - 43h                                             | On-board Timer/Counters                   |  |

| 30 - 3Dh                                             | On-board Master Interrupt Controller      |  |

| 2Fh                                                  | IPMC IO Data                              |  |

| 2Eh                                                  | IPMC IO Index                             |  |

| 24 - 2Dh                                             | Interrupt Controller                      |  |

| 20 - 21h                                             | On-board Master Interrupt Controller      |  |

| 0 - 1Fh                                              | On-board Master DMA Controller            |  |

|                                                      |                                           |  |

# **Analog Video Interface**

The CPC5505 provides access to video at the faceplate through J11 or through the rearpanel I/O connector J5, using integrated graphics support from the Intel 855GME. Video connector J11 is a standard 15-pin D shell connector. See Section 8, "Connectors," for connector locations and pinout information.

A small portion of the system RAM is devoted to the 855GME video memory. The 855GME can be set to consume between 4 MB and 32 MB of system RAM for video memory (see the table "Shared Video RAM"). In most cases it is best to let the Performance Technologies Embedded BIOS set the video memory size (select the default, "automatic," in the BIOS setup menu). Setting the video memory size to less than 1.5625% of the total system memory results in areas of uncached system memory, which significantly impacts overall system performance.

| System RAM | Video Memory |

|------------|--------------|

| 2 GB       | 32 MB        |

| 1 GB       | 16 MB        |

| 512 MB     | 8 MB         |

| 256 MB     | 4 MB         |

#### Table 2. Shared Video RAM