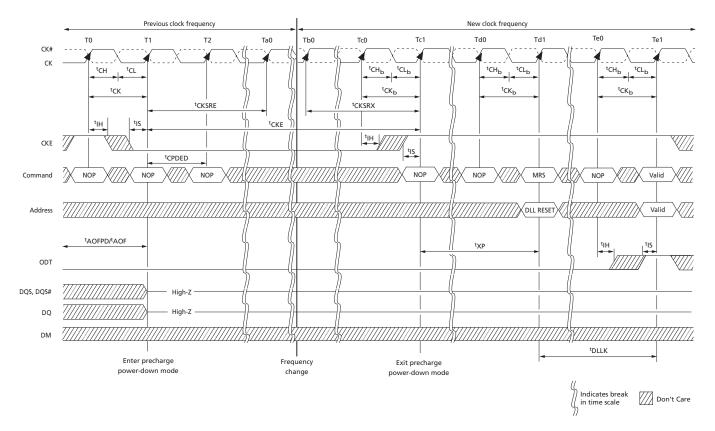

## Figure 46: Change Frequency During Precharge Power-Down

- Notes: 1. Applicable for both SLOW-EXIT and FAST-EXIT precharge power-down modes.

- 2. <sup>t</sup>AOFPD and <sup>t</sup>AOF must be satisfied and outputs High-Z prior to T1 (see On-Die Termination (ODT) (page 193) for exact requirements).

- 3. If the R<sub>TT,nom</sub> feature was enabled in the mode register prior to entering precharge power-down mode, the ODT signal must be continuously registered LOW, ensuring R<sub>TT</sub> is in an off state. If the R<sub>TT,nom</sub> feature was disabled in the mode register prior to entering precharge power-down mode, R<sub>TT</sub> will remain in the off state. The ODT signal can be registered LOW or HIGH in this case.

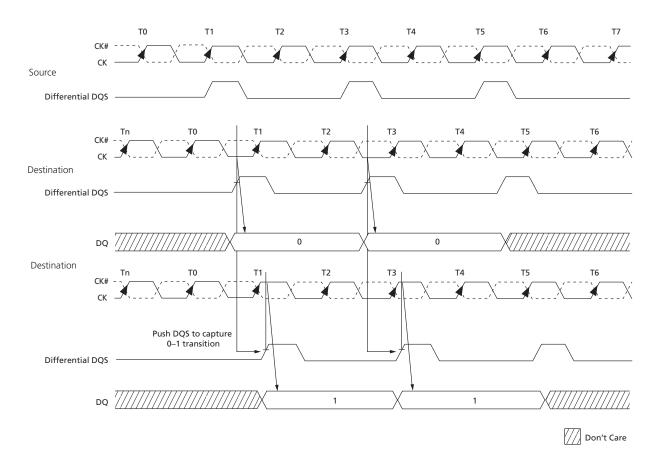

## Write Leveling

For better signal integrity, DDR3 SDRAM memory modules have adopted fly-by topology for the commands, addresses, control signals, and clocks. Write leveling is a scheme for the memory controller to adjust or de-skew the DQS strobe (DQS, DQS#) to CK relationship at the DRAM with a simple feedback feature provided by the DRAM. Write leveling is generally used as part of the initialization process, if required. For normal DRAM operation, this feature must be disabled. This is the only DRAM operation where the DQS functions as an input (to capture the incoming clock) and the DQ function as outputs (to report the state of the clock). Note that nonstandard ODT schemes are required.

The memory controller using the write leveling procedure must have adjustable delay settings on its DQS strobe to align the rising edge of DQS to the clock at the DRAM pins. This is accomplished when the DRAM asynchronously feeds back the CK status via the DQ bus and samples with the rising edge of DQS. The controller repeatedly delays the DQS strobe until a CK transition from 0 to 1 is detected. The DQS delay established by this procedure helps ensure 'DQSS, 'DSS, and 'DSH specifications in systems that use fly-by topology by de-skewing the trace length mismatch. A conceptual timing of this procedure is shown in Figure 47.

## **Figure 47: Write Leveling Concept**