Publication # 54267 Revision: 1.00 Issue Date: January 2014

Advanced Micro Devices 🛛 🟹

#### © 2014 Advanced Micro Devices, Inc. All rights reserved.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Microsoft and Windows, are registered trademarks of Microsoft Corporation.

PCIe is a registered trademark of PCI-Special Interest Group (PCI-SIG).

Dolby Laboratories, Inc. Manufactured under license from Dolby Laboratories.

Rovi Corporation

This device is protected by U.S. patents and other intellectual property rights. The use of Rovi Corporation's copy protection technology in the device must be authorized by Rovi Corporation and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Rovi Corporation.

Reverse engineering or disassembly is prohibited.

USE OF THIS PRODUCT IN ANY MANNER THAT COMPLIES WITH THE MPEG ACTUAL OR DE FACTO VIDEO AND/OR AUDIO STANDARDS IS EXPRESSLY PROHIBITED WITHOUT ALL NECESSARY LICENSES UNDER APPLICABLE PATENTS. SUCH LICENSES MAY BE ACQUIRED FROM VARIOUS THIRD PARTIES INCLUDING, BUT NOT LIMITED TO, IN THE MPEG PATENT PORTFOLIO, WHICH LICENSE IS AVAILABLE FROM MPEG LA, L.L.C., 6312 S. FIDDLERS GREEN CIRCLE, SUITE 400E, GREENWOOD VILLAGE, COLORADO 80111.

AMD Platform Security Processor BIOS Architectural Design Guide

## Contents

| Revision | Revision History                                                            |    |  |  |

|----------|-----------------------------------------------------------------------------|----|--|--|

| Chapter  | 1 Introduction                                                              | 12 |  |  |

| 1.1      | Scope of This Document                                                      | 12 |  |  |

| 1.1.     | 1 PSP Overview                                                              | 12 |  |  |

| 1.1.2    | 2 Key Features of the PSP                                                   | 12 |  |  |

| Chapter  | 2 Overview of Feature Implementation                                        | 13 |  |  |

| 2.1      | Hardware Validated Boot                                                     | 13 |  |  |

| 2.1.     | 1 Integrated TPM Functions                                                  | 14 |  |  |

| 2.1.2    | 2 Cryptographic Acceleration Support                                        | 15 |  |  |

| Chapter  | 3 PSP Components                                                            | 16 |  |  |

| 3.1      | On-chip PSP Boot ROM                                                        | 16 |  |  |

| 3.2      | Off-chip PSP Boot Loader                                                    | 16 |  |  |

| 3.3      | Off-chip PSP Secure OS                                                      | 17 |  |  |

| Chapter  | 4 Overview of BIOS Support for PSP                                          | 19 |  |  |

| 4.1      | SPI Flash Region Layout                                                     | 19 |  |  |

| 4.1.     | 1 PSP Directory Table                                                       | 19 |  |  |

| 4.1.2    | 2 Crisis Recovery Path with PSP Enabled                                     | 23 |  |  |

| 4.2      | Signing of BIOS Component- OEM Signing Key, PEI Volume                      | 28 |  |  |

| 4.3      | BIOS Build Process                                                          | 29 |  |  |

| 4.3.     | 1 Hardware validated Boot BIOS development bypass mechanism (Mullins Only). | 31 |  |  |

| 4.4      | Runtime Execution Flow                                                      | 32 |  |  |

| 4.4.     | 1 5.4.1 Pre x86 Initialization                                              | 32 |  |  |

| 4.4.2    | 2 BIOS Boot x86 Initialization                                              | 33 |  |  |

| 4.4.     | 3 BIOS Runtime Functionality                                                | 34 |  |  |

| Chapter  | 5 BIOS S3-Resume Path Handling                                              | 36 |  |  |

| 5.1      | BIOS S3 Transition Flow on ACPI Aware OS                                    | 36 |  |  |

| 5.2      | BIOS S3 Resume                                                              | 36 |  |  |

| 5.2.     | 1 Custom Resume Path                                                        | 37 |  |  |

| 5.2.     | 2 Separate Firmware Volume for Resume Code                                  | 37 |  |  |

| 5.2.     | 3 SMM Resume                                                                | 37 |  |  |

|         | AMD Platform Security Processor BIOS54267Rev. 1.00January 2014Architectural Design Guide54267Rev. 1.00January 2014 |                                                                  |    |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----|--|--|

| 5.2.    | 4                                                                                                                  | Modified Conventional Resume                                     |    |  |  |

| Chapter | · 6                                                                                                                | TPM Software Interface                                           | 39 |  |  |

| 6.1     | TPI                                                                                                                | M 2.0 Command/Response Buffer Interface                          | 39 |  |  |

| 6.2     | AM                                                                                                                 | ID Implementation of TPM 2.0 Interface                           | 40 |  |  |

| Chapter | • 7                                                                                                                | BIOS PSP Mailbox interaction                                     | 42 |  |  |

| 7.1     | BIC                                                                                                                | OS to PSP Mailbox Commands                                       |    |  |  |

| 7.1.    | 1                                                                                                                  | MboxBiosCmdDramInfo (MboxCmd = 0x01)                             |    |  |  |

| 7.1.    | 2                                                                                                                  | MboxBiosCmdSmmInfo (MboxCmd = 0x02)                              |    |  |  |

| 7.1.    | 3                                                                                                                  | MboxBiosCmdSxInfo (MboxCmd = 0x03)                               | 47 |  |  |

| 7.1.    | 4                                                                                                                  | MboxBiosCmdRsmInfo (MboxCmd = 0x04)                              | 47 |  |  |

| 7.1.    | 5                                                                                                                  | $MboxBiosCmdPspQuery (MboxCmd = 0x05) \dots$                     |    |  |  |

| 7.1.    | 6                                                                                                                  | MboxBiosCmdBootDone (MboxCmd = 0x06)                             |    |  |  |

| 7.1.    | 7                                                                                                                  | MboxBiosCmdClearS3Sts (MboxCmd = 0x07)                           | 49 |  |  |

| 7.1.    | 8                                                                                                                  | MboxBiosS3DataInfo (MboxCmd = 0x08)                              | 49 |  |  |

| 7.1.    | 9                                                                                                                  | MBOX_S3DATA_BUFFER;MboxBiosCmdNop (MboxCmd = 0x09)               | 49 |  |  |

| 7.2     | PSF                                                                                                                | P to BIOS Mailbox Commands                                       | 49 |  |  |

| 7.2.    | 1                                                                                                                  | MboxPspCmdSpiGetAttrib (MboxCmd = 0x081)                         | 50 |  |  |

| 7.2.    | 2                                                                                                                  | MboxPspCmdSpiSetAttrib (MboxCmd = 0x082)                         | 51 |  |  |

| 7.2.    | 3                                                                                                                  | MboxPspCmdSpiGetBlockSize (MboxCmd = 0x083)                      |    |  |  |

| 7.2.    | 4                                                                                                                  | MboxPspCmdSpiReadFV (MboxCmd = 0x084)                            | 51 |  |  |

| 7.2.    | 5                                                                                                                  | MboxPspCmdSpiWriteFV (MboxCmd = 0x085)                           | 52 |  |  |

| 7.2.    | 6                                                                                                                  | MboxPspCmdSpiEraseFV (MboxCmd = 0x086)                           | 52 |  |  |

| Chapter | 8                                                                                                                  | Platform BIOS Requirements for PSP Implementation                | 53 |  |  |

| Chapter | · 9                                                                                                                | Standards                                                        | 57 |  |  |

| 9.1     | UE                                                                                                                 | FI 2.3.1c Chapter 27 Secure Boot                                 | 57 |  |  |

| 9.2     | Mic                                                                                                                | crosoft <sup>®</sup> Trusted Execution Environment UEFI Protocol | 57 |  |  |

| 9.3     | Mic                                                                                                                | crosoft <sup>®</sup> Trusted Execution Environment ACPI Profile  | 57 |  |  |

| 9.4     | AM                                                                                                                 | ID PSP 1.0 Software Architecture Design Document                 |    |  |  |

| Appendi | ix A                                                                                                               | PSP Directory Structure                                          | 58 |  |  |

| Appendi | ix B                                                                                                               | PSP –BIOS Mailbox                                                | 60 |  |  |

| Appendi | ix C                                                                                                               | PSP S5 Boot Flow                                                 | 67 |  |  |

AMD Platform Security Processor BIOS Architectural Design Guide

| Appendi | x D  | PSP S3/Resume                                                           | .69 |

|---------|------|-------------------------------------------------------------------------|-----|

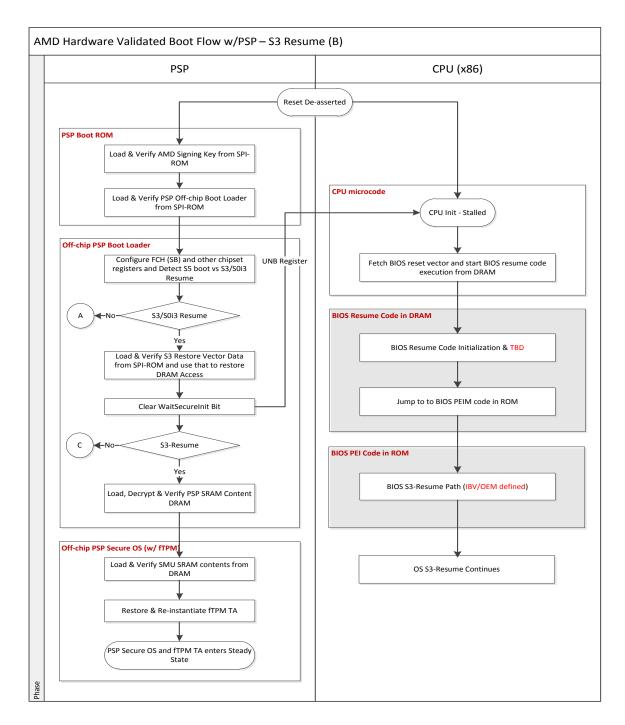

| D.1     | PSP  | S3 Resume Flow                                                          | .70 |

| Appendi | хE   | Key format                                                              | .71 |

| E.1     | Publ | lic Part of the AMD Signing RSA-2048 bit Key                            | .71 |

| E.2     | Cert | ified Public Part of the Leaf/Intermediate RSA-2048 or RSA 4096-bit Key | .72 |

| Appendi | x F  | BuildPspDirectory Tool                                                  | .74 |

| F.1     | PSP  | Directory Configure File Format                                         | .74 |

| F.2     | Con  | nmand Line Parameters                                                   | .74 |

| F.2.    | 1    | Build Directory Table (bd)                                              | .74 |

| F.2.2   | 2    | Build PSP BIOS Image (bb)                                               | .75 |

| F.2.    | 3    | Dump PSP Directory Information (dp)                                     | .75 |

| Appendi | x G  | PSP FW FW_STATUS                                                        | .76 |

###

AMD Platform Security Processor BIOS Architectural Design Guide 54267 Rev. 1.00 January 2014

# **List of Figures**

| Figure 1. Hardware Validated Boot Overview            | . 13 |

|-------------------------------------------------------|------|

| Figure 2. PSP Directory Table                         | . 20 |

| Figure 3. Crisis Recovery Flow With PSP               | . 27 |

| Figure 4. Final SPI Image                             | . 30 |

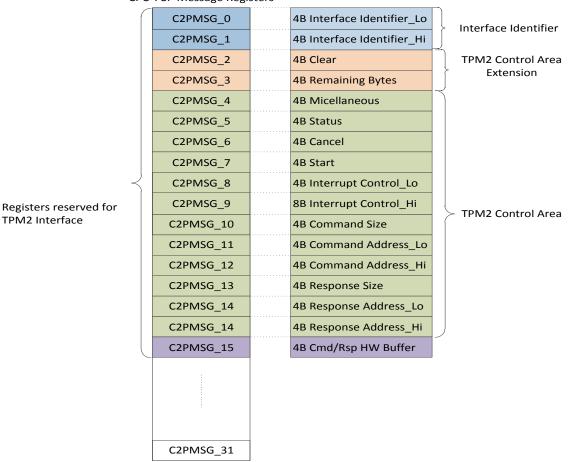

| Figure 5. TPM2 Command/Response Buffer Interface      | . 40 |

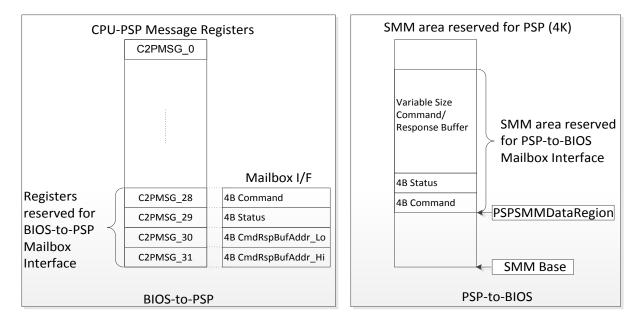

| Figure 6. BIOS-PSP Mailbox Interface                  | . 42 |

| Figure 7. BIOS-PSP Mailbox Command Execution Sequence | . 43 |

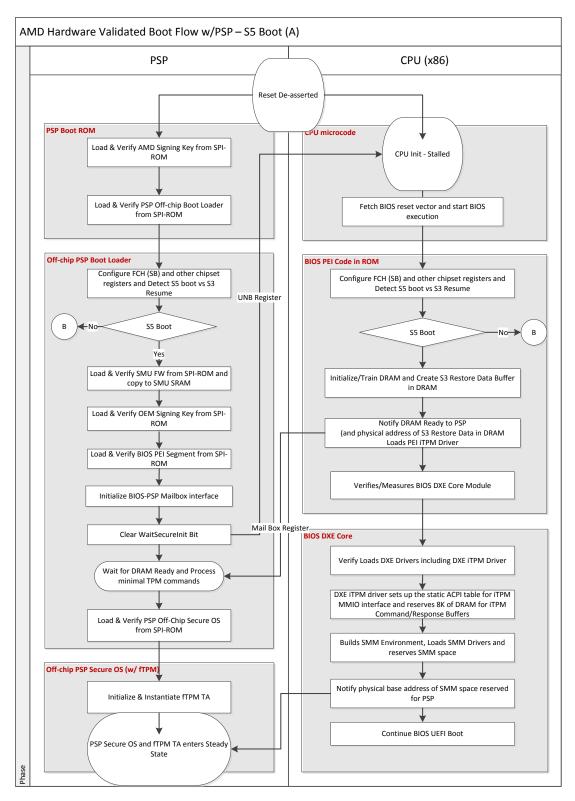

| Figure 8. Hardware Validated Boot Flow – S5 Boot      | . 68 |

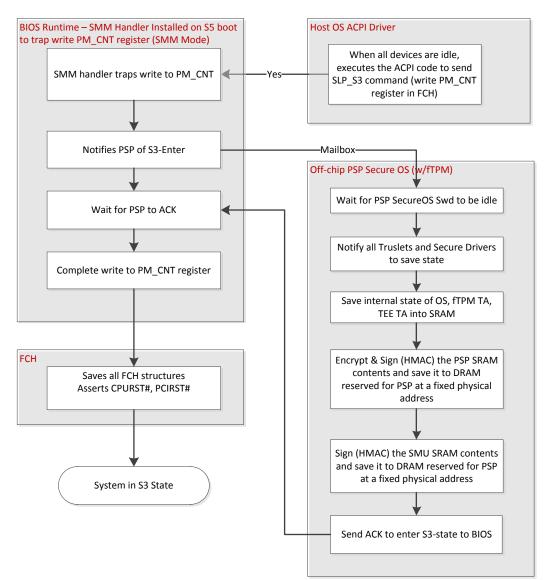

| Figure 9. Hardware Validated Boot Flow – S3 Suspend   | . 69 |

| Figure 10. Hardware Validated Boot Flow – S3 Resume   | . 70 |

| Figure 11. Root RSA Public Key Token Format           | . 71 |

| Figure 12. RSA Public Key Token Format                | . 72 |

AMD Platform Security Processor BIOS Architectural Design Guide

# List of Tables

| Fable 1. Definitions, Acronyms and Abbreviations         | 9  |

|----------------------------------------------------------|----|

| Fable 2. Embedded Firmware Signature Target Locations    | 20 |

| Fable 3. PSP Directory Table Header Structure            | 21 |

| Fable 4. PSP Directory Table Entry Fields                | 21 |

| Fable 5. PSP Directory Entry Type Encodings              | 21 |

| Гable 6. PSP Soft Fuse Chain 1                           | 22 |

| Fable 7. PSP Soft Fuse Chain Bit Assignment              | 22 |

| Гable 8. PSP Entry SPI ROM Property Assignment           | 24 |

| Гable 9. Control Area Layout                             | 39 |

| Fable 10. BIOS-PSP Mailbox Status Register Bit Fields    | 44 |

| Fable 11. BIOS-to-PSP Mailbox Commands                   | 44 |

| Fable 12. PSP-to-BIOS Mailbox Commands                   | 45 |

| Fable 13. RSA Key Format Fields                          | 73 |

| Fable 14. PSP BootLoader Error Codes                     | 76 |

| Fable 15. PSP BootLoader Progress Codes                  | 77 |

| Table 16. Progress Codes during Secure OS Initialization | 79 |

| Table 17. Progress Codes during S3 Cycle                 | 79 |

54267 Rev. 1.00 January 2014

# **Revision History**

| Date         | Revision | Description          |  |

|--------------|----------|----------------------|--|

| January 2014 | 1.00     | Initial NDA release. |  |

AMD Platform Security Processor BIOS Architectural Design Guide

# Definitions

| Term  | Definition                                        | Comments                                                                                                                                                                                                                                                    |

|-------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AES   | Advanced Encryption Standard                      |                                                                                                                                                                                                                                                             |

| AGESA | AMD Generic Encapsulated Software<br>Architecture | AMD software stack to initialize Si                                                                                                                                                                                                                         |

| AP    | Application Processor                             | Secondary core in a multi-core cluster                                                                                                                                                                                                                      |

| ССР   | Cryptographic Co-Processor                        |                                                                                                                                                                                                                                                             |

| CRTM  | Core Root of Trust for Measurement                |                                                                                                                                                                                                                                                             |

| DMA   | Direct Memory Access                              |                                                                                                                                                                                                                                                             |

| DRAM  | Dynamic Random Access Memory                      |                                                                                                                                                                                                                                                             |

| DXE   | Driver Execution Environment                      | Driver Execution Environment phase, that<br>run after memory has been initialized                                                                                                                                                                           |

| ECC   | Elliptic Curve Cryptography                       |                                                                                                                                                                                                                                                             |

| EFI   | Extensible Firmware Interface                     |                                                                                                                                                                                                                                                             |

| FFS   | Firmware File System                              | A binary storage format that is well suited<br>to firmware volumes. The abstracted model<br>of the FFS is a flat file system                                                                                                                                |

| fTPM  | Firmware TPM                                      | same as iTPM                                                                                                                                                                                                                                                |

| FV    | Firmware Volume                                   | A FV is a simple Flash File System that<br>starts with a header and contains files that<br>are named by a GUID. The file system is<br>flat and does not support directories. Each<br>file is made up of a series of sections that<br>support encapsulation. |

| FW    | Firmware                                          |                                                                                                                                                                                                                                                             |

| НОВ   | Hand-Off Block                                    | A structure used to pass information from<br>one boot phase to another (i.e., from the PEI<br>phase to the DXE phase)                                                                                                                                       |

| HMAC  | keyed-hash message authentication code            | In cryptography, a keyed-hash message<br>authentication code (HMAC) is a specific<br>construction for calculating a message<br>authentication code (MAC) involving a<br>cryptographic hash function in combination<br>with a secret cryptographic key       |

#### Table 1. Definitions, Acronyms and Abbreviations

54267 Rev. 1.00 January 2014

| Term | Definition                                 | Comments                                                                                                                                                                                                                                                                   |

|------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSM  | Hardware Security Module                   | A hardware security module (HSM) is a<br>physical computing device that safeguards<br>and manages digital keys for strong<br>authentication and provides<br>cryptoprocessing without revealing keying<br>material                                                          |

| IBV  | Independent BIOS Vendor                    |                                                                                                                                                                                                                                                                            |

| iTPM | Integrated TPM                             | Firmware TPM                                                                                                                                                                                                                                                               |

| ML   | Mullins                                    | Code name used for the AMD Family 16h<br>Models 30h-3Fh Processor, otherwise<br>known as the AMD FT3b processor or the<br>AMD FP4 processor.                                                                                                                               |

| MTM  | Mobile Trusted Module                      | A firmware version of a TPM                                                                                                                                                                                                                                                |

| OEM  | Original Equipment Manufacturer            |                                                                                                                                                                                                                                                                            |

| OS   | Operating System                           |                                                                                                                                                                                                                                                                            |

| PEI  | Pre-EFI Initialization                     | Set of drivers usually designed to initialize<br>memory and the CPU so that DXE phase<br>can run.                                                                                                                                                                          |

| PKCS | Public Key Cryptography Standards          |                                                                                                                                                                                                                                                                            |

| PSP  | Platform Security Processor                |                                                                                                                                                                                                                                                                            |

| RNG  | Random Number Generator                    |                                                                                                                                                                                                                                                                            |

| ROM  | Read Only Memory                           |                                                                                                                                                                                                                                                                            |

| RoT  | Root of Trust                              |                                                                                                                                                                                                                                                                            |

| RSA  | Rivest-Shamire-Adleman encrypton algorithm |                                                                                                                                                                                                                                                                            |

| RTM  | Root of trust for measurement              |                                                                                                                                                                                                                                                                            |

| SEC  | Security Phase                             | Initial starting point for boot process, first<br>code executed after hardware reset.<br>Responsible for 1) Establishing root trust in<br>the software space; 2) Initializing<br>architecture specific configuration to<br>establish memory space for the C code<br>stack. |

| SHA  | Secure Hash Algorithm                      |                                                                                                                                                                                                                                                                            |

#### Table 1. Definitions, Acronyms and Abbreviations (Continued)

AMD Platform Security Processor BIOS Architectural Design Guide

| Term | Definition                       | Comments                                                                                                                                                                                                                                                                                      |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMM  | System Management Mode           | An operating mode in which all normal<br>execution (including the operating system)<br>is suspended, and special separate software<br>(usually firmware or a hardware-assisted<br>debugger) is executed in high-privilege<br>mode.                                                            |

| SPI  | Serial Peripheral Interface Bus. | Also referred to as the Non-volatile ROM chip on this Bus                                                                                                                                                                                                                                     |

| SRAM | Static Random Access Memory      |                                                                                                                                                                                                                                                                                               |

| TCG  | Trusted Computing Group          | A standards organization                                                                                                                                                                                                                                                                      |

| TEE  | Trusted Execution Environment    | TrustZone is one example of a technology that establishes a TEE                                                                                                                                                                                                                               |

| TPM  | Trusted Platform Module          | A hardware root of trust                                                                                                                                                                                                                                                                      |

|      | AMD Signing Key                  | A 2048 bit RSA key pair generated by<br>AMD. The private key is used to sign the<br>public portion of OEM signing key.                                                                                                                                                                        |

|      | OEM Signing Key                  | An asymmetric key pair generated by<br>OEMs. The private key is used to sign the<br>RTM volume of BIOS. The public portion<br>of signed OEM key is stored in the SPI<br>BIOS image                                                                                                            |

|      | PSP Directory                    | A simple directory at certain SPI location<br>that lists various firmware images and<br>respective location in the SPI space                                                                                                                                                                  |

|      | BIOS RTM Volume                  | BIOS firmware Volume that is root of trust<br>of x86 BIOS execution. The code in this<br>volume is executed at x86reset. Based on<br>OEM implementation this can be SEC<br>volume or combined SEC-PEI volume. PSP<br>firmware authenticates BIOS RTM volume<br>before releasing the x86 core. |

#### Table 1. Definitions, Acronyms and Abbreviations (Continued)

# Chapter 1 Introduction

## **1.1 Scope of This Document**

This document's primary focus is to cover BIOS requirements and to suggest implementation guidelines. This document does not cover the details of the Platform Security Processor (PSP) firmware and PSP functionality. This document covers only the services and interfaces that BIOS provides to PSP firmware. The document also assumes that the platform BIOS will run on x86 CPU core under an ACPI-aware operating system and that BIOS uses SPI ROM storage.

#### **1.1.1 PSP Overview**

The PSP is an integrated hardware security subsystem that runs independently from the main cores of the platform. It provides various security features as listed in the following subsections. PSP executes its own firmware and shares the SPI flash storage that BIOS uses.

#### 1.1.2 Key Features of the PSP

#### 1.1.2.1 Hardware Validated Boot

- The PSP validates the signature of the initial BIOS Boot code prior to starting BIOS boot. PSP is the Core Root of Trust for Measurement (CRTM) and the x86 cores are only released from reset if the BIOS image is authentic.

- Only validated BIOS is allowed to boot.

- The initial block of BIOS code is responsible for subsequently validating the signatures of all other BIOS code blocks loaded from the system read only memory (ROM).

#### 1.1.2.2 Integrated Trusted Platform Module (TPM) Functions

Implements the TPM 2.0 functions required (for some categories of systems) by Microsoft<sup>®</sup> Windows<sup>®</sup> 8.

#### 1.1.2.3 Cryptographic Acceleration Support

Provides hardware acceleration of cryptographic algorithms for PSP FW and x86 software. Also provides true random number generator (RNG) support.

AMD Platform Security Processor BIOS Architectural Design Guide

# Chapter 2 Overview of Feature Implementation

# 2.1 Hardware Validated Boot

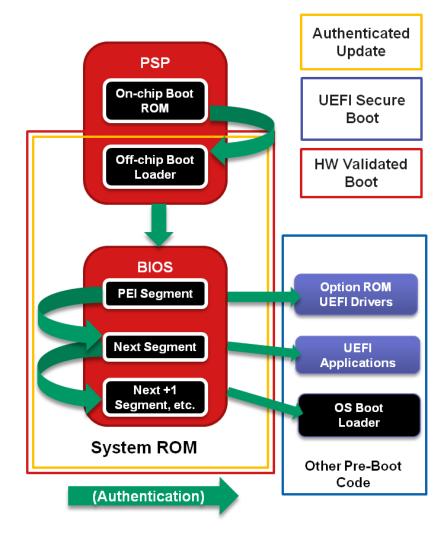

Hardware Validated Boot is an AMD specific form of secure boot, which roots the trust to hardware in an immutable PSP on-chip ROM firmware and validates the integrity of the system ROM firmware (BIOS).

Figure 1 shows the scope of hardware validated boot as it relates to the UEFI secure boot.

Figure 1. Hardware Validated Boot Overview

#### AMD Confide AMD Platform Security Processor BIOS

Architectural Design Guide

54267 Rev. 1.00 January 2014

The idea behind AMD Hardware Validated Boot is to build a trusted boot environment even before starting the x86 cores. In the Hardware Validated Boot mode, the PSP subsystem is the core root of trust for measurement.

During cold boot and under Hardware Validated Boot, the PSP runs its own firmware; all of the x86 cores are held in the reset state while PSP firmware performs basic initialization and authenticates the x86 reset code (i.e., the first block of BIOS). PSP firmware searches for this fraction of the BIOS image in the SPI flash area and validates its signature. After validating the BIOS signature, the PSP firmware configures the necessary hardware registers to release the x86 cores. The x86 cores, upon reset, start execution of the BIOS code authenticated by PSP firmware. The BIOS maintains this trust chain by first authenticating all firmware components before passing control to these firmware components. UEFI Specification 2.3.1, Chapter 27, provides further guideline for BIOS expected behavior. This document does not discuss those details and the BIOS writers are expected to follow those guidelines in addition to the ones listed later in this document.

On resume from sleep, PSP firmware restores the memory controller, validates resume vector and releases the x86 cores. Once released, the x86 cores fetch code straight from Dynamic Random Access Memory (DRAM) based on boot time BIOS configuration. Chapter 5, BIOS S3-Resume Path Handling, on page 36 covers details regarding the BIOS-PSP information exchange to make this execution flow possible.

#### 2.1.1 Integrated TPM Functions

The PSP software solution-stack offers firmware based TPM 2.0 services based on Microsoft whitepaper – "Trusted execution environment ACPI profile". BIOS writers are expected to follow the guidelines and provide BIOS support as outlined in the Microsoft whitepaper. BIOS must wait for memory to be available before sending firmware trusted platform module (fTPM) command to PSP.

The PSP subsystem does not have its own storage space to save the TPM data. Instead, it relies on BIOS to provide the storage services to PSP firmware. The PSP firmware uses BIOS system management mode (SMM) mailbox services to save PSP data in SPI space. The PSP firmware encrypts the data block and uses BIOS runtime SMM handler services to store or update this data to SPI flash storage. The BIOS is expected to (a) reserve part of SPI flash region for PSP data storage, (b) provide services to PSP firmware to store and update PSP data to this SPI region, and (c) protect this region of SPI flash from writing by unauthorized code (using the chipset-provided flash locking mechanisms and Secure Flash Update). PSP firmware is expected to manage any updated TPM data within its own local memory until BIOS makes those storage services available to PSP firmware; in other words, the BIOS storage services are not expected to be available during early boot and resume path and PSP firmware is expected to not rely on BIOS storage services during that time. Separately, BIOS can use the firmware TPM services for BIOS measurements as outlined in TCG specifications. In this usage model, the BIOS replaces the discrete-TPM PEI/DXE driver with a firmware-based-TPM PEI/DXE driver; and BIOS exposes the TPM

AMD Platform Security Processor BIOS Architectural Design Guide

protocol defined in "TCG EFI protocol" specification. Also BIOS is expected to use the TPM2.0 command-set to communicate with integrated Trusted Platform Module ( iTPM).

#### 2.1.2 Cryptographic Acceleration Support

The PSP solution-stack also offers hardware based cryptographic acceleration services such as support for SHA, AES, RSA, ECC, etc. BIOS makes use of PSP cryptographic acceleration for its own purposes such as validating the digital signature of other BIOS components, OS boot loader etc.

The CCP also provides a true RNG function, which may optionally be used to seed UEFI entropy. The mechanism for seeding UEFI entropy is described by Microsoft in the document entitled, "UEFI Entropy-gathering Protocol".

# Chapter 3 PSP Components

PSP components are described in the following subsections.

# **3.1 On-chip PSP Boot ROM**

PSP Boot ROM is an immutable part of the SOC and it embeds in it a SHA-256 hash of the public part of the AMD signing key, which forms the hardware core root of trust for the Hardware Validated Boot process. PSP microcontroller (A5) starts executing the On-chip Boot ROM code, in secure mode. It loads the off-chip PSP firmware into PSP static random access memory (SRAM) and after authenticating the PSP off-chip firmware it passes control to it.

# **3.2 Off-chip PSP Boot Loader**

When PSP on-chip Boot ROM transfers control to PSP off-chip Boot Loader, it communicates the pre-loaded PSP Directory table address in PSP SRAM, in mailbox area at a pre-defined address within PSP SRAM.

Once the PSP Boot Loader starts execution, it first determines if the system is booting from S5 or resuming from S3/S0i3 state by reading the sleep type and resume flag from FCH.

PSP Boot Loader performs the following sequence of operations as part of the S5 boot:

- 1. Locates and Loads the Off-chip SMU FW into PSP SRAM; and verifies its signature using the AMD Signing RSA Public Key. If the signature verification passes, Loads the verified Off-chip SMU FW image into SMU SRAM and notifies the SMU Boot ROM code to transfer control to the SRAM FW.

- 2. Locates and Loads the BIOS Signing RSA Public Key token into PSP SRAM; and validates its signature using the AMD Signing RSA Public Key.

- a. If the signature validation fails then it writes an error code to the TDR register and enters an infinite loop.

- b. If the signature validation passes, then proceeds to step 3.

- 3. Locates and Loads the BIOS RTM FW and signature block, into PSP SRAM; and validates its signature using the BIOS Signing RSA Public Key. The BIOS RTM FW signature is computed over the BIOS RTM FW code concatenated with PSP Directory Table.

- a. If the signature validation fails then it writes an error code to the TDR register and enters an infinite loop.

- b. If the signature validation passes, then proceeds to step 4.

- 4. Initializes the BIOS-PSP mailbox interface

- 5. Releases the CPU BSP core to begin execution. At this point the CPU microcode starts executing the BIOS RTM code from a fixed CPU reset vector 0xFFFF\_FF0.

PSP Boot Loader performs the following sequence of operations as part of the S3/S0i3 resume:

- Locates and Loads the S3 Restore Buffer generated by the platform BIOS and saved to SPI-ROM by the PSP Secure OS during S5 boot sequence into PSP SRAM; and validates its HMAC using the HMAC key.

- a. If the HMAC validation fails then it writes an error code to the TDR register and enters an infinite loop.

- b. If the HMAC validation passes, then proceeds to step 2.

- 2. Processes the S3 restore buffer and restore pre self-refresh data to the memory interface, reprograms memory interface, executes the programming sequence to take the DRAM out of self-refresh and writes the S3 restore post self-refresh data to the memory interface.

- 3. Releases the CPU BSP core to resume execution. At this point the CPU BSP core starts executing the BIOS Resume code located in SMM memory and pointed to by CPU S3-resume vector.

- 4. Determines if the system is resuming from S3 or S0i3 state

- 5. Derives the PSP SRAM Content Encryption Key

- Decrypts the PSP SRAM content (saved during S3/S0i3-suspend) from DRAM into PSP SRAM

- 7. Validates the HMAC of the loaded data using the HMAC key

- a. If the HMAC validation fails then it writes an error code to the TDR register and enters an infinite loop.

- b. If the HMAC validation passes, then it transfers control to the restored PSP Secure OS resume entry point.

# 3.3 Off-chip PSP Secure OS

When off-chip PSP Boot Loader transfers control to PSP Secure Operating System (OS), it communicates certain state information such as the Sleep (Sx) state, fTPM state and S3 Restore Buffer in a mailbox area at a pre-defined address with in PSP SRAM.

Once the PSP Secure OS starts execution, it first determines if the system is booting from S5 or resuming from S3/S0i3 state by reading the Sx state variable in the SRAM mailbox address.

PSP Secure OS performs the following sequence of operations as part of the S5 boot :

- 1. Performs the necessary initialization of OS internal structures and instantiates the TPM 2.0 compliant fTPM as a trusted application

- 2. Sets-up CPU-PSP interface registers' access control policy and interrupt mechanism

- 3. Re-initializes BIOS-PSP mailbox interface

- 4. Waits for BIOS SMM environment to be set up and BIOS to notify the SMM space reserved for PSP and parameters needed for PSP to generate SMI

- 5. Generates an HMAC over the S3 Restore Buffer content in SRAM using an HMAC key and stores S3 Restore Buffer contents appended with the HMAC to SPI-ROM by placing the payload in SMM space and generating an SMI interrupt to BIOS

- 6. Enters steady-state idling and waiting for commands from host interfaces

In steady state, when the system begins to enter S3/S0i3-state, as shown in Figure 3, on page 27 and Figure 4, on page 30, PSP Secure OS is notified. Upon receiving this notification, PSP Secure OS prepares to enter the S3/S0i3 state.

# Chapter 4 Overview of BIOS Support for PSP

### 4.1 SPI Flash Region Layout

The SPI flash storage is shared by both x86 BIOS binary and PSP firmware; i.e., BIOS code and data as well as PSP firmware code and data coexist in the same storage space. PSP firmware (onchip and off-chip) parses the SPI flash for various components in order to locate, authenticate and execute PSP binaries. A PSP directory table is needed to aid PSP firmware in finding various components in the SPI storage. This PSP directory is a simple table of various entries. Each of these entries provides information about various firmware components in the SPI flash area such as their type, size and location. The PSP directory can be anywhere in the SPI storage.

#### 4.1.1 **PSP Directory Table**

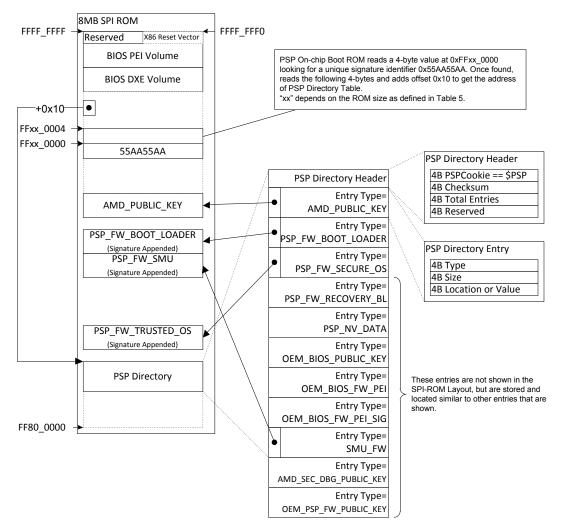

Figure 2 on page 20 describes the layout of the PSP Directory Table in SPI-ROM and how it is used to locate various PSP related public key tokens, firmware images and corresponding signatures.

#### Figure 2. PSP Directory Table

Table 2 describes the Embedded Firmware Signature (0x55AA55AA) locations for different ROM sizes:

**Table 2. Embedded Firmware Signature Target Locations**

| ROM Size | Address PSP Boot ROM checks (i.e. 0xFFxx_0000) |

|----------|------------------------------------------------|

| 512 KB   | 0xFFFA_0000                                    |

| 1 MB     | 0xFFF2_0000                                    |

| 2 MB     | 0xFFE2_0000                                    |

| 4 MB     | 0xFFC2_0000                                    |

| 8 MB     | 0xFF82_0000                                    |

| 16 MB    | 0xFF02_0000                                    |

#### AMD Platform Security Processor BIOS Architectural Design Guide

PSP Boot ROM does not have ROM size information and as such it sequentially reads all of the listed address from 0xFFFA\_000 to 0xFF02\_0000 until it finds the signature 0x55AA55AA.

Table 3 describes the fields of PSP Directory Table header structure:

| Field Name    | Offset<br>(Hex) | Size (in Bytes) | Description/Purpose                                                                                                                                      |

|---------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSP Cookie    | 0x00            | 4               | PSP cookie "\$PSP" to recognize the header                                                                                                               |

| Checksum      | 0x04            | 4               | 32 bit CRC value of the header items<br>below this field and the including all<br>entries. Fletcher's checksum algorithm is<br>used for CRC calculation. |

| Total Entries | 0x08            | 4               | Number of PSP Directory Table Entries in the table                                                                                                       |

| Reserved      | 0x12            | 4               | Reserved – Set to zero                                                                                                                                   |

Table 3. PSP Directory Table Header Structure

Table 4 describes the fields of PSP Directory Table Entry structure:

Table 4. PSP Directory Table Entry Fields

| Field Name                        | Offset<br>(Hex) | Size (in Bytes) | Description/Purpose                                                                                                                                                                        |

|-----------------------------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                              | 0x00            | 4               | Type of PSP entry                                                                                                                                                                          |

| Size                              | 0x04            | 4               | Size of the PSP entry in bytes                                                                                                                                                             |

| Union of { Location<br>or Value } | 0x08            | 8               | Depending on the Entry Type<br>Location: Address/Offset of SPI-ROM<br>location where the data for the<br>corresponding PSP Entry is located<br>OR<br>Value: 64-bit value for the PSP Entry |

#### **Table 5. PSP Directory Entry Type Encodings**

| PSP Entry Type | Description/Purpose                       |

|----------------|-------------------------------------------|

| 0x00           | AMD public Key                            |

| 0x01           | PSP Boot Loader firmware                  |

| 0x02           | PSP Secure OS firmware                    |

| 0x03           | PSP Recovery Boot Loader                  |

| 0x04           | PSP Non Volatile data                     |

| 0x05           | (OEM) BIOS public key signed with AMD key |

| 0x06           | BIOS RTM Volume                           |

54267 Rev. 1.00 January 2014

| PSP Entry Type | Description/Purpose                                                                                          |  |

|----------------|--------------------------------------------------------------------------------------------------------------|--|

| 0x07           | BIOS RTM volume Signature using OEM private key                                                              |  |

| 0x08           | SMU offchip firmware                                                                                         |  |

| 0x09           | AMD Secure Debug Key                                                                                         |  |

| 0x0A           | (OEM) PSP Secure OS public key signed with AMD key                                                           |  |

| 0x0B           | PSP Soft Fuse Chain<br>(VALUE = 0, Secure part can't be unlocked, Value<br>= 1, Secure part can be unlocked) |  |

| 0x0C           | PSP boot-loaded trustlet binaries                                                                            |  |

| 0x0D           | Trustlet public key signed with AMD key                                                                      |  |

| 0x0E-0x5E      | Reserved for AMD use                                                                                         |  |

| 0x5F           | Software Configuration Settings Data Block                                                                   |  |

| 0x60-0x7F      | Reserved for AMD use                                                                                         |  |

| 0x80-0xFF      | Reserved for OEM use                                                                                         |  |

#### Table 5. PSP Directory Entry Type Encodings (Continued)

*Note:* The First four entries of PspDirectory MUST be in the following order:

First entry- AMD Public Key (Type 0x00) Second entry- PSP Boot Loader firmware (Type 0x01) Third entry- SMU Firmware (Type 0x08) Fourth entry- PSP Recovery Firmware (Type 0x03)

When PSPType Enum is of type Soft Fuse Chain (i.e. type 0x0B) the Size tag is set to 8-bytes and the next 64bit field Location/Value is used to represent the soft fuse value itself.

The following table defines the PSP Soft Fuse Chain 1:

#### Table 6. PSP Soft Fuse Chain 1

| Bit Number | Purpose                                                   |

|------------|-----------------------------------------------------------|

| 0          | PSP Secure Debug Control Flag<br>1- Enabled, 0 – Disabled |

| 163        | Reserved for AMD Use                                      |

#### Table 7. PSP Soft Fuse Chain Bit Assignment

| Bit Index | Description/Purpose                                   |  |

|-----------|-------------------------------------------------------|--|

| 0         | PSP Secure Debug Control Flag (0-Disabled, 1-Enabled) |  |

| 163       | Reserved                                              |  |

AMDZ

#### 4.1.2 Crisis Recovery Path with PSP Enabled

BIOS already has an existing, mature recovery scheme in case of a flash update failure during a non-secure boot sequence (PSP disabled). The primary focus here is to handle the case where PSP is enabled. The off-chip PSP boot loader will run prior to releasing the X86 cores, and the PSP secure OS/Trustlet will run in parallel with X86 codes.

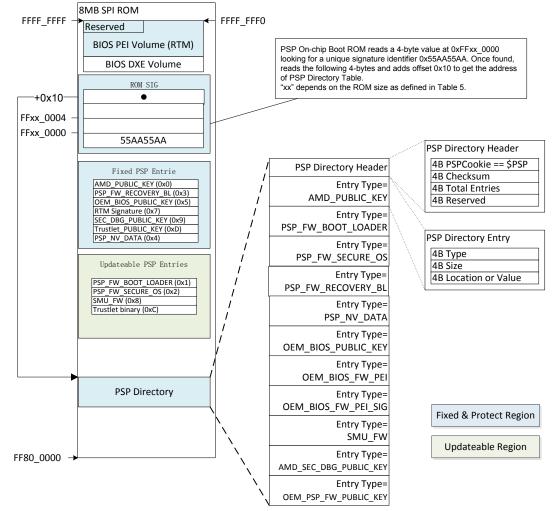

The recommendation is to separate the PSP SPI ROM into 2 categories, accompanied by BIOS and PSP FW changes.

Recommended SPI ROM Organization:

- 1. Fixed/Protected Region The contents in this region are unchanged and not updatable during flash update, it is protected by the IBV or OEM flash tool.

- 2. Updateable Region This area can be updated by new releases containing bug fixes, enhancements, and new feature enablement code.

If the following data areas in the SPI flash are corrupted, the result will be permanent boot failure, and the recovery mechanism will fail – ROMSIG (Embedded Firmware Signature), PSP Directory Table Header, PSP Directory Table Entries. Details for each of these items follow:

- ROMSIG should not be changed during flash update as the damage will result in the PSP onchip FW not being able to locate the PSP Directory header, and the whole system will hang with the X86 cores held in reset.

- The PSP Directory Table Header should not be changed during flash update as the corruption will lead to a checksum failure and the PSP OROM will stall the system.

- The items pointed to by some of the PSP entries region should preserve a maximum size for further Update.

- Directory Table Entries may be updated, and others should remain fixed. Table 8 on page 24 shows the type for each entry. Target items marked as "Fixed" should be kept in the protected region that is not updated during flash update, as this is the base of the PSP recovery mechanism, and the corruption of those binaries will lead unexpected behavior

54267 Rev. 1.00 January 2014

| Type ID (Hex) | Name                                                  | SPI ROM property |

|---------------|-------------------------------------------------------|------------------|

| 00            | AMD public Key                                        | Fixed            |

| 01            | PSP Boot Loader firmware                              | Updateable       |

| 02            | PSP Secure OS firmware                                | Updateable       |

| 03            | PSP Recovery Boot Loader                              | Fixed            |

| 04            | PSP Non Volatile data                                 | Fixed            |

| 05            | (OEM) BIOS public key signed with<br>AMD key          | Fixed            |

| 06            | BIOS RTM Volume                                       | Fixed            |

| 07            | BIOS RTM volume signature using OEM private key       | Fixed            |

| 08            | SMU offchip firmware                                  | Updateable       |

| 09            | AMD Secure Debug Key                                  | Fixed            |

| 0A            | (OEM) PSP Secure OS public key signed<br>with AMD key | Fixed            |

| 0C            | PSP boot-loaded trustlet binaries                     | Updateable       |

| 0D            | Trustlet public key signed with AMD key               | Fixed            |

| 5F            | Software Configuration Settings Data<br>Block         | Updateable       |

#### Table 8. PSP Entry SPI ROM Property Assignment

Chapter 4

#### AMD Platform Security Processor BIOS Architectural Design Guide

#### Figure 3 Overall SPI ROM layout (Recovery Supported Design)

The crisis-recovery flow for a non-secure system must be updated accordingly for a system with PSP enabled. (See also the "PSP Components" section, which covers details beyond crisis recovery.)

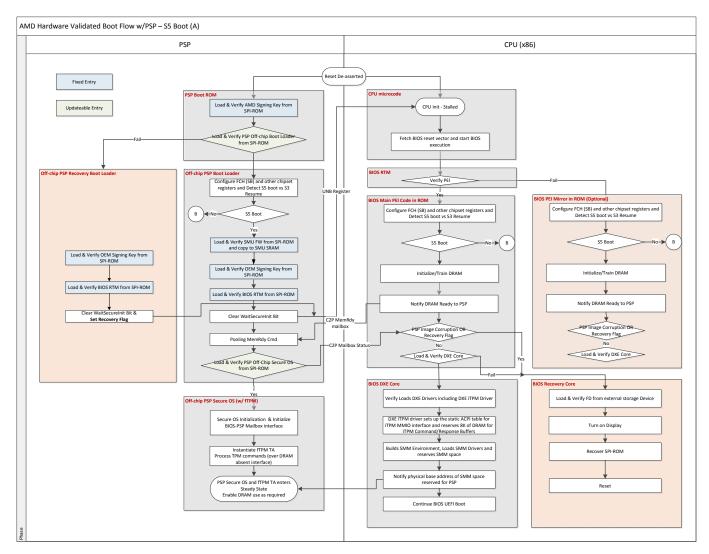

- When the system reset signal is de-asserted, the X86 cores will be held in reset, and the PSP on-chip boot ROM will start execution. After loading and authenticating the AMD Public key, the PSP on-chip boot ROM will load and validate the PSP off-chip boot loader.

- If verification fails, the recovery process is initiated and the PSP recovery off-chip boot loader will be loaded instead. The Recovery PSP Boot Loader verifies the BIOS PEI (not updatable), set a status bit to indicate recovery process required and releases x86.

- If verification succeeds, the PSP off-chip boot loader will authenticate the SMU FW. If SMU FW authentication fails, PSP off-chip Boot Loader, skips loading SMU FW, verifies the BIOS PEI (not updatable), set a status bit to indicate recovery process is required and releases x86. Given that the BIOS RTM and RTM signature are in the fixed region and not

####

#### AMD Platform Security Processor BIOS Architectural Design Guide

updated during flash update, it is assumed that the authentication of BIOS RTM will always be successful in normal as well as recovery boot paths.

- The PSP off-chip Recovery boot loader does not load the SMU FW.

- Considering that the SMU firmware may not loaded in the recovery path, BIOS boot code must check whether the SMU firmware is loaded before issuing any messages to the SMU. In other words, the BIOS modules that are executed during the recovery path (including: AGESA PEI module, Platform PEI module, Recovery module, VBIOS) should not depend on the services provided by SMU FW.

- The PSP BIOS PEI module sends the DRAM ready message to the PSP FW once DRAM has been initialized. PSP FW will return the recovery status bit along with other status bits indications. The PSP PEI module publishes this information through PPI/HOB. The platform BIOS recovery path should locate and check this PPI/HOB to retrieve PSP FW integrity status along with DXE FV integrity. If the PPI/HOB shows problems with the status of either of these items, the BIOS should run in the recovery path.

- The secure flash mechanism should be followed in the recovery path as well as the normal BIOS update path. This means the new BIOS image must be authenticated before the update and the fixed SPI region as mentioned above must remain protected

Figure 3 on page 27 illustrates the details of the crisis recovery flow with PSP; zoom in to make it more legible.

AMD Platform Security Processor BIOS Architectural Design Guide

Figure 3. Crisis Recovery Flow With PSP

# 4.2 Signing of BIOS Component- OEM Signing Key, PEI Volume

The OEM must sign the BIOS RTM volume using the private portion of secure RSA key. This key that is used to sign the BIOS RTM volume is referred here as OEM signing key. OEM keeps the private portion of the OEM signing key in secure place (HSM, etc.) and submits the public portion of OEM key to AMD. AMD will perform one time signing of public portion of OEM signing key. This process enables PSP firmware to authenticate OEM public key.

On secure PSP parts, the PSP firmware authenticates the BIOS image in two steps before releasing x86 core. PSP firmware first parses PSP directory to locate the signed OEM public key and authenticates the OEM public key that was signed with AMD signing key. Next, after the public portion of OEM signing key is authenticated, the PSP firmware uses the OEM public key to further authenticate the BIOS RTM volume that was signed by OEM secure private key. PSP encrypts the hash with the OEM public key and then compares the resulting hash with the hash in the signature.

If the signature matches, the BIOS is considered trusted and x86 cores are released.

One note about the signed BIOS RTM volume- The signed BIOS blob is generated by first concatenating BIOS RTM volume with PSP directory blob and signing this combined blob using private portion of OEM key. Integrity of both PSP directory and RTM volume integrity can now be checked together when PSP firmware authenticates this blob. Note, this combined blob must be signed with the BIOS Signing RSA Private Key using the RSASSA-PSS signing scheme used as signature scheme with SHA-256 used as the hashing algorithm for both message and mask generation. The resulting signature data is stored in the PSP directory entry as the entry type 0x07. The size of the signature data will be 256-byte for 2048-bits key or 512-byte for 4K key.4096-bits key.

This two-step authentication removes unnecessary dependence on AMD signing server or build processes where BIOS is built on regular basis by IBV/OEM. AMD signing server will sign the public portion of OEM signing key once at the beginning of project and is separate from the BIOS build process; during the normal BIOS build process the private portion of OEM signing key will be used to sign BIOS RTM volume as part of OEM build process without any AMD signing server involvement. The BIOS image includes the AMD public key as well as signed public OEM signing key in the PSP image that was generated at the beginning of the project. This allows the OEM to use internal signing processes without external dependency.

After the PSP firmware releases x86 core for execution, the BIOS is expected to maintain the chain of trust to authenticate next set of bios code before executing it. It is left to OEM/IBV to choose appropriate BIOS implementation to insure the trust chain. At x86 core release the RTM volume has been authenticated by PSP firmware. BIOS RTM volume must authenticate the next volume before handling of the control. If only the SEC code is the BIOS RTM volume, then SEC code must authenticate PEI volume before handling off control to PEI core. If BIOS RTM volume

AMD Platform Security Processor BIOS Architectural Design Guide

is entire PEI volume it must authenticate DXE volume. The DXE IPL code in BIOS PEI volume needs to further authenticate DXE volume before handing off control to DXE code.

There are various possible methods to authenticate each of BIOS drivers in DXE volume. In one possible method the DXE IPL driver in PEI volume validates the entire DXE volume before handing off control to DXE core. In such implementation the DXE volume can be signed and the static public key used for signing of DXE volume can be saved in PEI volume itself. This digital signature of DXE volume signature can be saved anywhere in SPI space with some provisions for DXE IPL driver to locate this key during cold boot. During cold boot the DXE IPL code in PEI volume will use this public key and validate DXE volume against the digital certificate of DXE volume saved in the SPI space and if the digital certificate is authentic the DXE IPL handoff control to DXE code.

Another option may be simply to save the SHA1/2 digest of DXE volume in PEI volume and during cold boot compare the DXE volume against the digest in PEI volume. If the digest matches the DXE volume is considered trusted. To implement such process the BIOS build process can compute the DXE digest and append the digest after PEI volume. The OEM signing key will sign the concatenated blob of PEI volume + DXE digest + PSP directory and this signature will be reflected in PSP directory for BIOS RTM entry. In this implementation PSP firmware will authenticate PEI volume as well as DXE digest. Later during cold boot DXE IPL driver can use this digest to authenticate DXE volume as well. Any tampering of DXE digest in SPI area can be detected by PSP since DXE digest is part of signed BIOS RTM.

AMD will provide the signed OEM public key and AMD public key. The format of AMD signing key and OEM signing key is shown in Appendix E on page 71.

# 4.3 **BIOS Build Process**

The SPI image includes BIOS components as well as PSP components. In the below process BIOS PEI volume is considered BIOS RTM volume.

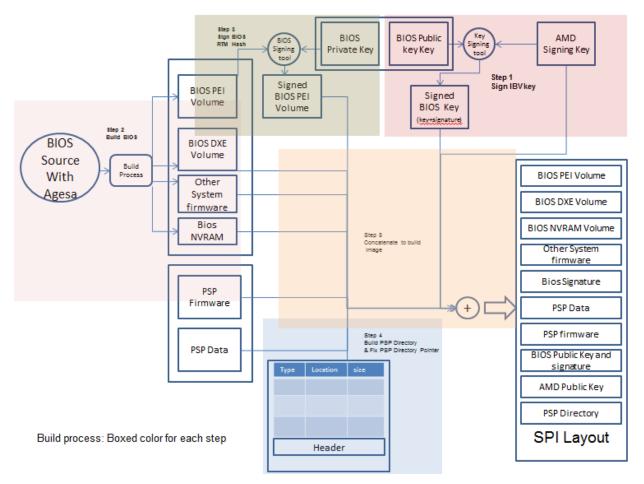

To support hardware validated boot the BIOS PEI FV needs to be signed and PSP directory needs to be present to provide information regarding various signed entities. Figure 4 on page 30 summarizes the above discussion to illustrate how various entities listed above can be combined to build the final SPI image.

AMD Platform Security Processor BIOS

54267 Rev. 1.00 January 2014

Architectural Design Guide

#### **Figure 4. Final SPI Image**

- As shown above, the first step is generation of the digital signature of public portion of OEM signing key. This may happen just once before the start of project. The OEM/IBV submits the public key portion of their OEM signing key to AMD. AMD signs this key using the AMD RSA key and passes back it to IBV/OEM. The AMD public key and the signed OEM public key should be part of final BIOS SPI image. Next, the BIOS source code is compiled and various BIOS components (PEI Volume, DXE volume, NVRAM storage, EC binary, etc.) are built as usual.

- As part of build process, DXE volume hash is generated and this hash is saved within BIOS PEI volume. This is required as part of hardware validated boot sequence for PEI kernel code to authenticate DXE volume before passing control to DXE core and extend the trust chain.

- The PSP directory is built next. PSP directory table points to location of various firmware entities. The PSP directory holds the location information of following entries-

- AMD Public Key

- PSP firmware i.e., Boot loader, Secure OS, PSP Recovery OS

- AMD SMU firmware

AMD Platform Security Processor BIOS Architectural Design Guide

- PSP NVRAM data

- OEM Signing Key signed with AMD signature

- BIOS PEI Volume signature (signed Private portion of OEM signing key)

- BIOS PEI Volume

- BIOS binaries, PSP directory and various firmware binaries are combined to build the SPI BIOS image.

- Finally, the OEM signing server builds the signed BIOS RTM signature based on blob of BIOS PEI volume concatenated with PSP Directory, and generates the digital signature of this using private portion of OEM signing key. The SPI location for signed BIOS RTM code is finally updated with this signature blob.

After the above steps the final SPI BIOS image will be ready.

# 4.3.1 Hardware validated Boot BIOS development bypass mechanism (Mullins Only)

Some IBVs have neither key management nor signing infrastructure. They have no way to securely generate and handle the OEM Signing Key. Thus, they have no way to sign their BIOS for the continuation of the secure boot mechanism. During bring-up and product development, the IBVs rev BIOS versions very quickly. Manually signing the BIOS block for them works initially but quickly becomes a drain on key AMD resources. Automating the signing of the BIOS block requires resources to create and support the signing portal. Automated checking of the submitted block is infeasible which means that AMD could inadvertently sign malicious BIOS blocks. Instead of either of these solutions, a specifically crafted and AMD private key signed data blob will be created to terminate the Hardware validated boot chain. This blob can only be used during development by IBVs and OEM. The blob mechanism will be removed in production release, AMD does not authorize the use of BLOB-based HVB for field use with production platforms..

The blob interception point is in the PSP secure off-chip bootloader. The PSP bootloader checks whether the entity pointed to by the BiosRtmFirmware entry (Entry Type6) of the PSP Directory is at the reset vector. If not, the PSP firmware considers it a blob and does not concatenate the PSP Directory table to the entity for signature validation. The blob is validated against the RTM.

This means that the PSP directory is not validated in this boot flow since it is not concatenated with the blob before the blob is signed. Since we are purposefully placing the token in a location that does not match the reset vector and thereby breaking the secure boot chain, this does not have additional negative security impact.

## 4.4 **Runtime Execution Flow**

The high level description of execution flow is listed below.

#### 4.4.1 5.4.1 Pre x86 Initialization

At power on reset the following execution flow takes place. The Pre x86 code Init sequence defines the sequence of events by PSP firmware before the x86 core is released from reset. Details on this flow are defined in PSP Software Architecture design document.

- 1. Under Hardware Validated Boot mode, the x86 cores are held in reset during the system Power-On sequence while the PSP begins executing code.

- 2. The PSP runs its on-chip firmware at reset; this code is an immutable part of the Silicon.

- 3. The PSP on-chip firmware scans for the PSP off-chip code in the SPI space. PSP on-chip firmware first scans SPI space for Firmware Location signature (0x55AA55AA); this signature is scanned at specific SPI locations as defined in FCH porting guide. Offset 0x10 of this structure points to location of PSP directory.

- 4. The PSP on-chip firmware scans the PSP directory to find the AMD public key, the PSP firmware and the PSP data in the SPI ROM; PSP on-chip code next loads these binaries into PSP's secure memory. After authenticating these binaries the PSP on-chip firmware passes control to the PSP off-chip firmware.

- 5. The PSP off-chip firmware uses the PSP Directory to find the signed OEM key, the BIOS RTM signature, and the BIOS RTM code.

- 6. PSP off-chip firmware authenticates the BIOS in a three-step process

- PSP on-chip code authenticates the AMD public key by comparing this digest of the key value against the value saved in immutable ROM.

- PSP off-chip code authenticates the OEM public key by using AMD public key.

- After the signature of the OEM public key is validated, PSP firmware uses the OEM public key to authenticate BIOS PEI (RTM) Volume and PSP directory (signed RTM blob build with PEI volume concatenated with PSP Directory).

- 7. After authenticating the BIOS PEI volume, the PSP firmware writes to a hardware register to release the x86 cores.

- 8. PSP boot loader continues to load PSP secure OS from SPI to secure SRAM in parallel to x86 BIOS code execution. X86 BIOS must ensure the SPI region decode range remain valid. If the SPI decode range is changed by BIOS SEC or other code than it will also affect the PSP subsystem that is attempting to read from SPI space.

#### 4.4.2 BIOS Boot x86 Initialization

After the x86 cores are released from reset, the BIOS boot phase starts and performs the following steps:

- 1. The CPU fetches the BIOS reset vector from SPI flash ROM at memory address 0xFFFFFF0 and BIOS SEC execution starts.

- 2. The BIOS SEC code loads and executes rest of PEI driver in PEI (RTM)volume that has already been authenticated by PSP firmware.

- 3. If the platform wishes to use a TPM, the platform may use firmware TPM services offered by PSP or it may use discrete TPM, but not both; the correct BIOS TPM drivers need to be present to perform necessary TPM operation. PSP firmware offers TPM 2.0 support as outlined in Microsoft specification. BIOS must wait for memory to be available before sending any command to PSP.

- 4. Once memory is initialized the BIOS sends mailbox command "MboxBiosCmdDramInfo" to PSP to inform availability of memory. PSP firmware can now use memory for its own use.

- 5. At the end of PEI stage the PEI kernel must authenticate DXE volume before handing off control to DXE IPL. As part of the build process, the digest of DXE volume is saved within PEI volume. PEI core computes the digest of DXE volume and compares it against saved digest in PEI volume. If the digest matches, the DXE IPL is considered trusted and PEI kernel code continues to load the DXE driver.

- 6. At this point the BIOS boot process moves to the DXE phase.

- 7. The DXE core authenticates various DXE driver modules, such as Option ROMs, third party DXE drivers, etc. that are not part of the SPI flash (i.e. not part of DXE volume). The authentication steps follow secure boot flow as outlined in UEFI specification.

- 8. If the BIOS is using integrated TPM, then the iTPM drivers are loaded to perform measurements of other DXE components. The iTPM DXE driver allocates necessary memory space for TPM request/response buffer and builds the TPM2 Static ACPI table as outlined in the Microsoft whitepaper on "Trusted Execution Environment ACPI Profile". In addition it extends necessary protocol outlined in TCG specification to aid BIOS to perform measurement and other TPM use. A platform should only include discrete or integrated TPM and not both. The only exception is AMD reference board where both kind of TPM are present on board for validation purposes only. In such validation boards BIOS need to support both kind of TPM driver and provide setup option (default to internal TPM) for test user to select discrete vs. internal TPM device for test.

- 9. Next the SMM environment is built and SMM drivers are loaded. The SMM drivers are needed to handle PSP firmware storage request. PspP2Cmbox SMM driver: This driver handles SMI requests coming from PSP firmware and also provides information to PSP FW of how to trigger specific SMI to BIOS. The Fake SMI has been selected as the SMI source. Currently all the P2C mailbox commands are only used for providing the SPI ROM access to PSP FW. Once the SMM driver handler receives the request from PSP FW, it will call

####

IBV/OEM customized storage library in the backend. Interface of the customized storage library is same as EFI\_FIRMWARE\_VOLUME\_BLOCK2\_PROTOCOL.

- a. The customized storage library operates on SPI space for PSP NVRAM and enables write/erase operation on that space. It also ensures NVRAM region is appropriately locked against unauthorized update on this SPI space. Note, this library is required to work in SMM mode, and should not depend on any boot available services.

- b. The PspP2Cmbox SMM driver will perform the following steps:

- 1. The driver allocates transfer buffer in SMRAM for PSP to pass the parameter.

- 2. The driver sends a mailbox command "MBoxBiosCmdSmmInfo" to the PSP firmware and informs the space reserved for PSP communicating as well as other relevant information for PSP to trigger SMI at runtime.

- 3. When PSP firmware triggers SMI for BIOS services, the callback handler checks the integrity of data that PSP firmware writes into SMM buffer and uses EFI\_FIRMWARE\_VOLUME\_BLOCK2\_PROTOCOL liked library to service PSP NVRAM access request.

- 10. Now PSP firmware can call the BIOS services to store TPM data.

- 11. A new PSP DXE/SMM driver is loaded to handle the resume path. This driver prepares the BIOS resume code (discussed in Chapter 5, BIOS S3-Resume Path Handling, on page 36) in memory and sends a mailbox command to inform the PSP firmware about the location of the BIOS S3 resume vector. In addition it registers to service the SlpxSx SMM trap. (See Chapter 5 on page 36 for more details on S3 resume path).

- 12. The IBV Storage code needs to lock the PSP and other critical regions of the SPI flash. The SPI region must be locked before running any Option ROMs or other non-System ROM code and only trusted SMM code should be able to unlock and update this region.

- 13. PSP DXE driver will register a callback on ReadyToBoot event to perform the tasks right before handling control to OS boot loader. The details steps of the callback are:

- a. Initialize the RDRAND instruction related register

- b. Save the SMM resume vector and Core context to specific MSR (*Note, should be only called once during boot*)

- c. Send MboxBiosCmdBootDone C2P mailbox command to PSP FW

- 14. The remaining DXE drivers are loaded and finally OS boot loader is loaded and after proper authentication BIOS hands off control to the OS boot loader.

#### 4.4.3 **BIOS Runtime Functionality**

The high-level execution flow during runtime is listed below.

- 1. After BIOS hands off control to the OS boot loader, the OS boot loader loads the operating system (e.g. Windows 8).

- 2. The OS takes control and loads rest of the OS drivers.

- 3. The OS references the iTPM ACPI table and loads iTPM OS driver to offer TPM support.

- 4. The OS uses the TPM software stack and sends TPM commands that are handled by PSP firmware. The PSP firmware services any OS requests for TPM commands.

- 5. If the PSP firmware needs to perform a write to SPI storage, it performs the following additional steps:

- a. PSP firmware copies necessary data as well as command parameters into SMM space reserved for PSP-BIOS communication.

- b. PSP firmware triggers SMI for BIOS to service the request. BIOS SMM entry code invokes all registered SMM handlers. In this case, the P2CMbox SMM Handler gets control and checks if the PSP firmware generated the SMM.

- c. The P2CMbox SMM callback handler locates and invokes the EFI\_FIRMWARE\_VOLUME\_BLOCK2\_PROTOCOL liked library to write the data into SPI.

- d. Finally, the P2CMbox SMM driver reports the appropriate status to the PSP firmware and resumes out of SMM mode.

- 6. The PSP firmware returns the appropriate status and data values to the operating system.